在电子设备的散热设计中,热阻(Thermal Resistance)是一个至关重要的物理量,它定量描述了材料或系统对热量传递的阻碍能力。从本质上看,热阻是热传递路径上的“阻力标尺”,其作用可类比于电路中的电阻——电阻限制电流,热阻则限制热流。

定义与公式:

热阻定义为物体两端温度差(ΔT,单位:℃或K)与通过它的热功率(P,单位:瓦特,W)的比值,数学表达式为:Rθ = ΔT / P。热阻越大表示热越不容易传导,因此物体温度就会越高。

这一公式揭示了热阻的核心意义:单位热功率下产生的温差。例如,若某散热器的热阻为0.5℃/W,当芯片功耗为10W时,散热器两端温差将达5℃。

一、热阻参数解析

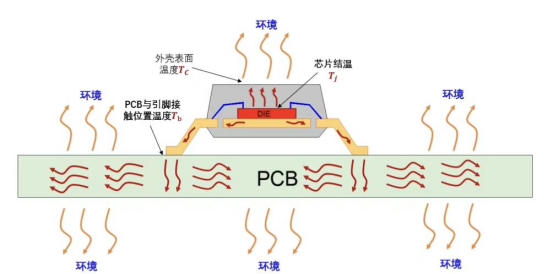

常见热阻参数包括:结到外壳的热阻(RθJC),结到环境热阻(RθJA),结到板热阻(RθJB),外壳到散热器热阻(RθCS),结到顶部热阻(RθJT)。

图1:芯片热阻模型示意图

结到外壳的热阻

RθJC, Junction-to-Case Thermal Resistance

定义:芯片内部发热结(Junction)与封装外壳(Case)之间的热阻,反映封装内部的导热能力。

计算公式:RθJC = (Tj-Tc)/PH

测试条件:通常在标准冷却条件(如强制风冷)下测量,外壳需与散热器紧密接触。

影响因素:基板材料(陶瓷/塑料/金属)、TIM(导热界面材料)性能、芯片与基板的连接工艺(如焊线、倒装焊)。

典型值:陶瓷封装(如QFN)可能低至1-5℃/W,塑料封装(如LQFP)可能高达10-30℃/W。

结到环境热阻

RθJA, Junction-to-Ambient Thermal Resistance

定义:芯片结到周围环境的总热阻,综合反映封装、PCB、散热器及空气对流的散热能力。

计算公式:RθJA=(Tj-TA) /PH

测试条件:分为自然对流(RθJA-NA)和强制风冷(RθJA-FA),结果差异显著。

影响因素:PCB铜箔面积、散热孔设计、空气流动速度、封装高度(如BGA比QFN更易散热)。

典型值:小封装(如SOT-23)可能高达200-500℃/W,大功率封装(如TO-220)可能低至10-30℃/W。

结到板热阻

RθJB, Junction-to-Board Thermal Resistance

定义:芯片结到PCB板(Board)的热阻,反映热量通过封装底部传导至PCB的能力。

计算公式:RθJB=(Tj-TB )/PH

测试条件:芯片底部与PCB紧密接触,测量点位于PCB下方特定距离(如1mm或2mm)。

影响因素:封装底部金属层厚度、PCB铜箔面积和层数、焊盘设计。

典型值:带散热焊盘的QFN封装可能低至10-20℃/W,无焊盘的SOP封装可能高达50℃/W以上。

应用场景:优化PCB散热设计,尤其适用于无散热器的密闭空间设备。

外壳到散热器热阻

RθCS, Case-to-Sink Thermal Resistance

定义:封装外壳与散热器之间的热阻,反映接触界面的导热效率。

计算公式:RθCS=(TC-TCS )/PH

影响因素:接触压力、导热膏/垫的材质与厚度、表面粗糙度。

典型值:优质导热膏(如硅脂)可将RθCS降至0.1-0.5℃/W,而空气间隙可能导致RθCS超过1℃/W。

应用场景:指导散热器安装工艺,避免因接触不良导致散热失效。

结到顶部热阻

RθJT, Junction-to-Top Thermal Resistance

定义:芯片结到封装顶部的热阻,反映热量通过封装顶部散出的效率。

计算公式:RθJT=(Tj-Tt)/PH

应用场景:适用于顶部散热设计(如加装散热片或风扇),常见于高功率LED或功率模块。

典型值:金属顶盖封装(如TO-247)可能低至5-10℃/W,塑料封装可能高达50℃/W以上。

其中:

Tj:结温;

TA:环境温度;

TB:PCB板温度;

TC:外壳温度;

TCS:散热器温度;

Tt:封装顶部温度;

PH:总功耗。

二、案例分析

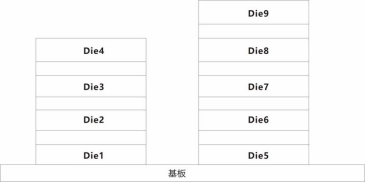

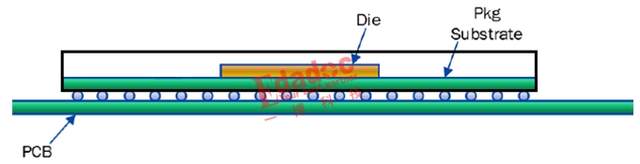

我们以公司的一个产品设计和热仿真结果作为真实案例,做一个热阻分析。这款DDR4芯片采用9片die堆叠设计,采用两半(4个die和5个die)进行堆叠。

图2:DDR4芯片封装示意图

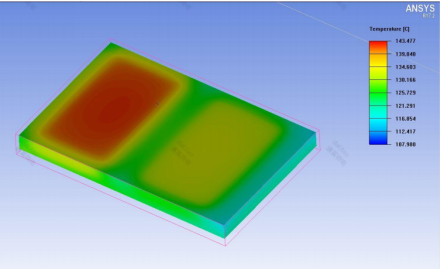

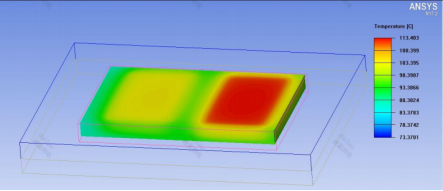

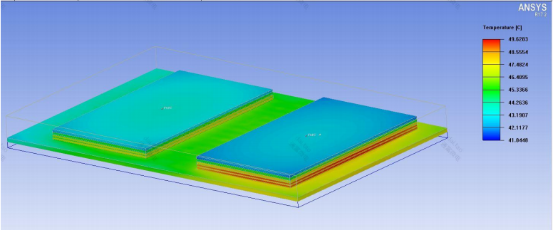

下图是多芯片堆叠的热仿真结果。本次仿真采用Ansys Icepak进行模拟,旨在评估BGA321封装在不同热路径下的热阻性能。仿真条件如下:环境温度25℃,功率6.75W,PCB类型2s2p,散热方式为自然对流。

图3:RθJA

在JA环境中,最高温在5个芯片堆叠的芯片上表面,环境温度为25℃,功耗为6.75W,计算可得热阻JA为17.55℃/W。RθJA反映了芯片到环境空气的整体散热能力,在自然对流条件下RθJA的典型值为20~100℃/W。该芯片RθJA小于典型值,说明热量更容易散热到环境当中,芯片有很好的环境散热性能。

图4:RθJB

在JB环境中,最高温在5个芯片堆叠的芯片上表面,环境温度为25℃,功耗为6.75W,计算得热阻JB为11.61℃/W。RθJB表示芯片通过封装底部向PCB传递热量的能力,在自然对流条件下,RθJB典型值为5~20℃/W。该芯片RθJB在在典型值范围内,说明芯片通过PCB板散热的能力较好,即芯片热量向电路板传递的效率更高,可以适用于高功率场景。

图5:RθJC

在JC环境中,最高温在5个芯片堆叠的芯片底面,环境温度为25℃,功耗为6.75W,计算得热阻JC为3.65℃/W。RθJC是芯片到封装外壳的热阻,在自然对流条件下,RθJC典型值为1~10℃/W。该芯片RθJC在典型范围内,说明芯片通过封装外壳散热的性能较好,封装导热性好,便于安装散热器和导热垫。

三、热性能优化建议

如需进一步降低结温,优化散热路径,下列方法可供参考:

通过改进PCB设计,例如使用高导热材料或者增加散热层。也可以通过提高PCB覆铜率来提高PCB面热导率,如提高覆铜率至80%,PCB面内热导率可以提升至150W/m*K,预计可以降温6℃~8℃。

优化塑封料:随着塑封料热导率的增加,DDR 模组的最高温度会逐渐降低。当前塑封料热导率较低,为1W/m*K,根据傅里叶热传导定律,计算出当前塑封料热阻为4.8℃/W,占系统总热阻的27%。可以尝试将塑封料热导率提升至5W/m*K,预计结温可以降级5℃左右。

优化散热路径。当前RθJC为3.65℃/W,说明封装顶部是高效散热路径。可以添加顶部散热器,或者采用高导热界面材料,来进一步优化散热降低结温。

四、结论

在电子散热设计中,热阻是衡量芯片散热性能的核心指标,直接影响设备的可靠性与寿命。通过对 RθJA(结到环境)、RθJB(结到板)、RθJC(结到外壳)等关键参数的解析,我们可以精准评估芯片的散热路径效率,并针对性地优化设计。较低 RθJA 表明芯片整体散热性能优异,热量能高效传递至环境;较低 RθJB 反映 PCB 导热能力强,适合依赖电路板散热的场景;较低 RθJC 则说明封装内部导热路径高效,便于外接散热器提升散热能力。

通过优化 PCB 设计(如增加覆铜率、使用高导热材料)、改进封装工艺(如提升塑封料导热率)以及增强散热路径(如加装散热器),可显著降低芯片结温,确保其在高温、高负载下的稳定运行。精准的热阻分析与优化,是提升电子设备性能与可靠性的关键一步。

-

封装

+关注

关注

128文章

8845浏览量

145952 -

热阻

+关注

关注

1文章

115浏览量

16925 -

散热

+关注

关注

3文章

555浏览量

32586 -

DDR4

+关注

关注

12文章

335浏览量

41923

原文标题:解读DDR4堆叠模组的热仿真报告与散热优化

文章出处:【微信号:封装与高速技术前沿,微信公众号:封装与高速技术前沿】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

DDR4与DDR3的不同之处 DDR4设计与仿真案例

DDR4堆叠模组的热仿真案例分析

DDR4堆叠模组的热仿真案例分析

评论