µ‰–Յ˺∆”¶∏√≤ªª·≥ˆœ÷ ±–ÚŒ•¿˝°£∂ý bank …˺∆∏¸»ð“◊ Ð¥ÀŒ ”∞œÏ°£

∂‘”⁄∂ý bank Ω”ø⁄≈‰÷√£¨»Áπ˚µ•∏ˆ bank Õ¨ ±æþ”– RX ∫Õ TX£¨≤¢«“∆‰÷––Ú¡–ªØ“Ú◊”≤ªÕ¨£¨ªÚ’þ»Áπ˚‘⁄°∞Advanced°±—°œÓø®…œ π”√¡À enable_all_ports£¨‘Úø…ƒÐ∑¢…˙¥ÀŒ °£

‘⁄ 2021.1 ∞ʵƒ Advanced IO Wizard ÷–Œ™ PLL ÷π©¡Àæ≠π˝∏¸–¬µƒ»•Õ·–±µÁ¬∑£¨¥À∏¸–¬ø…Ω‚æˆ¥Û≤ø∑÷ ±–ÚŒ•¿˝°£

»Áπ˚»‘∑¢…˙Œ•¿˝£¨«Îøº¬« ÷∂ص˜’˚ ±÷”µƒ PHASE Ù–‘£¨÷±÷¡Ω‚戌•¿˝Œ™÷π°£

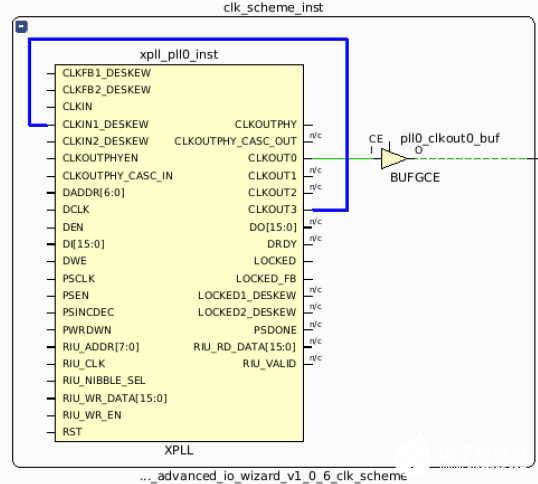

XPLL µƒ CLKIN_DESKEW ¡¨Ω”µΩ XPLL µƒ CLKOUT3£®XPLL Ω´…Ë÷√Œ™ π CLKOUT3 ∆µ¬ = CLKIN ∆µ¬ £©°£

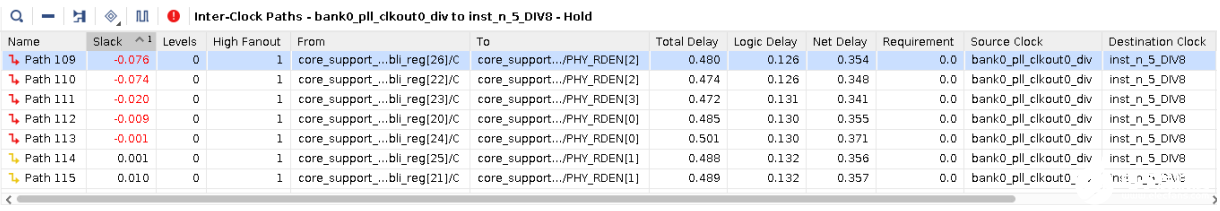

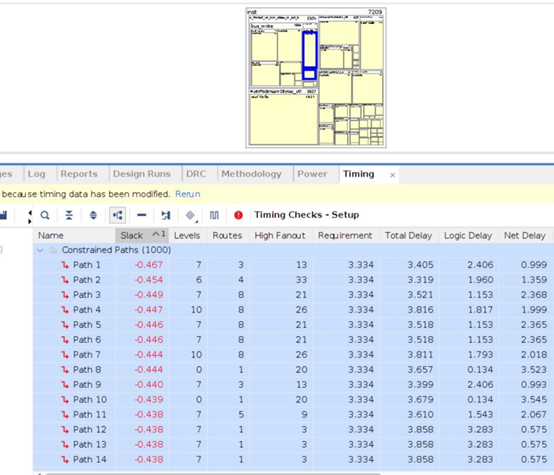

‘⁄“‘œ¬ æ¿˝÷–£¨µΩ PHY_RDEN µƒ¬∑æ∂…œ¥Ê‘⁄±£≥÷ ±º‰Œ•¿˝£¨◊Ó≤Ó«Èøˆœ¬±£≥÷ ±º‰Œ™ 0.076 ns°£

ƒ˙ø… π”√“‘œ¬ Tcl √¸¡Ó¿¥º∆À„ CLKOUT3 µƒœý“∆£¨“‘Ω‚æˆ¥À±£≥÷ ±º‰Œ £¨»ª∫Û∂‘∏√¬∑æ∂Ω¯––∂® ±£∫

set XPLL [get_cells >]

set THSviolation 0.076

set existingPhaseShift [get_property CLKOUT3_PHASE $XPLL]

set clkout3_divide [get_property CLKOUT3_DIVIDE $XPLL]

set c_stepsize [expr 45.0/$clkout3_divide]

set phaseAdjust [expr {$THSviolation / [get_property PERIOD [get_clocks -of [get_pins -of $XPLL -filter REF_PIN_NAME=~CLKOUT3]]] * 360}]

set updatedPhaseShift [expr {$existingPhaseShift + $phaseAdjust}]

set c_phase_rounded [format %.3f [expr $c_stepsize * round($updatedPhaseShift/$c_stepsize)]]

set c_phase_rounded_margin [format %.3f [expr $c_phase_rounded + $c_stepsize]]

set_property CLKOUT3_PHASE $c_phase_rounded_margin $XPLL

report_timing -from [get_pins {design_1_i/advanced_io_wizard_0/inst/design_1_advanced_io_wizard_0_0_phy_i/inst/phy_rden_int_bli_reg[*]/C}] -to [get_pins design_1_i/advanced_io_wizard_0/inst/design_1_advanced_io_wizard_0_0_phy_i/inst/BANK_WRAPPER_INST0/NIBBLE[1].UNISIM.I_XPHY/PHY_RDEN[*]]

Õ¨—˘£¨ƒ˙“≤ø… π”√“‘œ¬ Tcl √¸¡Ó¿¥º∆À„ CLKOUT3 µƒ–¬œý“∆£¨“‘Ω‚æˆ¥ÀΩ®¡¢ ±º‰Œ•¿˝£¨»ª∫Û∂‘∏√¬∑æ∂Ω¯––∂® ±£∫

set XPLL [get_cells >]

set WNSviolation 0.076

set existingPhaseShift [get_property CLKOUT3_PHASE $XPLL]

set clkout3_divide [get_property CLKOUT3_DIVIDE $XPLL]

set c_stepsize [expr 45.0/$clkout3_divide]

set phaseAdjust [expr {$WNSviolation / [get_property PERIOD [get_clocks -of [get_pins -of $XPLL -filter REF_PIN_NAME=~CLKOUT3]]] * 360}]

set updatedPhaseShift [expr {$existingPhaseShift - $phaseAdjust}]

set c_phase_rounded [format %.3f [expr $c_stepsize * round($updatedPhaseShift/$c_stepsize)]]

set c_phase_rounded_margin [format %.3f [expr $c_phase_rounded - $c_stepsize]]

set_property CLKOUT3_PHASE $c_phase_rounded_margin $XPLL

report_timing -from [get_pins {design_1_i/advanced_io_wizard_0/inst/design_1_advanced_io_wizard_0_0_phy_i/inst/phy_rden_int_bli_reg[*]/C}] -to [get_pins design_1_i/advanced_io_wizard_0/inst/design_1_advanced_io_wizard_0_0_phy_i/inst/BANK_WRAPPER_INST0/NIBBLE[1].UNISIM.I_XPHY/PHY_RDEN[*]]

»Áπ˚ Advanced IO Wizard ”–∂ý∏ˆ µ¿˝£®»Á”–∆‰À¸ IP π”√¥À Wizard£¨¿˝»Á SGMII£¨ƒ«“≤º∆À„‘⁄ƒ⁄£©£¨ƒ«√¥‘⁄ƒ≥–©«Èøˆœ¬£¨¥À Tcl Ω≈±æø…“‘Ω‚æˆ PHY_RDEN …œµƒ±£≥÷ ±º‰Œ £¨µ´ª·‘⁄ PHY_WREN ¬∑æ∂…œ“˝∑¢Ω®¡¢ ±º‰Œ °£

2022.2 ∞ʺ∞∏¸µÕ∞ʱ浃 Advanced IO Wizard ƒ¨»œ‘⁄ PHY_WREN ¬∑æ∂…œ≤ª π”√ BLI ºƒ¥Ê∆˜°£»Áπ˚ π”√∏√Ω≈±æΩ‚æˆ±£≥÷ ±º‰Œ µº÷¬ PHY_WREN ≥ˆœ÷Ω®¡¢ ±º‰Œ £¨«ÎŒ™ PHY_WREN …Ë÷√ BLI = TRUE£¨’‚—˘º¥ø…∞Ô÷˙Ω‚æˆ¥ÀŒ °£

‘⁄ XDC Œƒº˛÷–”¶”√œ¬¡–‘º ¯£¨»ª∫Û÷ÿ–¬‘À–– µœ÷°£

set_property BLI TRUE [get_cells -hierarchical phy_wren_bli_temp_*]

…Û∫À±ýº≠£∫ÿ˘∫Ï

-

Ω”ø⁄

+πÿ◊¢

πÿ◊¢

33Œƒ’¬

9049‰Ø¿¿¡ø

154169 -

pll

+πÿ◊¢

πÿ◊¢

6Œƒ’¬

891‰Ø¿¿¡ø

136592 -

±–Ú

+πÿ◊¢

πÿ◊¢

5Œƒ’¬

399‰Ø¿¿¡ø

38171 -

Versal

+πÿ◊¢

πÿ◊¢

1Œƒ’¬

170‰Ø¿¿¡ø

8143

∑¢≤º∆¿¬€«Îœ» µ«¬º

AMD Versal Adaptive SoC Clock Wizard AXI DRP æ¿˝

“ªŒƒœÍΩ‚Advanced IO wizard“Ï≤Ωƒ£ Ω

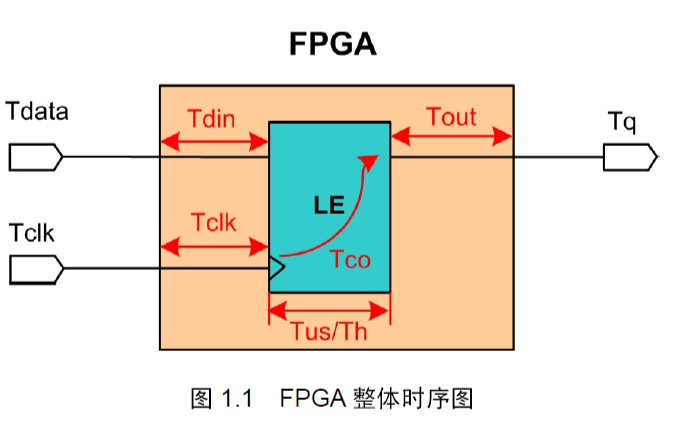

Ω¯––RTL¥˙¬Î…˺∆–Ë“™øº¬« ±–Ú ’¡≤µƒŒ Â

UltraFast…˺∆∑Ω∑® ±–Ú ’¡≤øÏΩð≤Œøº÷∏ƒœ

FPGAµƒIOø⁄ ±–Ú‘º ¯∑÷Œˆ

FPGA ±–Ú ’¡≤—ßœ∞±®∏Ê

«ÎŒ »Á∫Œ ’¡≤∏þÀŸADC ±–Ú£ø

”–ƒƒ–©∑Ω∑®ø…“‘Ω‚æˆ ±–Ú ’¡≤µƒŒ £ø

ª˘”⁄MCMMºº ıIC ±–Ú ’¡≤µƒøÏÀŸ µœ÷

FPGA ±–Ú ’¡≤»√ƒ„µƒ≤˙∆∑¥ÔµΩ◊Óº—–‘ƒÐ£°

FPGA÷–IOø⁄µƒ ±–Ú∑÷ŒˆœÍœ∏Àµ√˜

¥”“—≤ºœþ…˺∆÷–÷»°ƒ£øÈ”√”⁄∆¿π¿ ±–Ú ’¡≤æÕ–˜◊¥Ã¨

AMD Versal◊‘ ”¶SoC∆˜º˛Advanced Flow∏≈¿¿£®…œ£©

AMD Versal◊‘ ”¶SoC∆˜º˛Advanced Flow∏≈¿¿£®œ¬£©

Versal Advanced IO Wizard-≤ø∑÷≈‰÷√¥Ê‘⁄ ±–Ú ’¡≤Œ Â

Versal Advanced IO Wizard-≤ø∑÷≈‰÷√¥Ê‘⁄ ±–Ú ’¡≤Œ Â

∆¿¬€