本文将使用 Clocking Wizard文档 PG321中的“通过 AXI4-Lite 进行动态重配置的示例”章节作为参考。

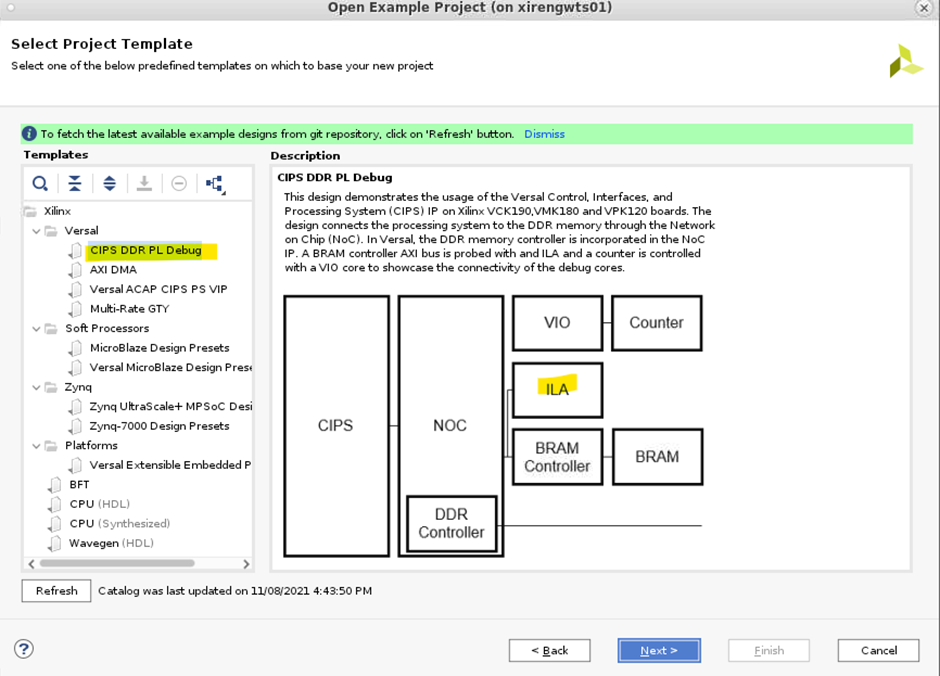

首先在 AMD Vivado Design Suite 中构建工程。本文使用的是 VCK190 评估板。

您可使用 Vivado 中的实用设计示例作为起点。选择 CIPS DDR PL 调试示例,其中 CIPS 已设置完成。

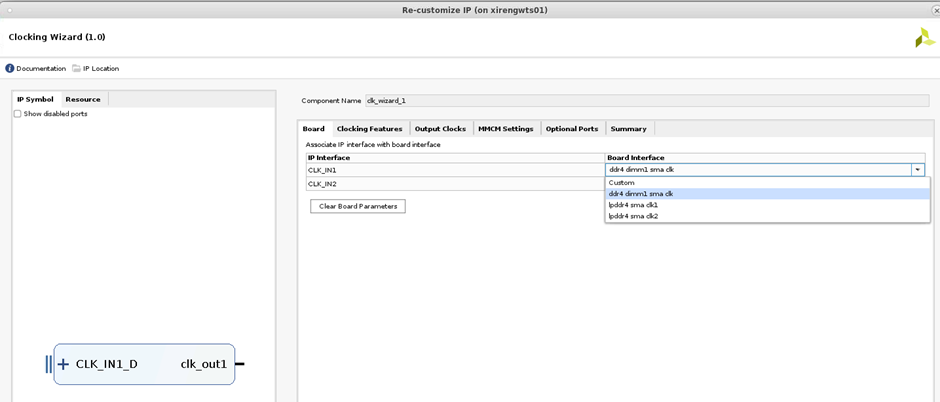

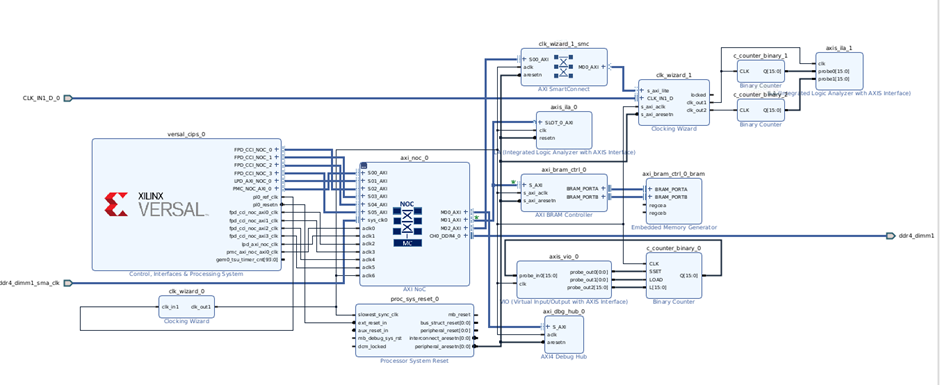

在块设计中,将 Clocking Wizard 添加到图形界面中。鉴于我们使用的是 VCK190,因此设置 CLK_IN1 = LPDDR4 SMA CLK2。

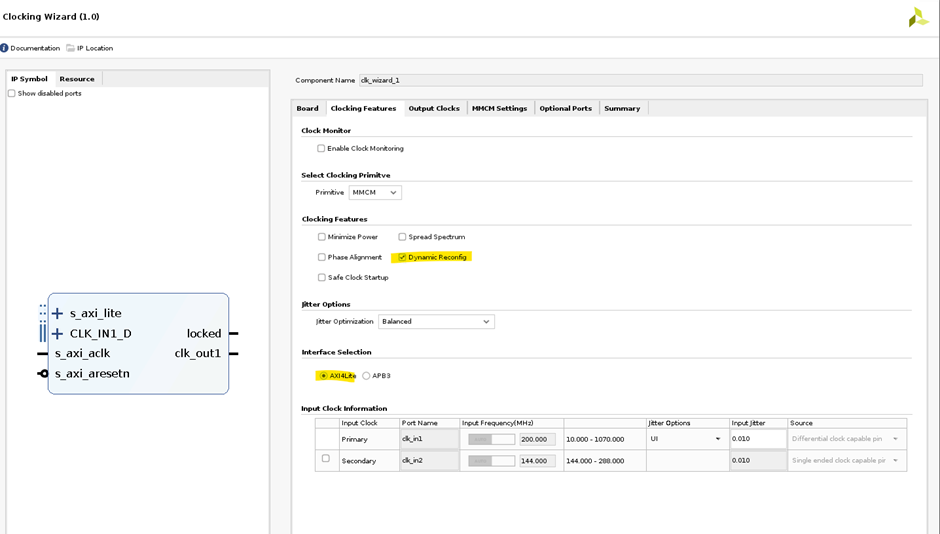

在“Clocking Features”选项卡上,选中“Dynamic Reconfiguration”选项卡,保留“Interface Selection”的设置“AXI4Lite”不变。

在“Output Clocks”选项卡上,选择两个输出时钟:100 MHz 和 50 MHz。

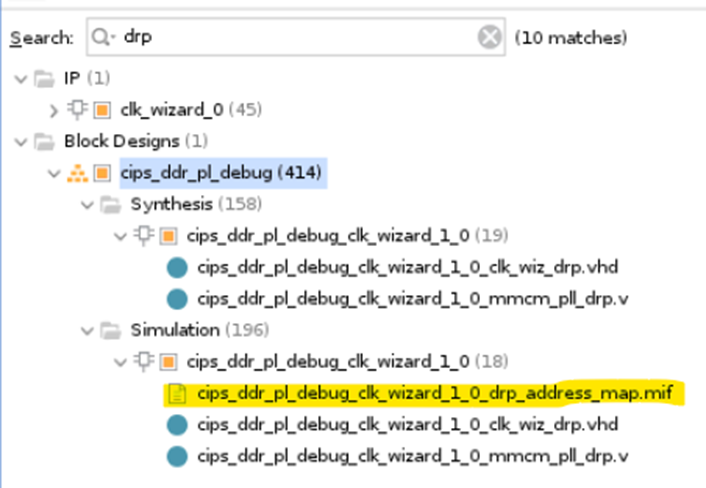

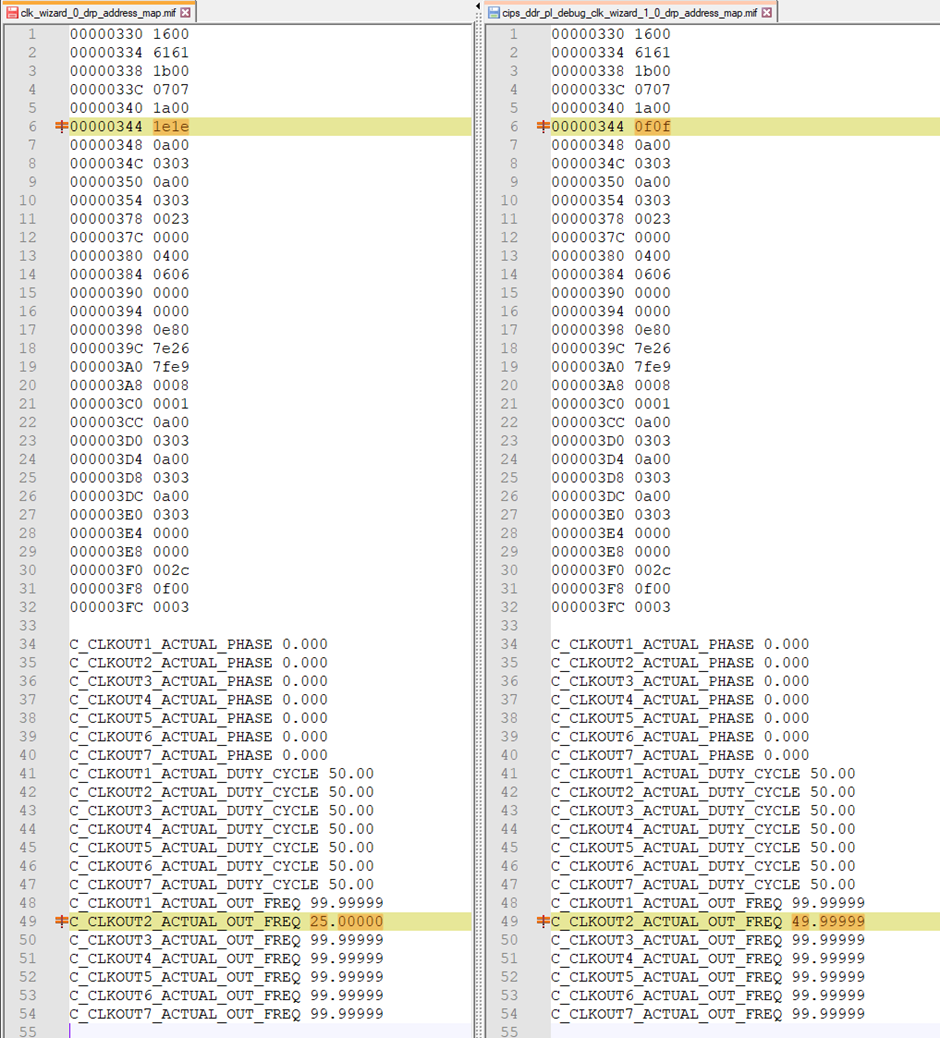

Clocking Wizard 将生成 _drp_address_map (MIF) 文件,其中包含地址和值列表,与 Wizard 中请求的值相对应。

您也能使用要重新配置的值来创建第二个 Clocking Wizard,以便生成重配置时要写入的地址和数据。

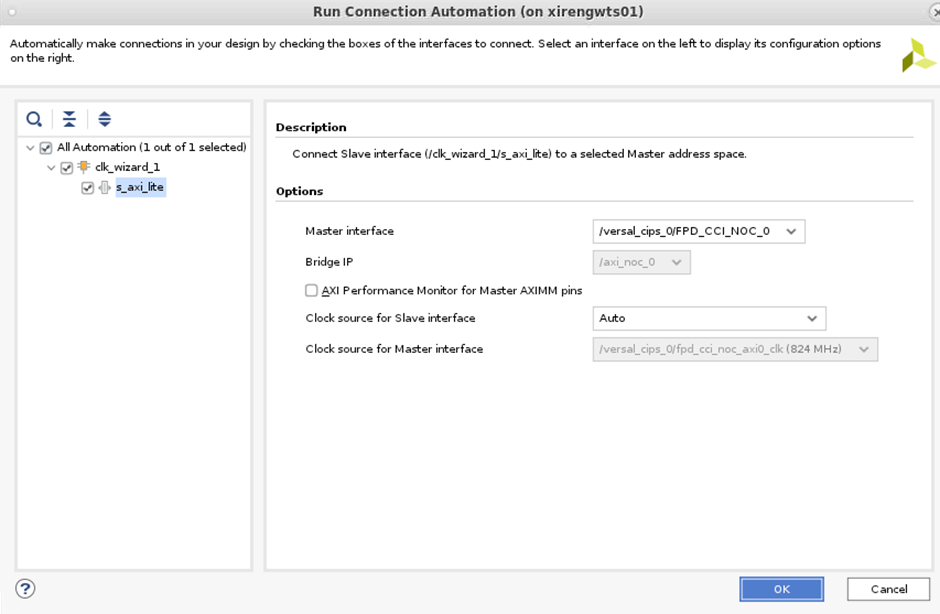

选择“Connection Automation”,将设置 Bridge IP 以将 AXI4-Lite 转化为 NOC/CIPS 上的 AXI 接口。

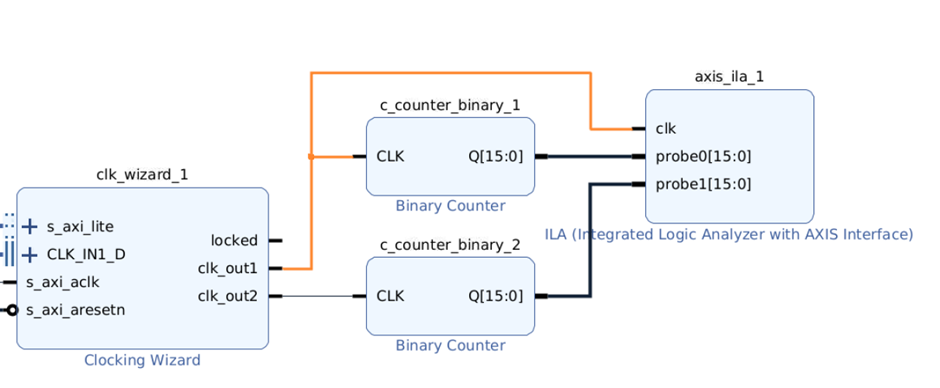

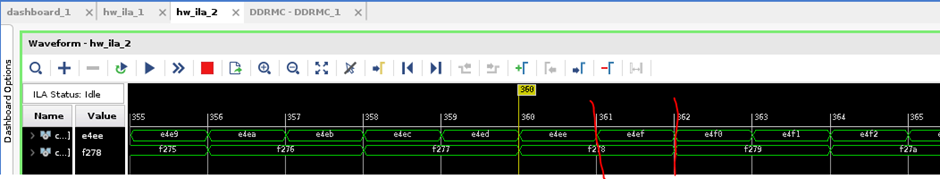

在此示例中,输出了 2 个时钟。这些是 ILA 捕获的 100 MHz 和 50 MHz 时钟计数器,可以比较这 2 个计数器来直观显示相对频率。

此处随附了 BD Tcl 供您参考:

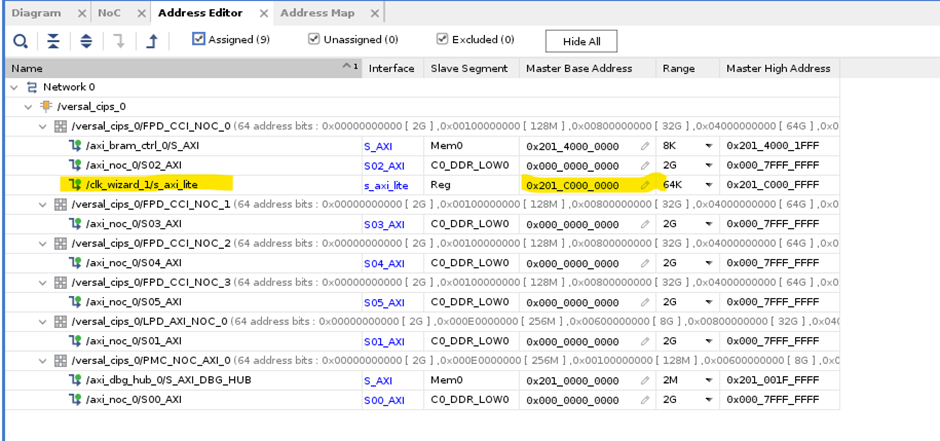

在“Address Editor”中,可看到 Clock Wizard 的“Base Address”。在 Clock Wizard 实例中,“Base Address”为 0x201C0000000。

运行实现,并写入器件镜像。然后选择“Export -> Export Hardware”并选择“Include device image”。这样会生成包含 Clock Wizard 的 XSA 文件。

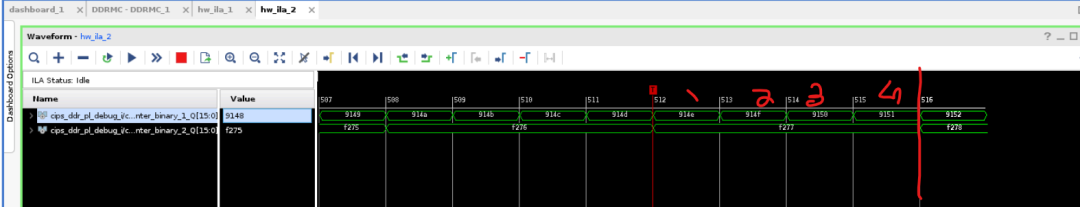

在此阶段可以下载 PDI 并进行检查。您会看到其中一个计数器的速率是另一个计数器的两倍。

CLK_OUT1 工作频率为 100 MHz,时钟设置为 c_counter_binary_1。CLK_OUT2 工作频率为 50 MHz,时钟设置为 c_counter_binary_2。因此,c_counter_binary_1 的工作频率是 c_counter_binary_2 的两倍。

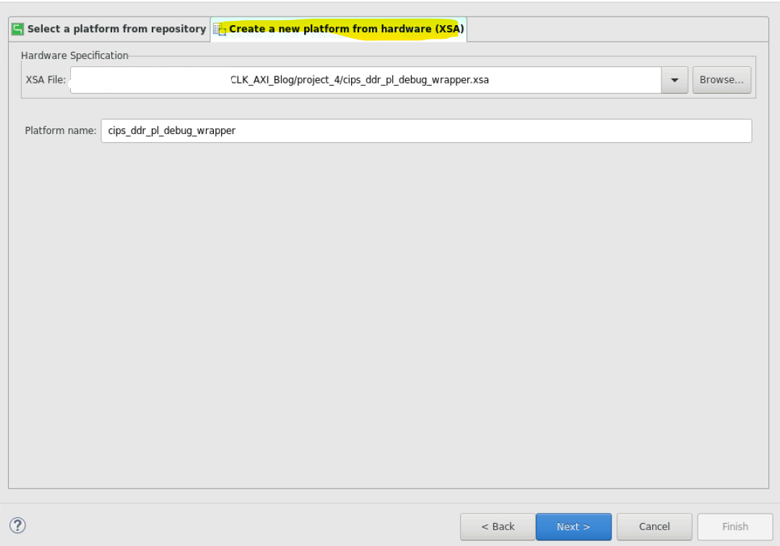

要启动 AMD Vitis 统一软件平台,请转至“Tools -> Launch Vitis IDE”,并选择或创建工作空间。

选择“Create Application Project”,在“Platform”选项卡上,选中“Create a new platform from hardware (XSA)”。

为应用工程命名。“Domain”保留默认设置。

对于“Templates”,如果 XSA 中有 UART(对于 VCK190,UART 包含在 CIPS 中),那么您可以选择“Hello World”,否则,您可以选择“Empty Application”。

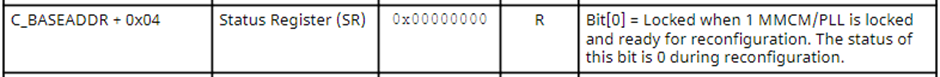

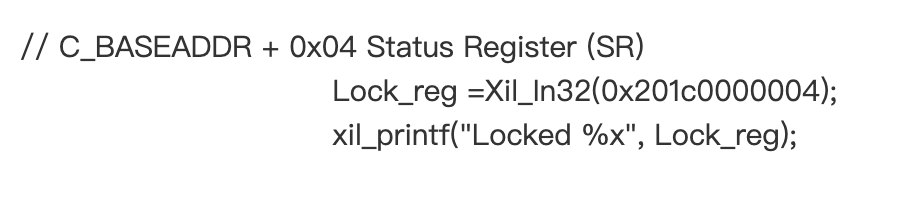

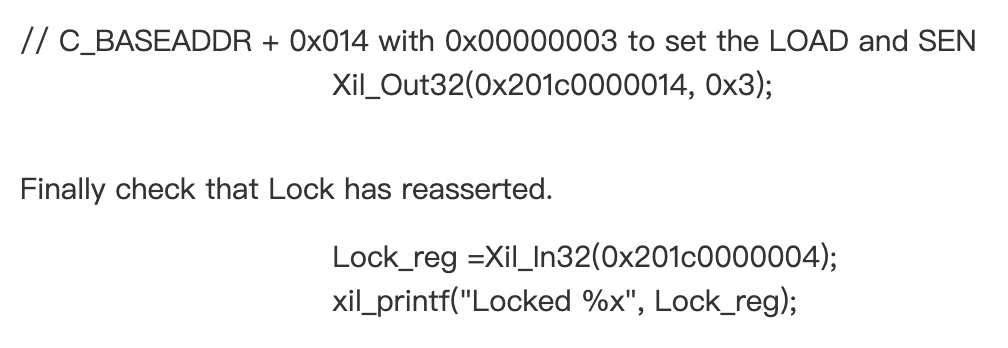

我们已知 Clock Wizard 基地址为 0x201C0000000。在 Clocking Wizard 中,使用 PG 读取 LOCKED 状态,OFFSET 为 0x4。

利用 Xil_In32 和 Xil_Out32 通过 AXI 直接读取和写入地址。

在示例中,把 CLKOUT2 从 50 MHz 重配置为 25 MHz。

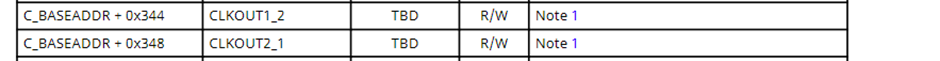

以下是第二个 Clocking Wizard 的 drp_address_map (MIF),其中 CLKOUT2 设为 25 MHz(而不是 50 MHz)。

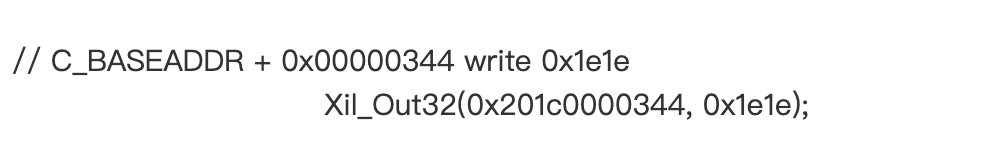

在地址 0x201c0000344 处,写入数据 0x1e1e。

下一步是写入并应用该 DRP 值以配置地址:C_BASEADDR + 0x014,搭配 0x00000003 以设置 LOAD 位和 SEN 位。

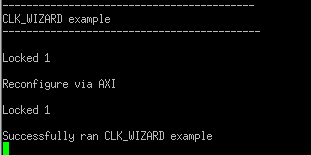

在终端上会看到:

返回到 ILA 并观察 c_counter_binary_1 的计数结果是否是 c_counter_binary_2 的 4 倍。

Clocking Wizard 包含软件驱动程序,其中包含的示例在使用 AXI DRP 时也很有帮助。

-

amd

+关注

关注

25文章

5594浏览量

136574 -

DDR

+关注

关注

11文章

733浏览量

66989 -

soc

+关注

关注

38文章

4406浏览量

223182 -

design

+关注

关注

0文章

162浏览量

46692 -

评估板

+关注

关注

1文章

762浏览量

30260

原文标题:开发者分享|AMD Versal? Adaptive SoC Clock Wizard AXI DRP 示例

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

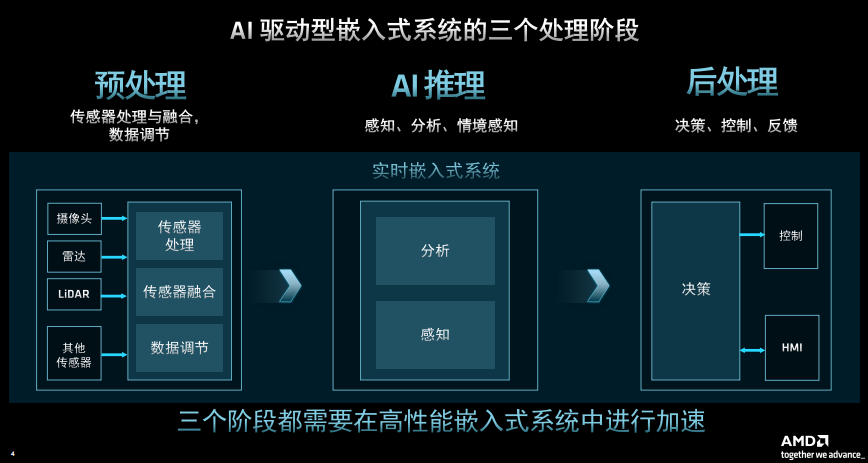

AMD Versal SoC刷新边缘AI性能,单芯片方案驱动嵌入式系统

《电子发烧友电子设计周报》聚焦硬科技领域核心价值 第13期:2025.05.26--2025.05.30

Versal CPM AXI Bridge模式的地址转换

AMD Versal SoC全新升级边缘AI性能,单芯片方案驱动嵌入式系统

AMD发布第二代Versal自适应SoC,AI嵌入式领域再提速

AMD Versal? Adaptive SoC CPM PCIE PIO EP设计CED示例

AMD Versal自适应SoC CPM5 QDMA的Tandem PCIe启动流程介绍

AMD Vivado Design Suite 2024.2全新推出

如何通过PMC_GPIO唤醒AMD Versal? Adaptive SoC Linux系统

AMD Versal自适应SoC DDRMC如何使用Micron仿真模型进行仿真

AMD Versal自适应SoC器件Advanced Flow概览(上)

AMD Versal自适应SoC器件Advanced Flow概览(下)

第二代AMD Versal Premium系列SoC满足各种CXL应用需求

AMD Versal Adaptive SoC Clock Wizard AXI DRP示例

AMD Versal Adaptive SoC Clock Wizard AXI DRP示例

评论