关于 FPGA 的 IO资源分析共分为三个系列进行具体阐述,分别为:

IO资源:分析FPGA IO资源的电气特性;

IO逻辑资源:分析FPGA的输入输出数据寄存器、DDR工作方式、可编程输入延时工作方式;

IO串并转换资源:分析IO资源如何实现串并转换。

其中第二、三系列是对第一系列中的部分内容进行更进一步的详细描述。本篇是对于第一个系列——IO资源进行部分描述,共分为几个章节进行具体阐述。

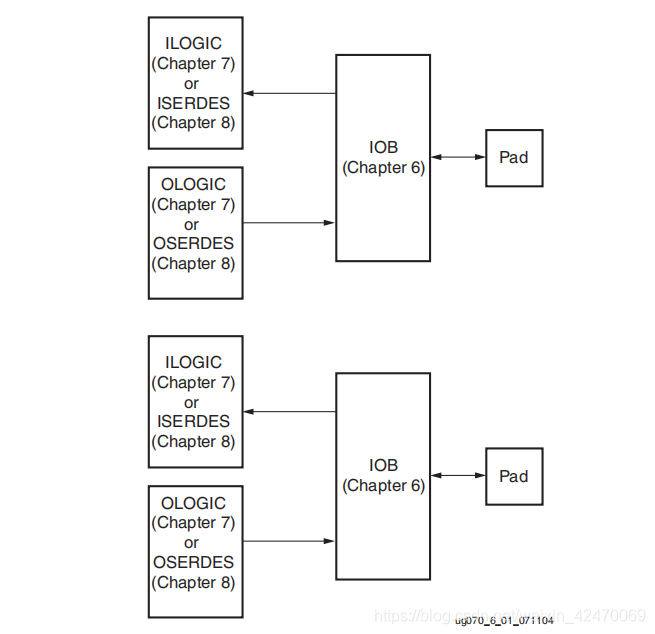

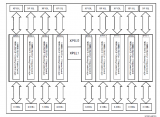

FPGA IO资源的基本单元架构为一个个 IO tile ,下图为 IO tile 的结构概略图:

一个 IO tile 包含两个 IOB、两个 ILOGIC 和 两个 OLOGIC。本篇主要描述 IOB 的结构。

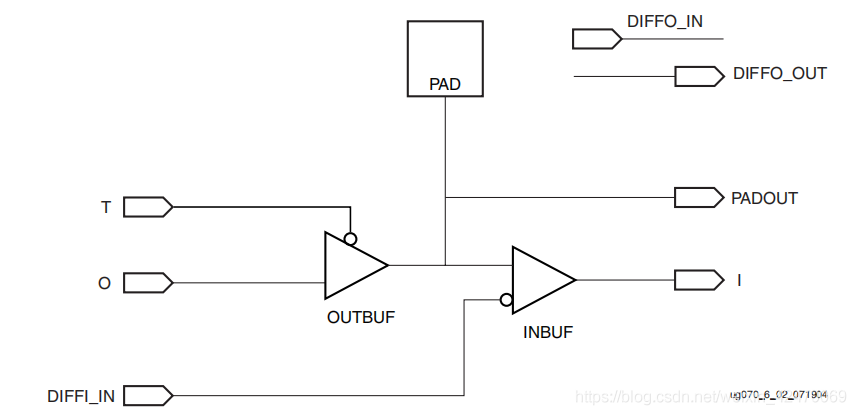

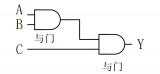

IOB的基本结构如下图所示,包含了输入缓冲、输出缓冲和三态控制三种驱动。

一、FPGA的开发软件提供了 IOB 不同功能的原语(primitives):

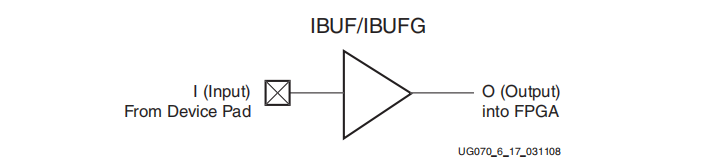

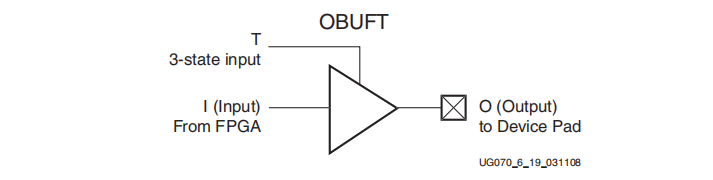

对于单端信号:

IBUF (input buffer)

IBUFG (clock input buffer)

OBUF (output buffer)

OBUFT (3-state output buffer)

IOBUF (input/output buffer)

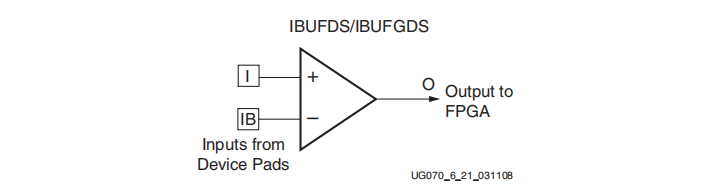

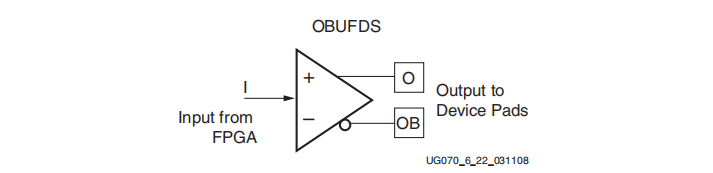

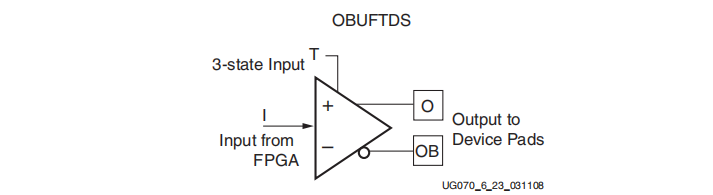

对于差分信号:

IBUFDS (input buffer)

IBUFGDS (clock input buffer)

OBUFDS (output buffer)

OBUFTDS (3-state output buffer)

IOBUFDS (input/output buffer)

注意:一对差分信号作为输入输出时必须使用同一 tile 的 P/N 管脚,如下图的 L31P 和 L31N 为同一tile上的一对差分管脚。

二、定义好 IOB 输入输出特性后,FPGA开发软件还提供对 IOB 的管脚约束、IO接口电气标准、输出压摆率、输出驱动能力、低容性IO、IO上下拉、差分100欧姆匹配电阻使能的设置。可以参考相关FPGA的数据手册,查看具体参数设置。

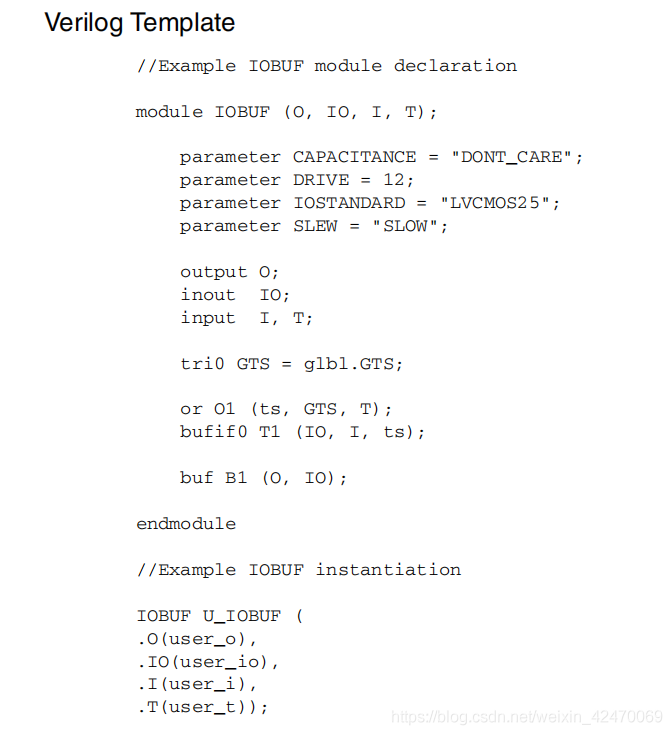

三、以上原语及设置如何实现?拿IOBUF举个例子:

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA 结构分析 -IO 资源

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1647文章

22109浏览量

621151

原文标题:FPGA 结构分析 -IO 资源

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

FPGA的定义和基本结构

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

Why FPGA开发板喜欢FMC?

有没有对appsfpga_io模块输入端功能时序的控制的资料?

请问AFE5801的输入输出可以直接和FPGA的IO连吗?

fpga和cpu的区别 芯片是gpu还是CPU

xilinx FPGA IOB约束使用以及注意事项

λ-IO:存储计算下的IO栈设计

ADC3663的SPI配置管脚连接至FPGA时遇到IO电平不匹配怎么解决?

RISC-V内核是如何与FPGA内核进行资源共享的?

详解FPGA的基本结构

FPGA 结构分析 -IO 资源

FPGA 结构分析 -IO 资源

评论