ISE版本为14.7

1、时钟IP核(Clocking Wizard)

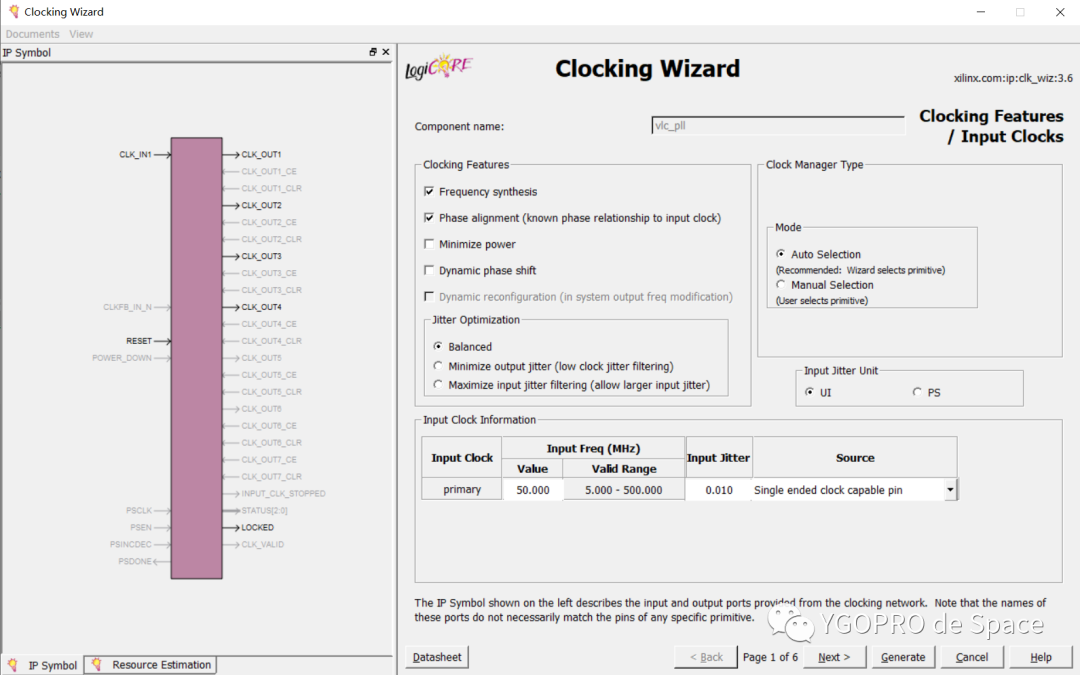

第一页

Clocking Features选项框中:

(1)Frequency synthesis选项是允许输出与输入时钟不同频率的时钟。

(2)Phase alignment选项是相位锁定,也就是将输出始终的相位和一个参考时钟同步,大多是和输入时钟同步。

(3)Minimize power选项为降低功耗,也就是资源,取而代之的是相位、频率的偏差,对于对时钟要求不高、资源有限的情况下可以使用,一般不推荐选此选项。

(4)Dynamic Phase Shift该选项为提供动态相移功能,选上此选项之后,可以在输入端控制相移,并有相移完成之后的反馈,相移步进长度为固定的几个值。

(1)Balanced就是在抖动优化时选择比较均衡的正确带宽。(一般选这个)

(2)Minimize output jitter:使输出时钟抖动最小,但是可能会增加功耗或资源,可能导致输出相位错误。

(3)Maximize input jitter filtering:该选项表示可使输入时钟抖动变大,但是可能会导致输出时钟抖动变大。

其他选项按照图中选择。

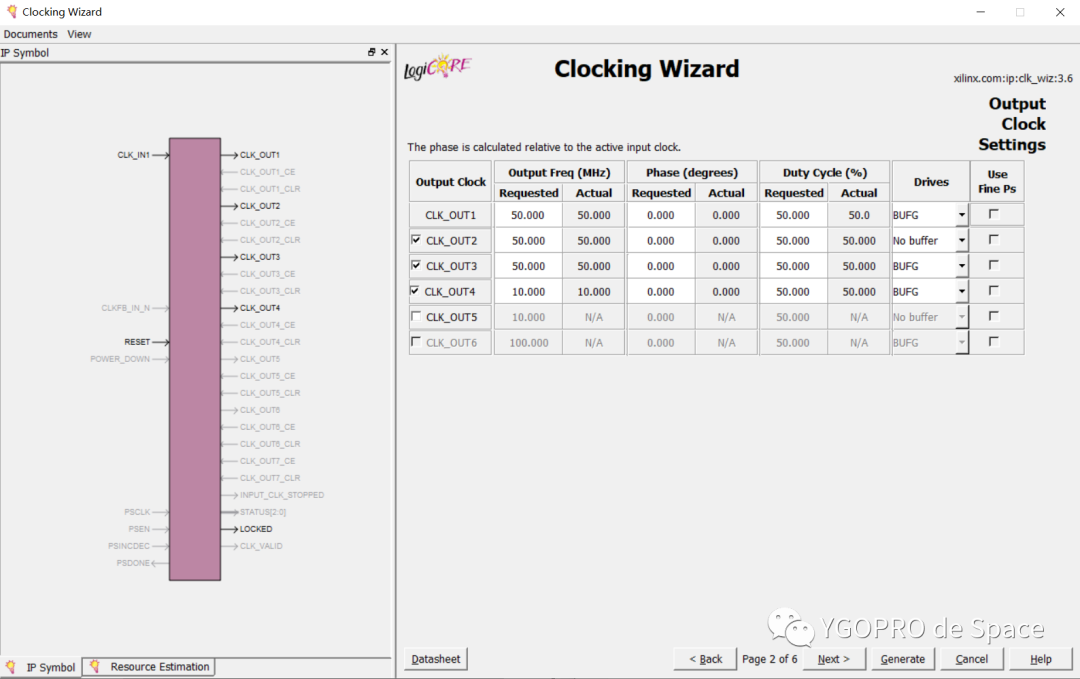

第二页

选择输出CLK端口

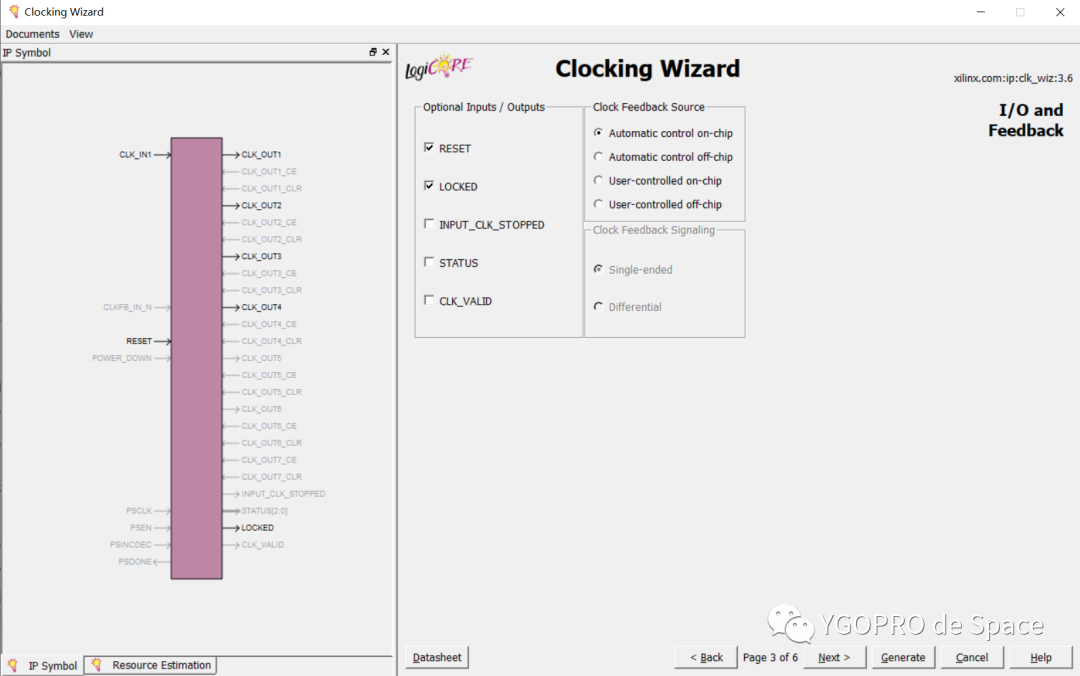

第三页

可选端口,可根据实际应用选择,一般情况下reset,locked选上。

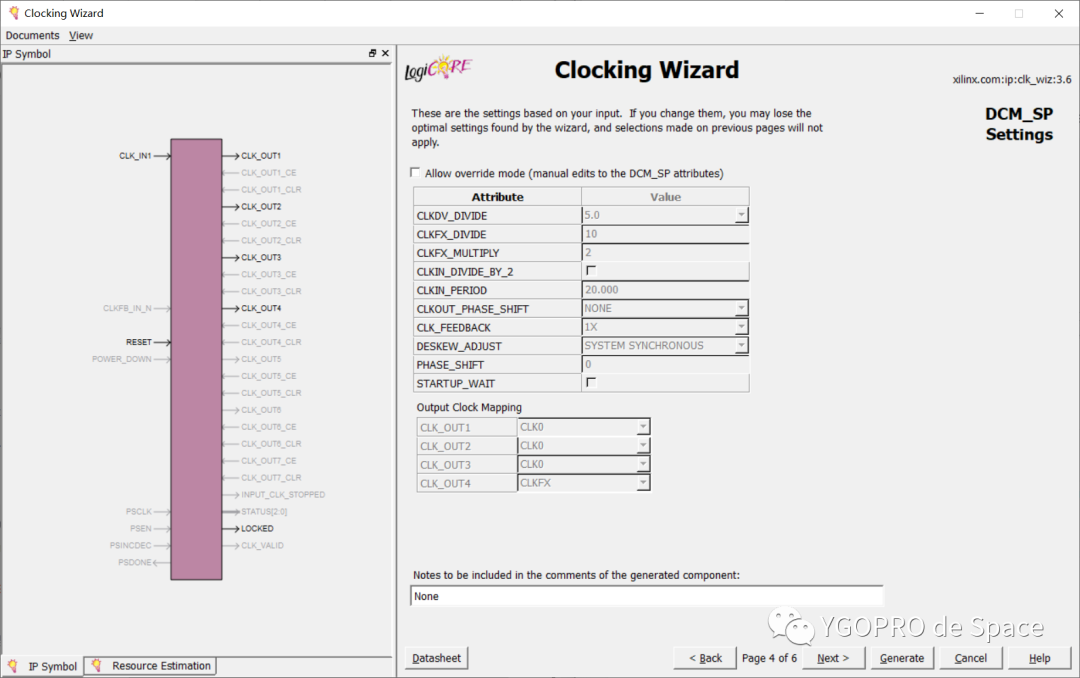

第四页

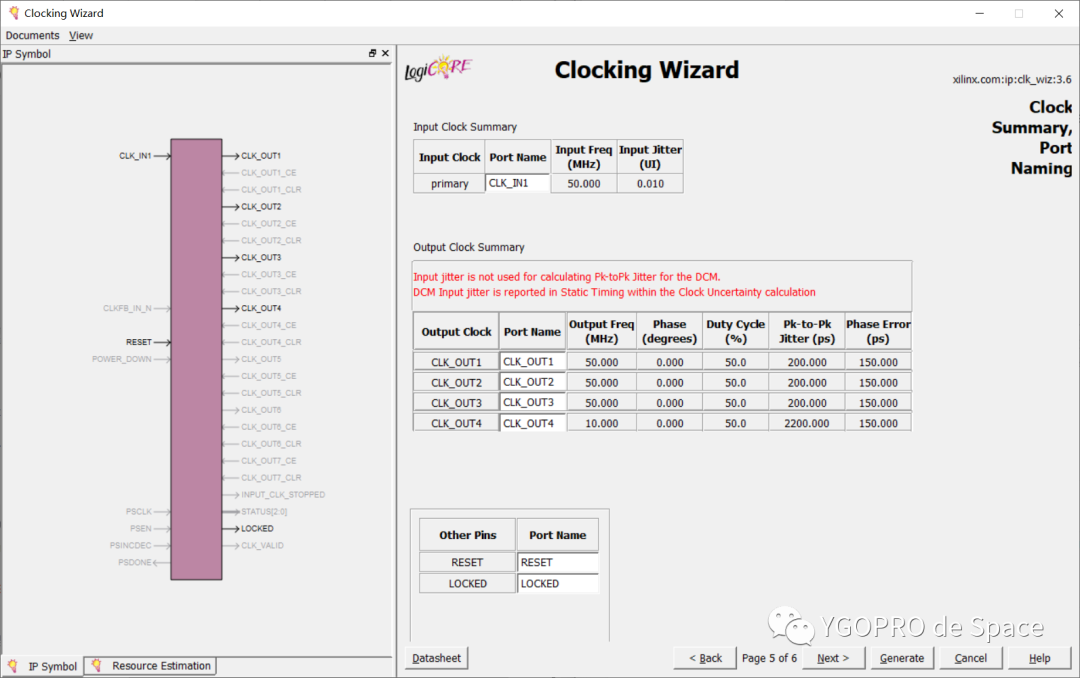

第五页

可对端口进行重命名。

2、FIFO IP核(FIFO Generator)

fifo是一种先进先出的数据存储和缓冲器,其本质是RAM。fifo的位宽就是每个数据的位宽,fifo的深度简单来说是需要存多少个数据。fifo有同步fifo和异步fifo两种,同步即读写时钟相同,异步fifo即读写时钟不同。一般异步fifo用的较多,用来处理跨时钟域的问题。

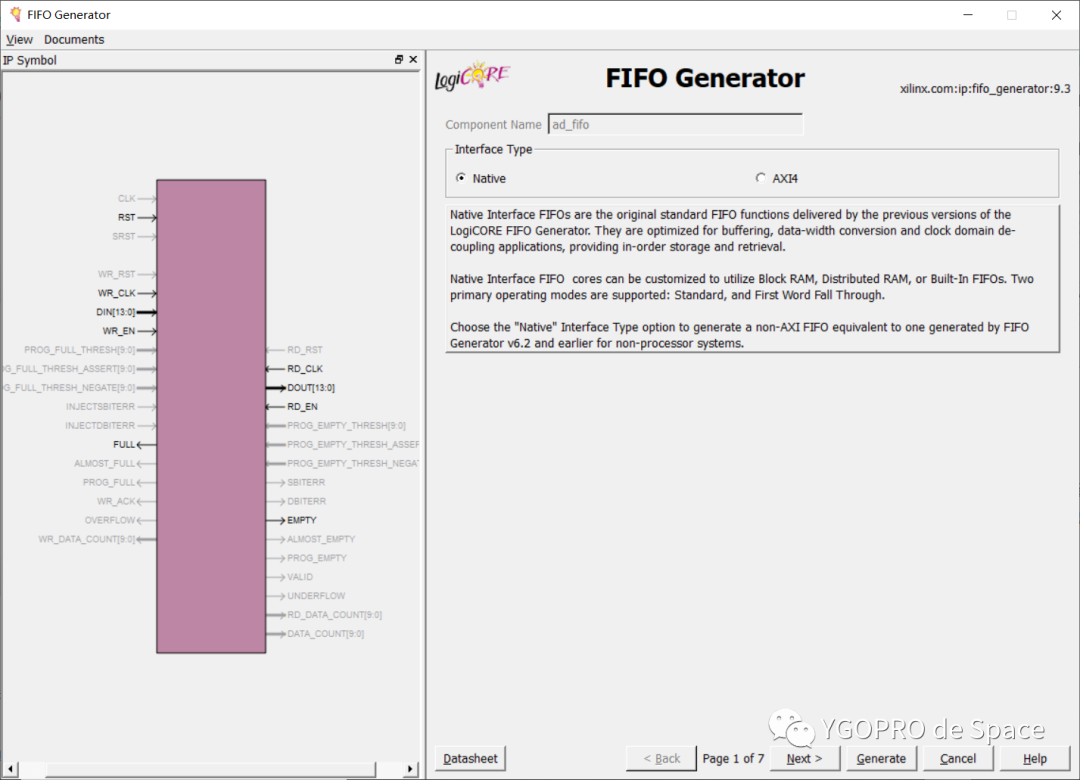

第一页

接口类型选择Native类型的,AXI4是与DMA或与其他有AXI4接口通信时使用的。

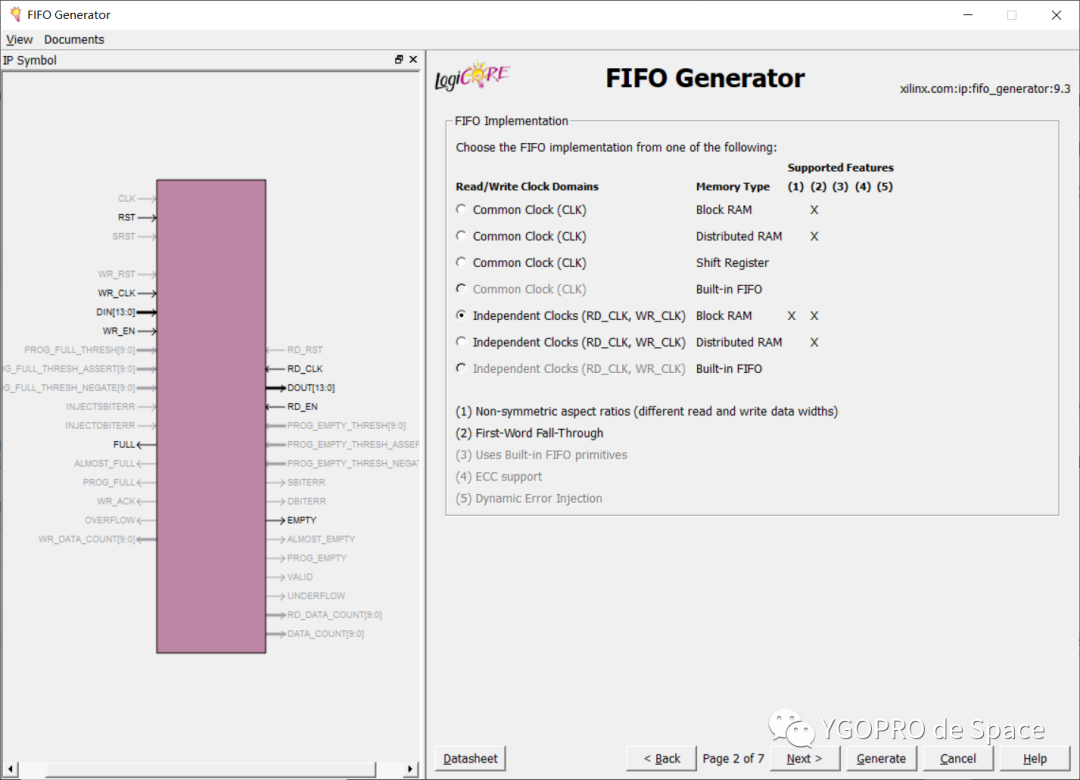

第二页

(1)选择异步时钟,FIFO的主要功能就是用在异步时钟域作为缓存,所以选择独立时钟的模式使用范围更广。

(2)Memory Type :常用的有Block Ram 和 Distrubtion RAM ,前者使用片上ROM作为缓存,后者使用LUT逻辑资源搭建RAM缓存,如果使用FIFO不大,或者资源充足的情况下,使用Block RAM。

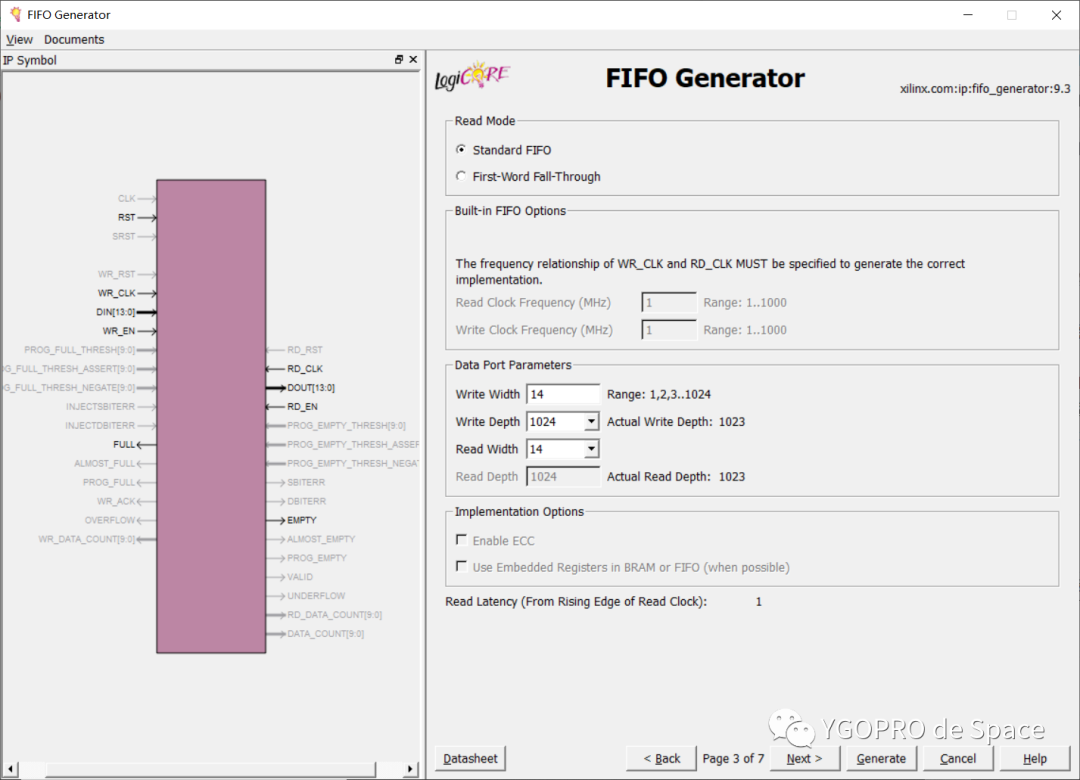

第三页

(1)Read Mode:First-word Fall-Through 与 Stanbdard FIFO 的区别是,Standard FIFO为当给出读使能后,数据会延迟一拍;First-Word Fall-Through 则是当给出读使能,立即给出数据。

(2)根据自己的需求设置位宽和深度

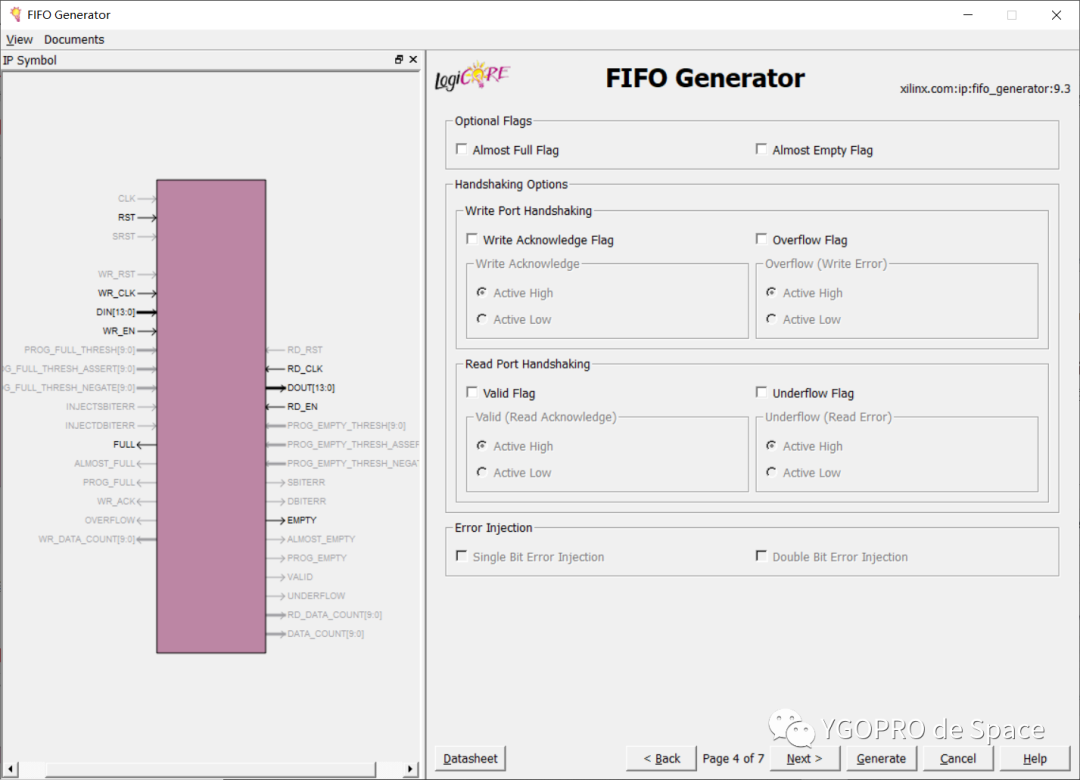

第四页

Almost Full Flag 和 Almost Empty Flag 指示FIFIO快要满/空,根据需求选择。

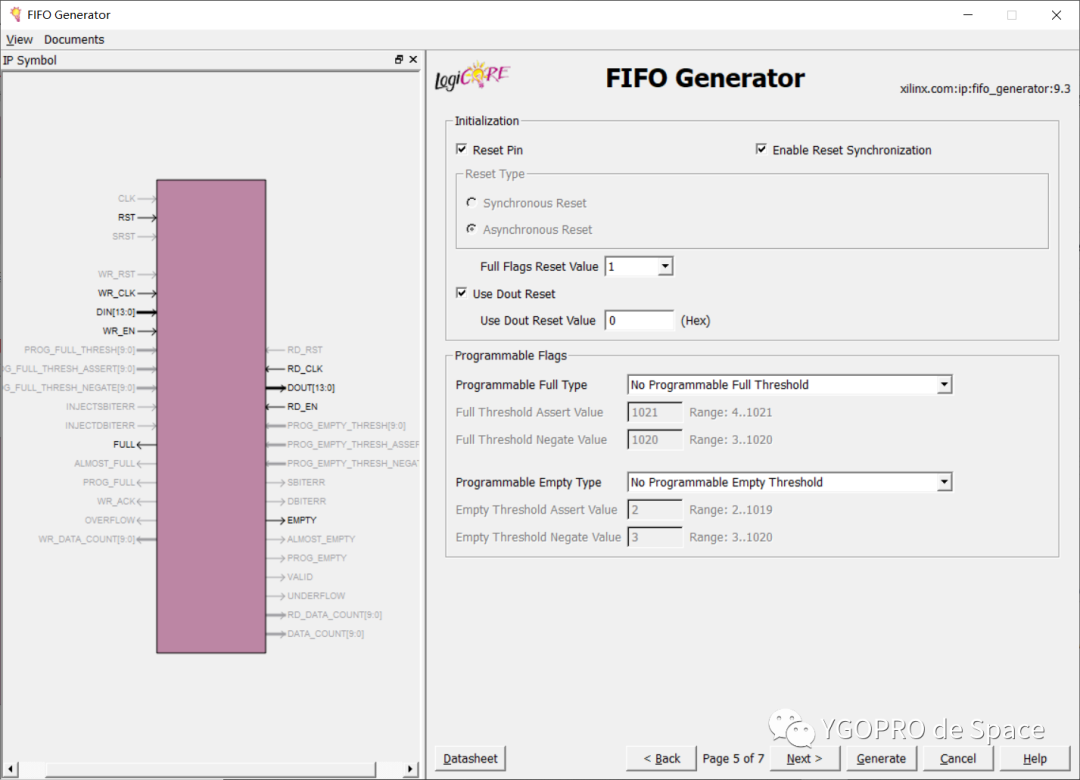

第五页

Programmable Full Type 和 Programmable Empty Type 是:根据需要设置提前多少个数据来给自己提示即将写满还是即将读空。

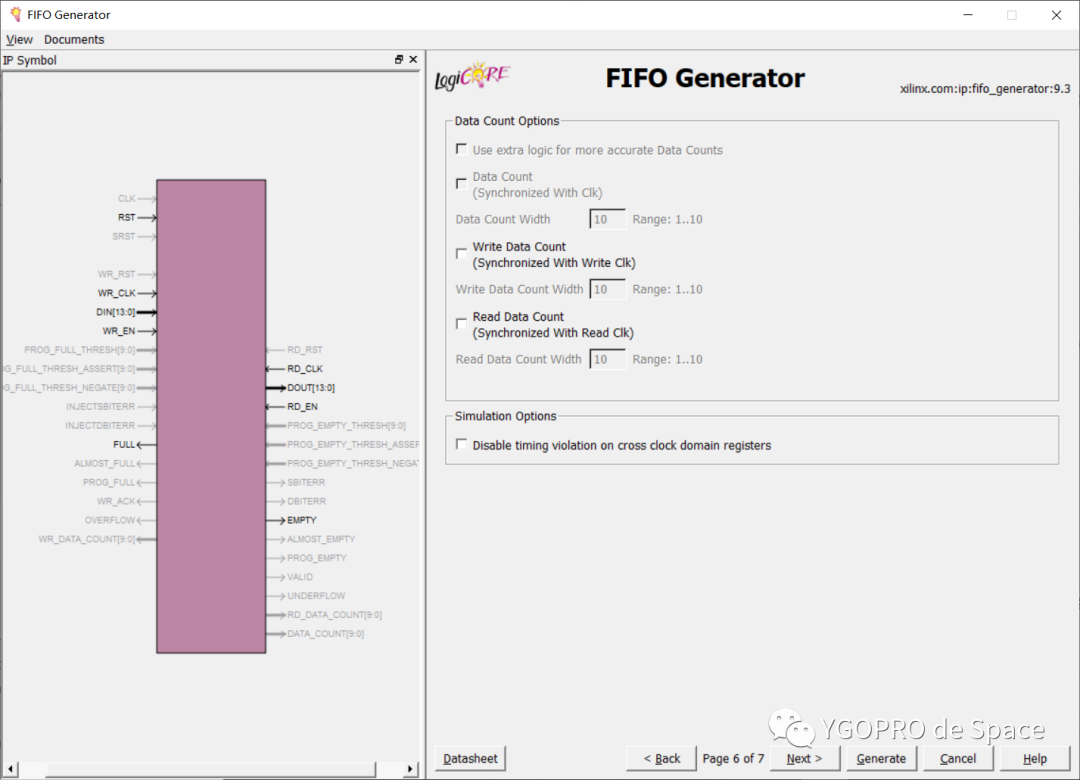

第六页

默认设置

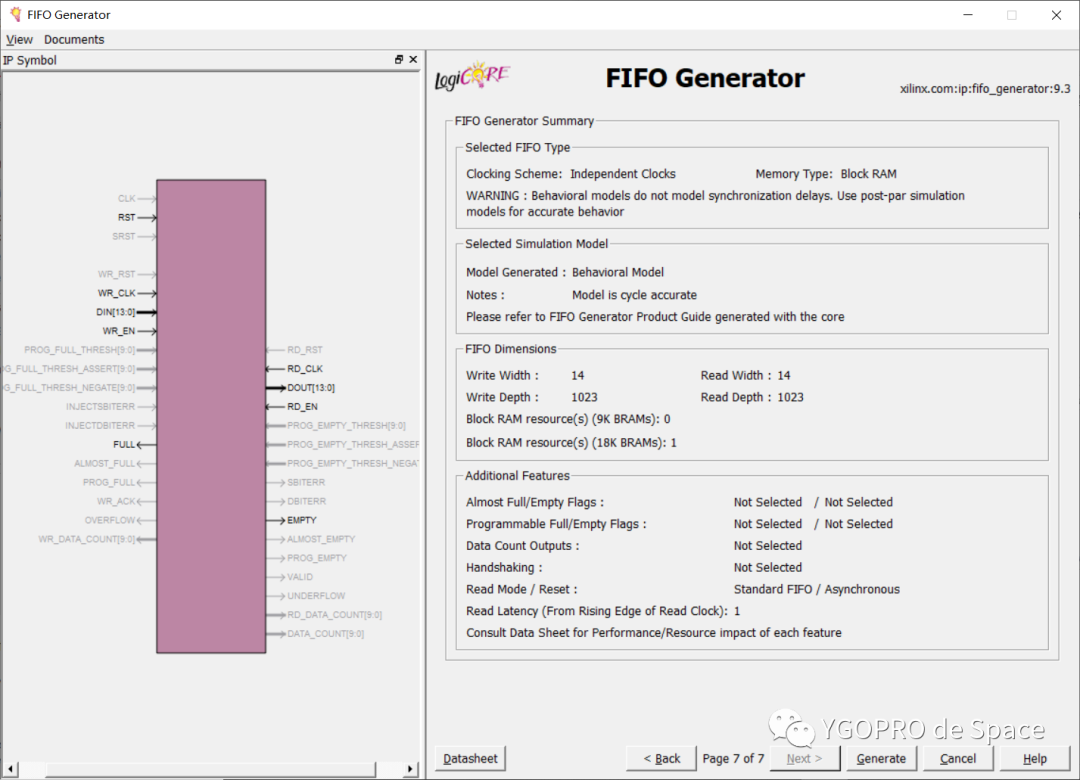

第七页

最后给出设置的fifo的报告,点击generate生成IP核心。

3、RAM IP核(Block Memory Generator)

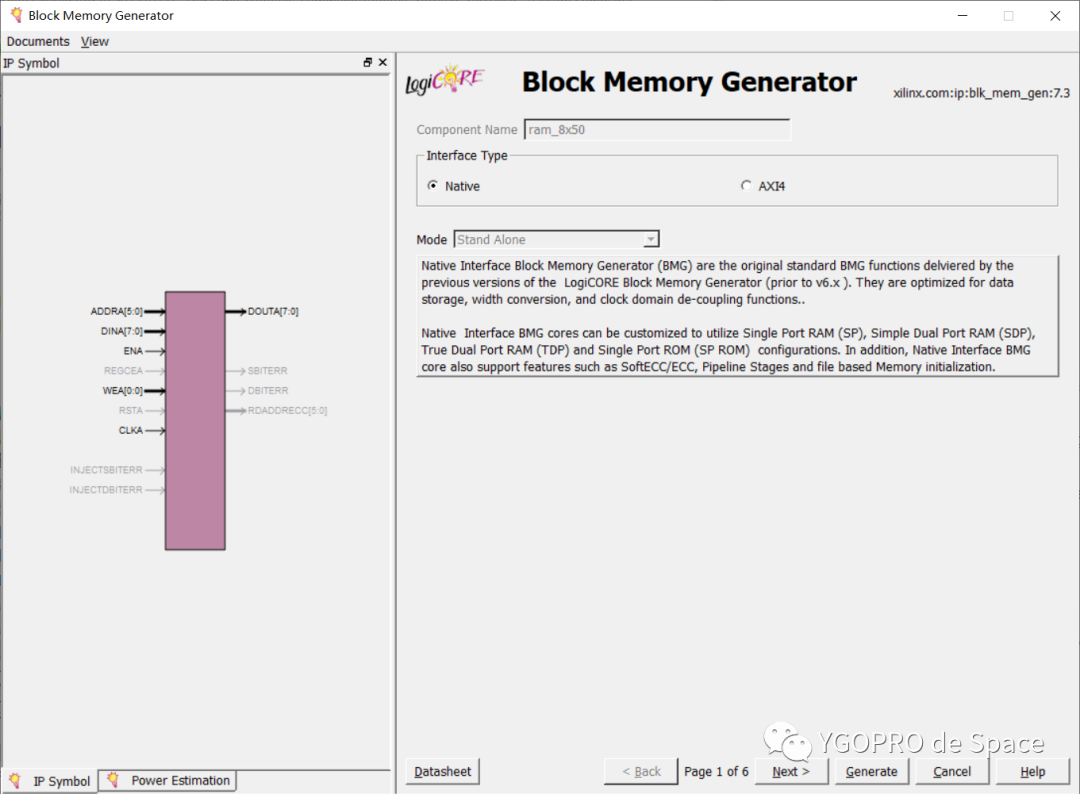

第一页

InterfaceType选择Native

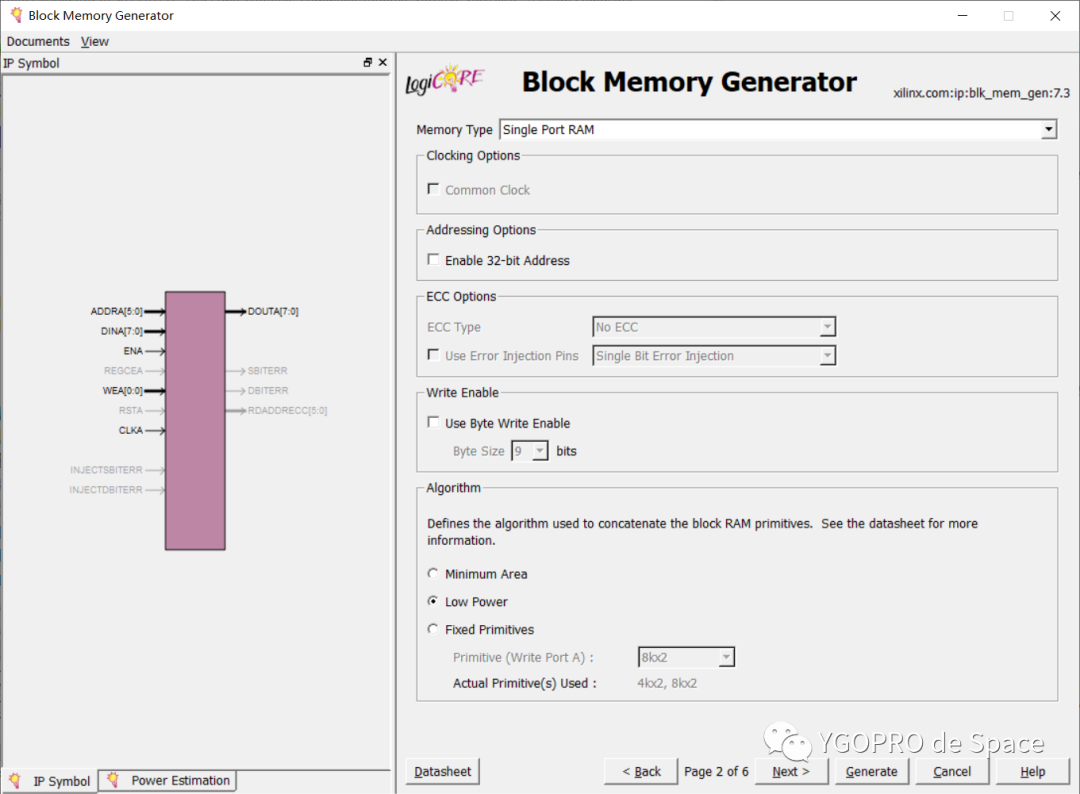

第二页

Single Port RAM:单口RAM

ADDRA 为地址线

DINA 为数据输入端

ENA 为可选端口,在其为高电平时,才使能

WEA 为写使能“当其为高电平时,DINA数据才会被写入对应的地址

DOUTA 为A输出端

CLKA 为时钟线

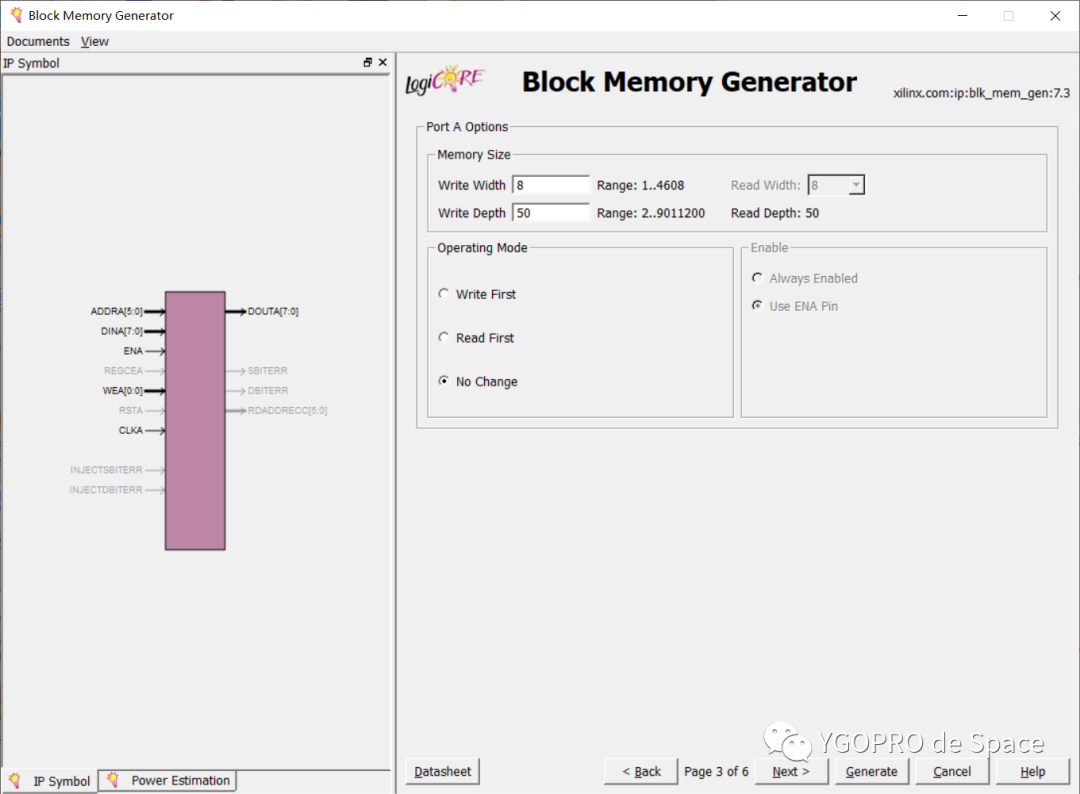

第三页

配置写入宽度和深度

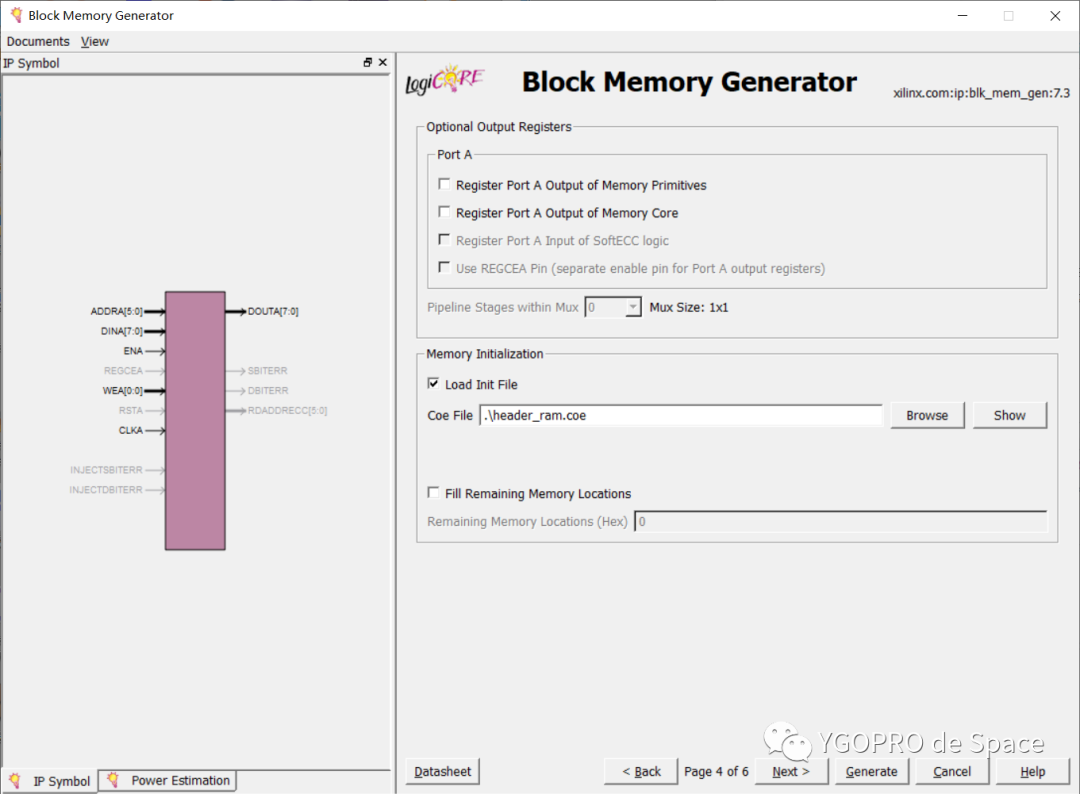

第四页

加载coe文件:

memory_initialization_radix = 10; //数据进制

memory_initialization_vector =1,2,3;//数据,数据以分号结束

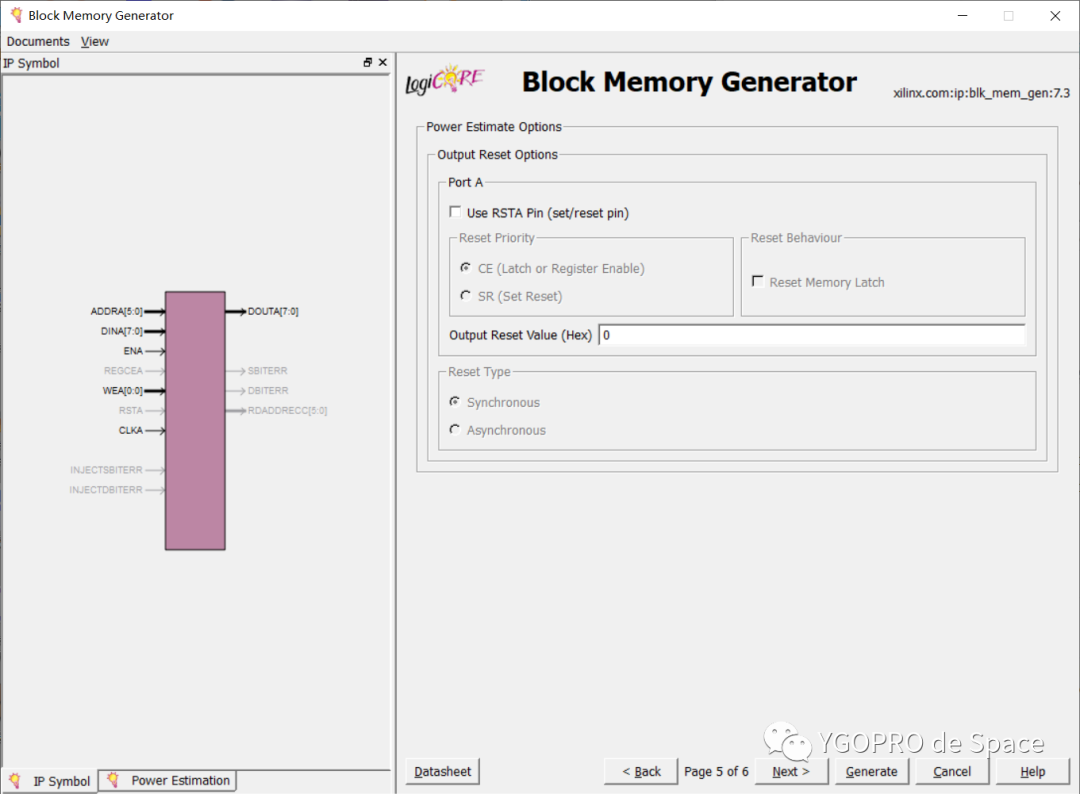

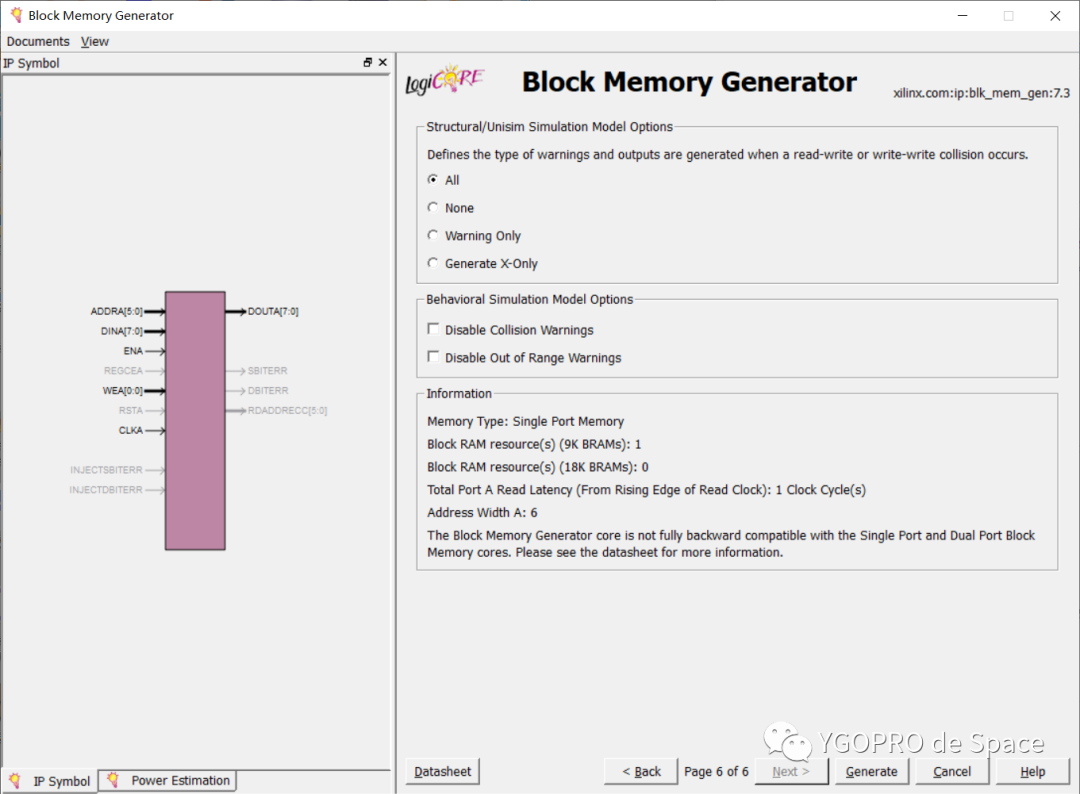

第五六页

默认设置。

原文标题:Xilinx常用IP核配置

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

-

带宽

+关注

关注

3文章

998浏览量

42401 -

IP

+关注

关注

5文章

1826浏览量

153252 -

端口

+关注

关注

4文章

1077浏览量

33160

原文标题:Xilinx常用IP核配置

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【RK3568+PG2L50H开发板实验例程】FPGA部分 | Pango 的时钟资源——锁相环

VIVADO自带Turbo译码器IP核怎么用?

FPGA时序约束之设置时钟组

一文详解Video In to AXI4-Stream IP核

Linux ip命令常用操作

新加坡共享主机怎么设置ip

ALINX发布100G以太网UDP/IP协议栈IP核

在FPGA里面例化了8个jesd204B的ip核同步接收8块AFE芯片的信号,怎么连接设备时钟和sysref到AFE和FPGA?

芯驿电子 ALINX 推出全新 IP 核产品线,覆盖 TCP/UDP/NVMe AXI IP 核

芯驿电子ALINX推出全新IP核产品线

Xilinx DDS IP核的使用和参数配置

时钟IP核常用设置

时钟IP核常用设置

评论