在设计FPGA项目的时候,对时钟进行约束,但是因为算法或者硬件的原因,都使得时钟约束出现超差现象,接下来主要就是解决时钟超差问题,主要方法有以下几点。

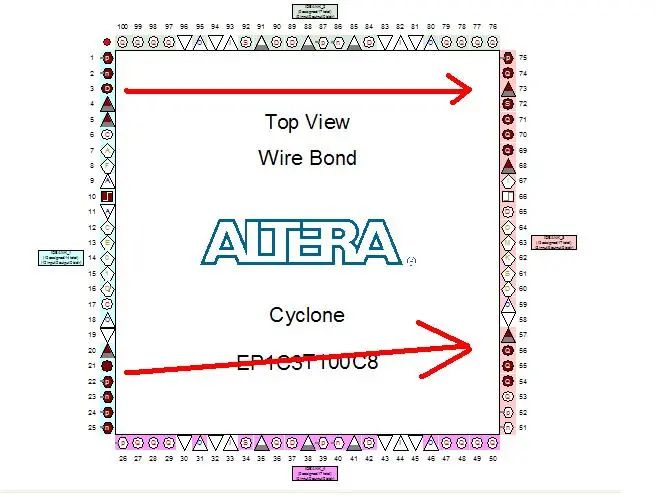

第一:换一个速度更快点的芯片,altera公司的cyclone系列FPGA,有6,7,8速度等级的,8的最慢,6的最快,或者cyclone系统4,5更快的芯片,当然了成本会增加些的。

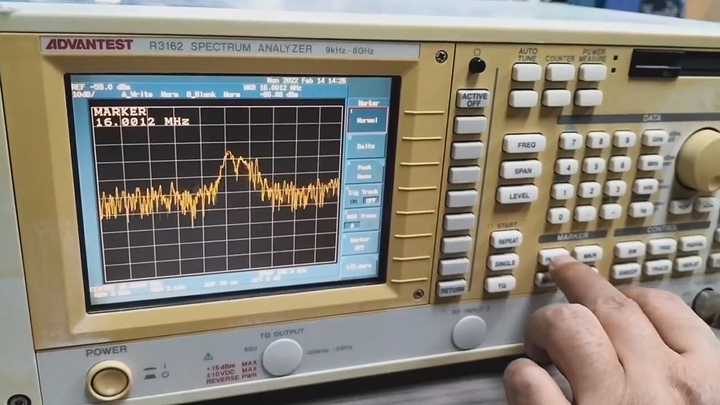

第二:尽量避免在FPGA中做乘法和除法的运算,除非这个FPGA有硬件乘法器。我使用的这个FPGA没有硬件乘法器,我就尽量利用左移或者右移来做乘法和除法运算。

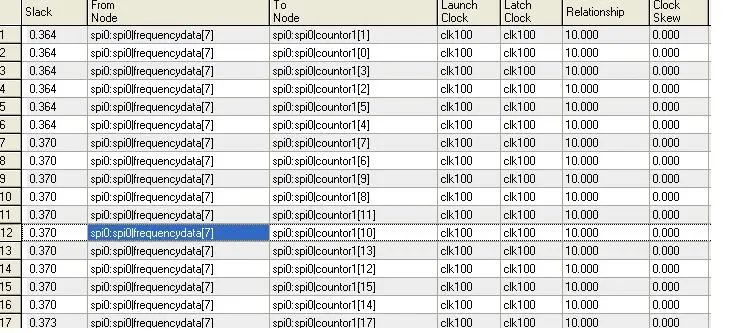

第三:重新分配一下IO管脚,这样在布局布线的时候,会提高一定程度的时钟余量。下图是调整IO分配以后,时钟余量提高了0.2ns。

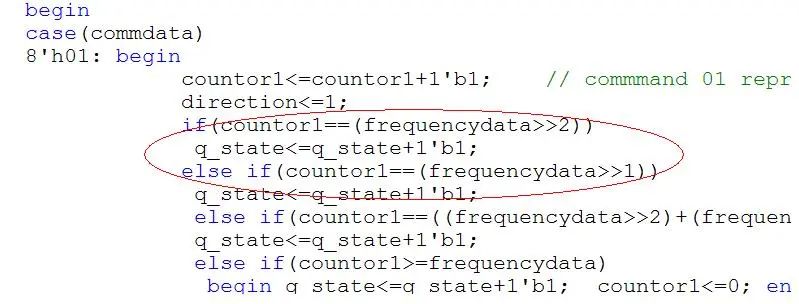

第四:就是看看超差的那个线路,增加一些中间寄存器,或者使用流水线技术,就是将组合逻辑和时序逻辑分开,大的时序逻辑,尽量优化成由很多小的时序逻辑组成一个大的时序逻辑。或者更该程序代码,更该算法。到这一步就是没有办法的办法了。

第五:有些时候在程序中加入一些和项目不相关的代码,也可以提高正常程序的时钟约束余量,估计是不相关代码挤占了一些逻辑单元,使得正常程序在布局布线的时候,选择了其他路径吧。这个办法不固定,瞎猫碰死耗子的事情。

主要就是这几种方法了,首先要选好芯片,这是最重要的,不然为了省成本,最后发现芯片速度不够,很烦人的。

最后提一下有些网友提到FPGA发热厉害的现象,看看你在项目中是不是将unused pin 接地了,这样芯片会发热,最好将unused pin 微上拉,或者设置为输入即可。

编辑:jq

-

FPGA

+关注

关注

1646文章

22072浏览量

619833 -

芯片

+关注

关注

460文章

52624浏览量

442788 -

乘法器

+关注

关注

9文章

213浏览量

38035

原文标题:FPGA时钟约束时钟余量超差解决方法

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

晶振频偏超差?这5个核心因素正在悄悄改变你的时钟精度

FPGA时序约束之设置时钟组

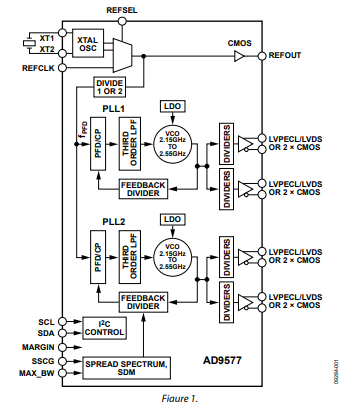

AD9577带双路PLL、扩频和余量微调功能的时钟发生器技术手册

基于FPGA的数字时钟设计

xilinx FPGA IOB约束使用以及注意事项

简述FPGA时钟约束时钟余量超差解决方法

简述FPGA时钟约束时钟余量超差解决方法

评论