小技巧分享:

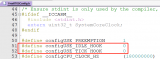

verilog下取对数其实可用$clog2这个系统函数,和自己找代码里面写入function是同样的效果,但是方便的多。这是verilog 2005就开始支持的标准,所以vivado也是支持的,我试了2017.4及以后的版本都可以支持,放心用。

***友情提示:所有支持verilog2005标准的编译器都可以用这个函数,所以使用之前确定编译器是否支持这个标准,还有考虑好后期可移植性的影响

这个是可编译的函数大家可以把她当做宏定义函数一样看待。这操作好玩吗?好玩就赶紧升级编译器吧,新标准总是有很多的改进,如果想了解一些更有意思的东西欢迎关注我,我是最骚的FPGAer。

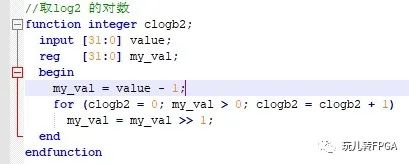

这里附上常用的自定义log2函数,供大家白嫖。图片不清晰尽请担待。

编辑:jq

-

FPGA

+关注

关注

1646文章

22098浏览量

620814 -

函数

+关注

关注

3文章

4388浏览量

65318 -

代码

+关注

关注

30文章

4908浏览量

71248 -

编译

+关注

关注

0文章

680浏览量

34319

原文标题:verilog2005的骚操作之对数函数

文章出处:【微信号:HaveFunFPGA,微信公众号:玩儿转FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

verilog模块的调用、任务和函数

FPGA Verilog HDL语法之编译预处理

Verilog中signed和$signed()的用法

TSC2005EVM和TSC2005EVM-PDK用户指南

Verilog 与 ASIC 设计的关系 Verilog 代码优化技巧

Verilog 测试平台设计方法 Verilog FPGA开发指南

Verilog与VHDL的比较 Verilog HDL编程技巧

使用Phase Lab2024A计算示踪扩散系数的操作步骤

剖析verilog2005的骚操作之对数函数

剖析verilog2005的骚操作之对数函数

评论