1 MAX121оƬ���������ص�

MAX121оƬ��һ���������ӿ���14λģ��ת�����ɵ�·��ADC�����������и���/���ֵ�· ��һ����Ʈ�硢������������ʽ������ѹ����Դ������ת���ٶȿ졢�������ĵס��������ʸߴ�308 ks/s�㣬�����������ѹ��ΧΪ��5V������Ϊ210 mW�������������е������ź��������Ĵ��нӿ�ֱ�ӽӿڣ���������Խ���TTL��CMOS���ź���ƽ��ʱ��Ƶ��Ϊ0.1-5.5MHz����

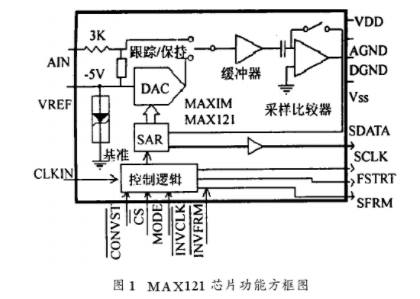

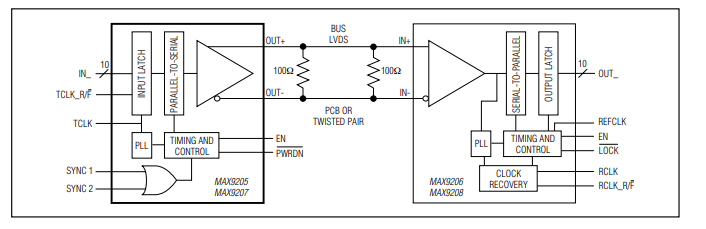

MAX121оƬ�Ĺ��ܷ���ͼ��ͼ1��ʾ������16�ź�20��ģʽ��16����DIP��SO��װ��20���� SSOP��װ���ص����£���

14λ�ֱ��ʣ�2.9 ��Sת��ʱ��/308 ks/s�����ʣ�400 ns����ʱ�䣻�������͵�ʧ�棺78Db SINAD -85Db THD����5V˫�������뷶Χ����ʱ���ܡ�15V�Ĺ���ѹ��210 mW���ģ���������ת��ģʽ��30 ppm/C��-5V�ڲ���Դ����DSP�������ӿڣ�16��DIP��SO��װ��20��SSOP��װ��

��������VDD��DGND 0.3-+6V��VSS��DGND +0.3--7V��AIN��AGND��15V��AGND��DGND ��0.3V���������DGND��CS��CONVST��MODE��CLKIN��INVCLK��INVFRM����-0.3��Vdd+0.3V�������������DGND��SFRM��FSTRT��SCLK��SDATA ��+0.3��Vdd+0.3V���������������ģ�TA=+70 �棩

ǿ�ȳ����������������ܵ�������������������Щ�����Ǽ�������������ζ���ڼ����������£������κ��������������淶�涨�Ĺ��������£���������Ч�ع������ӳ��ڼ����������µ�����ʱ�䣬��Ӱ�������Ŀɿ��ԡ�

2 ������·

MAX121������αȽϼ�������/���֣�T/H����·����ģ���ź�ת��Ϊ14λ����������� �롣��������ӿں��������������������P���������źŴ�������DSP�������ӣ��ڴ����Ӧ����ֻ��Ҫ���ټ�����ԴԪ����T/H��·����Ҫ��ӵ��ݡ�

2.1 ģ����������뱣��

���ݵ�Ч������·����������ADC��ģ��Ƚ����IJ����ṹ���ڲ�������������������磬�Լ�Сת���ڼ���Ҫ��IJɼ�ʱ�䡣ģ������˳���6k�������������䲢����10pF���ݡ�

������ת��֮�䣬����������ͨ������������ӵ�AIN�ˡ���ת����ʼʱ����������AIN�� �Ͽ����������źŲ�������ת������ʱ������������������ӵ�AIN�ˣ����ұ��ֵ��ݸ��� �����ѹ�����ۺ�ʱ��ֻҪת��û�н��У�T/H�ʹ��ڸ���ģʽ����ת����ʼ�Ժ���ģ ʽ����ʱ��ӽ�10 ns�������ӳ٣�����һ��ת������һ��ת���ӳٱ仯�ĵ���ʱ��Ϊ30 ps�����ڶ�������

2.2 ��·ʱ��Ƶ��

MAX121����ʱ��Ҫһ����TTL��CMOS��ƽ���ݵ�ʱ�ӣ�ʱ��Ƶ�ʵķ�Χ��0.1-5.5 MHz��Ϊ����2��ʱ������400 ns�ɼ�ʱ���Ҫ�����ʱ��Ƶ��������5MHz�������ڲ�T/H ��ѹ�½����ʵ����ƣ�����ģʽ��ʱ��Ƶ�ʲ�Ӧ����0.1MHz��

2.3 ������ݸ�ʽ

ת�������16λ���������������ǰ14λΪ����λ������ΪMSB������2λΪ�㡣������� Ϊ�����Ʋ�����ʽ����CLKIN�������أ�������SDATA��ͬ�������

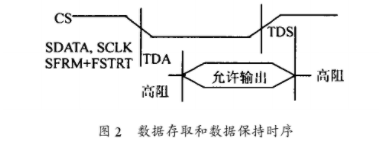

������ݿ���FSTRT����SFRM�������֡��FSTRT��ƽ��Ϊ�ͣ�����MSB1��ʱ�����ڱ�Ϊ�ߡ�FSTRT���½���SDATA�����MSB��

SFRM�������INVFRM=Vddʱͨ��Ϊ�ߣ���Ϊ�͵�ͬʱ��MSB������SDATA�ˡ�16��ʱ�������Ժ� SFRM��Ϊ�ߵ�ƽ��ͨ������ӵ����ֵأ��ɷ�תSFRM�ļ��ԡ�Ҫ��ÿ��ת������Ϊ18��ʱ�����ڣ��Ի����ЧSFRM�����

����м����������ô������ߣ����Բο�ͼ2�����ݴ�ȡ�����ݱ���ʱ��

3 TMS320���ٴ��нӿ�

3.1 �ϵ��ij�ʼ��

������������������ϵ��MAX121���״�ת��������Ч�ġ��ṩ16��ʱ������ʹT/H�������ģʽ���ټ��ϸ���ģʽ�����ݲɼ�����Сʱ��400 ns��ȷ����Դ�Ѿ��ȶ���ÿ1��F��Դ��·���ݵ��ȶ�ʱ����0.5 ms����22��F����Ϊ11ms����

3.2 ����ʱ���������

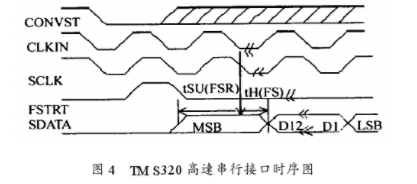

�� �������źŴ������ӿ�ʱ��MAX121�Ĵ���ʱ���������ȡ���ڴ������Ĵ�������������Ҫ �����С����ʱ���ADC��ʱ�������ݵ�����ӳ�ʱ�䡣MAX121�����ַ��������ݶ��봦������ CLKIN��MAX121������ʱ�ӣ���SCLK��ʹ������λ���봦�����Ĵ���ʱ�ӣ�֧���첽���ݴ���ij��ϡ�tSU�Ǵ��������������������Ҫ������ݽ�����Сʱ�䣻tCD��MAX121��CL KIN��SCLK�����ʱʱ�䣻tSC��MAX121��SCLK��SDATA�������ʱʱ�䡣MAX121 ��SCLK��������������Ĵ��нӿڣ���ʱ�ɴ����������ȥ��tCD�������ʹ �ø����ʱ��Ƶ�ʡ�����������£�����ʱ������ٶ�����ʽ���㣺

fCLKIN=1/2��tSU+tSC��

3.3 �������ݴ��нӿ�

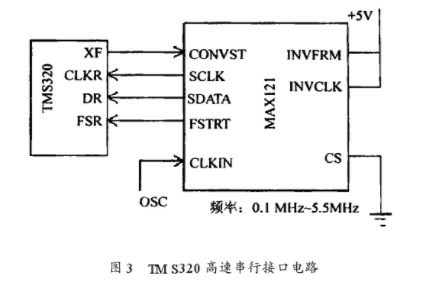

MAX121�������ʹ������������������˾TMS320�ĸ��ִ��нӿ����ӡ����ٽӿڿ�ʹMAX121/TM320ϵͳ����������������ʣ���ʱMAX121�������������ʱ�ӡ�ͼ3ʾ����������� �ӿ���������ߡ�ͼ4Ϊ�ӿڵ�ʱ��ͼ����

MAX121��CLKIN���ⲿʱ������������TMS320��XF0 I/O������MAX121�����Ϊ�ͣ����� һ��ת����TMS320��CLKR������ʱ�ӣ�������Ϊ���룬���� MAX121��SCLK�����������MAX 121��SDATA�����������ʱ�ӵ������ظı�״̬������ʱ���½��أ����ݱ����浽TMS320�� DR����ˡ��������ṩ1/2��ʱ�����ڣ�������TMS320DR���������Ҫ�����ݽ����ͱ���ʱ�䡣 MAX121SCLK��SDATA֮������ʱ����+25ʱΪ65ns������1/2��ʱ��������������Ҫ��Ľ����ͱ���ʱ�䡣

MAX121��FSTRT�������TMS320��FSR���룬�Զ����ݷ�֡��FSTRT������½���ָʾMSB�����ã��ɱ����档����һ��ʱ���½��أ�MSB��������TMS320��ʹ�����ֽӿڣ�TMS320�ɽ���16λ�֣���TMS320���п�������ƼĴ����У�RLEN=01��������14λ���ݱ�ʱ��ͬ������DSP��ͬʱ������λβ���0��

4 ����

�������������ű�Яʽ������ʽ���Ӳ�Ʒ���������࣬MAXIMϵ�в�Ʒ��Ӧ��ҲԽ��Խ�� ����������ϸ������MAX121оƬ�������źŴ������ٴ��нӿڵ�·�����Ӧ�á�ͬʱMAX121���ɵ�·Ҳ������ʶ��ͺϳɡ�DSP�ŷ��ϳɡ�Ƶ�����������й㷺��Ӧ�á�

�༭��jq

-

оƬ

+��ע

��ע

460����

52790�����

445186 -

���ɵ�·

+��ע

��ע

5433����

12194�����

369509 -

CMOS

+��ע

��ע

58����

6058�����

239465 -

TTL

+��ע

��ע

7����

543�����

72318

������������ ��¼

�ǶྦྷXSBERT�����������ӿ����Ի���Ϊ��

MAX9205/MAX9207 10λ������LVDS�����������ֲ�

MAX9259/MAX9260��ý��������·���ṩ��Ƶ���ܺ�ȫ˫������ͨ�������ֲ�

MAX9249��ý��������·������������LVDSϵͳ�ӿ������ֲ�

MAX9268��ý��������·���������LVDSϵͳ�ӿ������ֲ�

DMDоƬ��������ʵ����Ӧ�÷���

DMDоƬ�������������ʹ��

SOCоƬ��������������Ӧ��

�����ӿ�PCB���ָ�ϣ��Ż������벼�߲���

����оƬ��Ӧ�����ij��������������

DRV8332оƬ�����ԵĹ����������ʼ�մﲻ��24V��Ϊʲô��

���������ӿ�(FSI)�ڶ�оƬ�����е�Ӧ��

̽��MAX121оƬ�ڸ��ٴ��нӿڵ�·�е�Ӧ��

̽��MAX121оƬ�ڸ��ٴ��нӿڵ�·�е�Ӧ��

����