在高速PCB设计中,“信号”始终是工程师无法绕开的一个知识点。不管是在设计环节,还是在测试环节,信号质量都值得关注。在本文中,我们主要来了解下影响信号质量的5大问题。

根据目前工作的结论,信号质量常见的问题主要表现在五个方面:过冲,回冲,毛刺,边沿,电平。

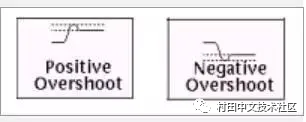

01 过冲

过冲图

过冲带来的问题是容易造成器件损坏,过冲过大也容易对周围的信号造成串扰。造成过冲大的原因是不匹配,消除的方法有始端串电阻或末端并阻抗(或电阻)。

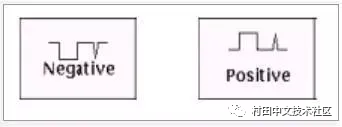

02 毛刺

毛刺图

毛刺作用在高速器件上,容易造成误触发、控制信号控制错误或时钟信号相位发生错误等问题,毛刺脉冲带来的问题多发生在单板工作不稳定或器件替代后出现问题。造成毛刺的原因很多,比如逻辑冒险,串扰、地线反弹等,其消除的方法也不尽相同。

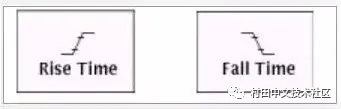

03 边沿

边沿图

边沿速度缓慢发生在信号线上时,会造成数据采样错误。其产生原因通常是输出端容性负载过大(负载数量过多),输出是三态时充(放)电电流小等原因。

04 回冲

回冲图

回冲产生的原因是信号线不匹配或多负载等原因,消除的方法是加匹配电阻或调整总线的拓扑结构。

05 电平

电平图

输入电平幅度不符合要求时,会造成器件输出错误。导致电平异常的原因主要有:输出过载,电平不匹配,三态总线、总线冲突等原因。

扩展

工程师在进行信号质量测试时,应该具备以下三方面的知识:

1)对测量工具(示波器)有清楚的了解,要了解示波器的性能,掌握示波器及其探头的使用,清楚信号质量异常的测试与示波器菜单设置间的配合关系。

2)对异常的信号形式有全面和清楚的认识,对异常信号的异常指标有了解。

3)对被测单板的原理电路有一定的认识和了解,要求能够对信号进行分类,了解板上的关键器件、关键总线、关键信号的信号质量要求和相关时序参数。

责任编辑:lq

-

pcb

+关注

关注

4373文章

23562浏览量

412586 -

阻抗

+关注

关注

17文章

975浏览量

47709 -

信号质量

+关注

关注

0文章

9浏览量

6906

原文标题:高速PCB设计中影响信号质量的5个方面

文章出处:【微信号:murata-eetrend,微信公众号:murata-eetrend】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高速PCB设计挑战 Allegro Skill布线功能 自动创建match_group

高速PCB设计中影响信号质量的5大问题

高速PCB设计中影响信号质量的5大问题

评论