这是《创建 Vitis 加速平台》系列的第 3 篇博文。在前文中,我们讲解了如何创建硬件和软件工程。在本文中,我们将讲解如何在 Vitis 中将所有这些工程封装在一起。

在 Vitis 中加速软件功能(创建内核)即表示创建硬件 IP 核,并使用由此产生的基础架构将此功能连接到现有平台。

为此,Vitis 需要重构平台。Vitis 使用 XSA 来重构 Vivado 工程。随后,它将追加经过更新的硬件,并重新创建 Vivado 工程。

其它所有一切都保持不变,当然比特流和生成的内核应用除外。因此,启动镜像不能保持不变。而是由我们提供 BIF 文件,并在其中包含镜像占位符用于在 Vitis 中创建这些镜像。

此外,为了能够执行内核,我们需要为目标硬件执行交叉编译。此处使用的是 PetaLinux 中创建的 sysroot。

准备镜像

为了便于使用,我在此对平台文件进行了组织,但这并非必要步骤。重要的是,请牢记创建 BIF 文件时的启动镜像位置,因为我们使用的是占位符。

mkdir -p sw_comp/src/a53/xrt/image mkdir sw_comp/src/boot

将 image.ub、boot.scr 和 rootfs.cpio.gz 从 PetaLinux image/linux 文件夹复制到 sw_comp/src/a53/xrt/image

将 bl31.elf、uboot.elf、zynqmp_fsbl(已重命名为 fsbl.elf)和 pmufw.elf 从 PetaLinux image/linux 文件夹复制到 sw_comp/src/boot

创建 BIF

BIF 文件在 bootgen 中用于创建 SD 启动镜像。

其中包括 BOOT.BIN 文件中所有分区的位置。以下提供了一个模板。

此处请务必注意,我们只提供占位符文件名,而不提供实际文件名。工具将添加指向这些文件的路径。因此,我建议将所有这些文件保存在相同启动文件夹内。zcu104_base 将用作为平台名称。

the_ROM_image: { [fsbl_config] a53_x64 [bootloader]

将 linux.bif 复制到 sw_comp/src/boot

创建 init.sh 脚本

启动时将运行此脚本以进行 XRT 设置,并将平台名称传递到 ZOCL。

将 init.sh 复制到 sw_comp/src/a53/xrt/image

cp ./platform_desc.txt /etc/xocl.txt export XILINX_XRT=/usr

将 init.sh 复制到

sw_comp/src/a53/xrt/image

创建 platform_desc.txt

这样即可将平台名称传递到 XRT。此处名称应与 Vivado 中提供的平台名称匹配:

zcu104_base

将 platform_desc.txt 复制到

sw_comp/src/a53/xrt/image

创建 QEMU 文件

Vitis IDE 支持软件仿真和硬件仿真。QEMU 即可用于执行此操作。但我们需要传递 QEMU 机器详细信息。

针对 PMU,需使用 pmu_args.txt 执行此操作

-M microblaze-fdt -device loader,file=

将 pmu_args.txt 复制到 sw_comp/src/boot

此外还需要通过 qemu_args.txt 传递 PSU 机器详细信息:

-M arm-generic-fdt -serial mon:stdio -global xlnx,zynqmp-boot.cpu-num=0 -global xlnx,zynqmp-boot.use-pmufw=true -net nic -net nic -net nic -net nic -net user -m 4G -device loader,file=

将 qemu_args.txt 复制到

sw_comp/src/boot

在 Vitis 中封装平台

启动 Vitis 并选择“创建平台工程 (Create Platform Project)”:

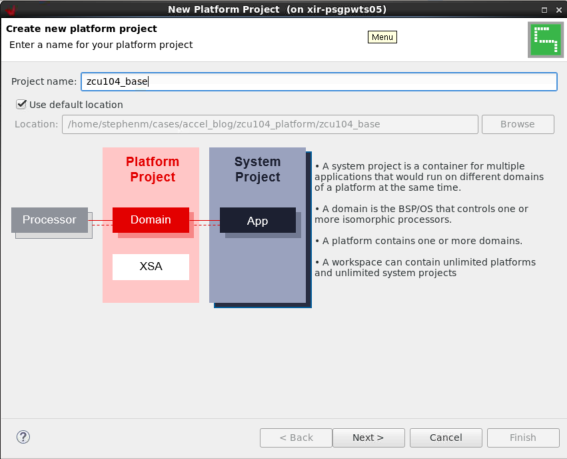

使用 BIF 中所提供的名称:

选择“根据硬件规范 (XSA) 创建 (Create from hardware specification (XSA))”:

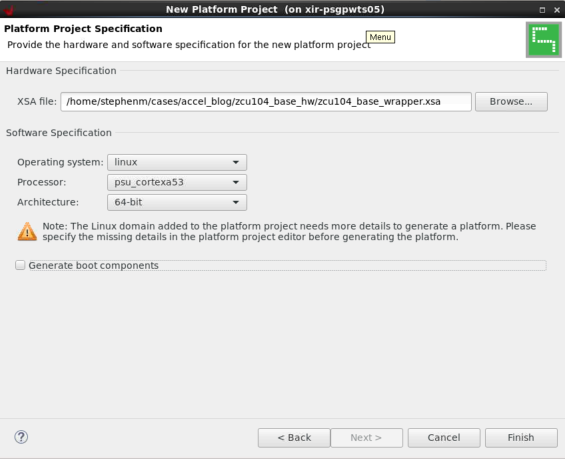

针对操作系统选择 Linux,然后取消勾选“生成启动组件 (generate boot components)”,因为在 PetaLinux 中已创建这些组件:

注:此处警告信息仅用于声明需添加 sysroot。

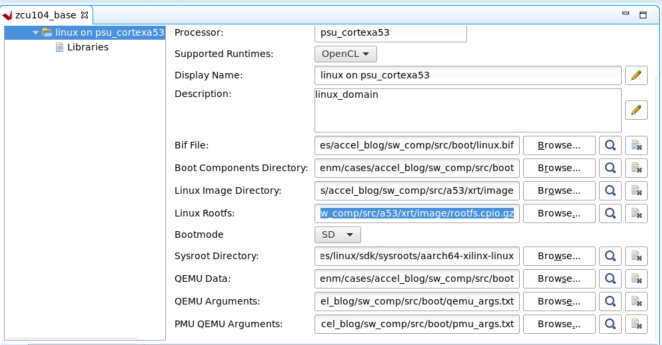

填入上一篇博文中创建的软件镜像:

然后执行构建:

完成此操作后,平台将置于 exportzcu104_base.... 至此大功告成。

原文标题:创建 Vitis 加速平台第 3 部分:在 Vitis 中封装加速平台

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

封装

+关注

关注

128文章

8741浏览量

145735 -

Vitis

+关注

关注

0文章

150浏览量

7979

原文标题:创建 Vitis 加速平台第 3 部分:在 Vitis 中封装加速平台

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何在Unified IDE中创建视觉库HLS组件

全新AMD Vitis统一软件平台2025.1版本发布

使用AMD Vitis Unified IDE创建HLS组件

如何使用AMD Vitis HLS创建HLS IP

如何在基于Arm Neoverse平台的CPU上构建分布式Kubernetes集群

GPU加速计算平台的优势

使用AMD Vitis进行嵌入式设计开发用户指南

AMD Vitis Unified Software Platform 2024.2发布

U50的AMD Vivado Design Tool flow设置

GPU加速计算平台是什么

如何在采用 SOT563 封装的 TPS56x242-7 上实现更良好的热性能

如何在SOT-563封装和SOT-236封装之间实现共同布局

如何在Vitis中封装加速平台?

如何在Vitis中封装加速平台?

评论