本应用笔记介绍了具有FIFO(先进先出)设置说明的UARTJ串行接口控制,以及使用示例的概述。该文档还描述了使用环境,例如电路图,开发环境,所使用的软件以及带有流程图,主要处理,接收/发送中断处理和寄存器设置的示例应用程序。

概述

本应用笔记举例说明了UARTJ的用法示例。

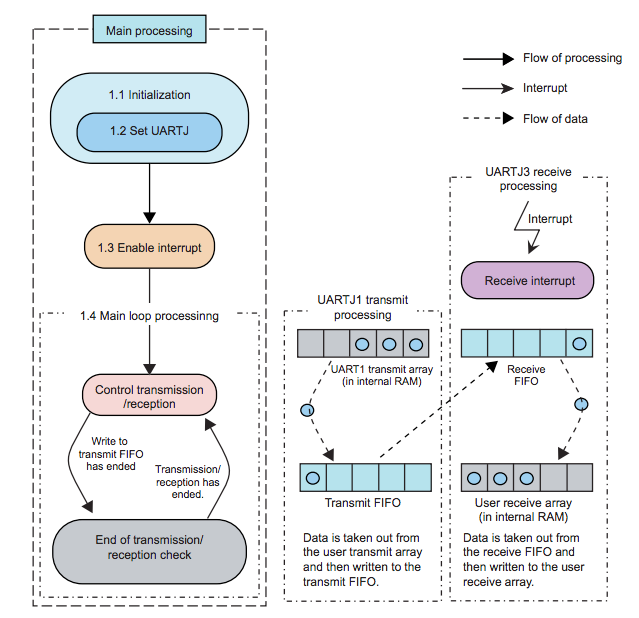

该示例程序对V850E2 / MN4微控制器进行了基本的初始设置,例如时钟频率的选择和端口I / O的设置。初始化结束后的主要处理将执行UARTJ1和UART3之间的串行通信。UARTJ1发送数据,而UARTJ3接收数据。

该软件的要点如下所示。

UARTJ软件处理

主循环处理

主循环处理主要分为两个。它反复控制发送/接收,并等待发送/接收结束。如果在设置了UARTJ的操作之后将发送数据写入URTJnFTX寄存器,则将数据写入发送FIFO。存储在发送FIFO中的数据被传送到发送移位寄存器,然后通过TXDnF引脚开始串行发送。

在此示例程序中,发送UARTJ1发送16字节数据,接收UARTJ3从UARJ1接收16字节数据。内部RAM具有16字节(一个字节(一个块数据)?16)的用户发送阵列来存储发送数据,而16字节的用户接收阵列来存储接收数据。

当在主循环处理期间发生发送/接收中断或状态中断时,将执行相应的中断处理。在此示例程序中,中断在以下列出的时间发生。

发送中断:当发送FIFO为空时

接收中断:当接收FIFO满时

状态中断:在接收或发送过程中发生错误时

发展

必须安装下面列出的通行费才能运行示例程序。

CubeSuite +

瑞萨电子的集成开发环境CubeSuite +提供了用户开发应用程序所需的各种软件开发工具。用户可以在各种开发阶段无缝,轻松地使用这些工具,包括编码,汇编,编译,使用仿真器或模拟器进行调试以及Flash编程。

MINICUBE

MINICUBE是瑞萨电子的通用在线仿真器,它采用JTAG接口系统。它允许用户调试板载真实处理器,并提供高度透明和稳定的仿真功能。需要适配器才能将TB板连接到MINICUBE。

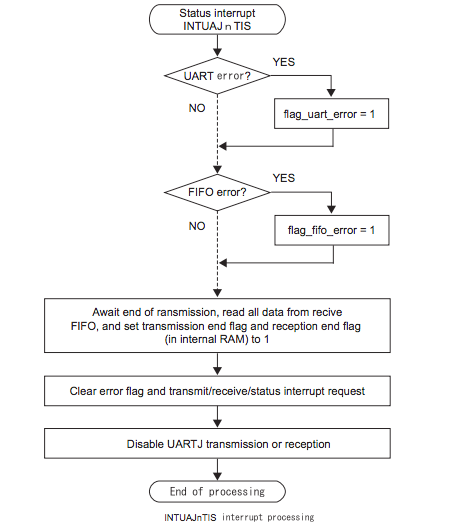

状态中断处理

在发送/接收过程中发生错误时,会发生状态中断请求。

数据一致性错误

超时错误

取景错误

奇偶校验错误

溢出错误

溢出错误

状态中断处理

当在发送/接收期间检测到错误时,URTJnSTR1和URTJnFSTR1寄存器中的相应错误标志将设置为1。然后,UARTJ状态中断处理将清除发送/接收FIFO。通过等待相当于传输16字节数据所需的时间来清除发送FIFO。通过从中读取所有接收到的数据来清除接收FIFO。内部RAM中的发送标志和接收标志设置为1。通过URTJnSTC和URTJnFSTC寄存器清除SFR错误标志,并清除发送/接收中断请求或状态中断请求。UARTJ1和UARTJ3暂时停止并返回主循环(在主循环处理中恢复发送/接收)。

编辑:hfy

-

微控制器

+关注

关注

48文章

7993浏览量

157175 -

寄存器

+关注

关注

31文章

5451浏览量

125592 -

串行通信

+关注

关注

4文章

592浏览量

36473 -

接口控制

+关注

关注

0文章

11浏览量

8852

发布评论请先 登录

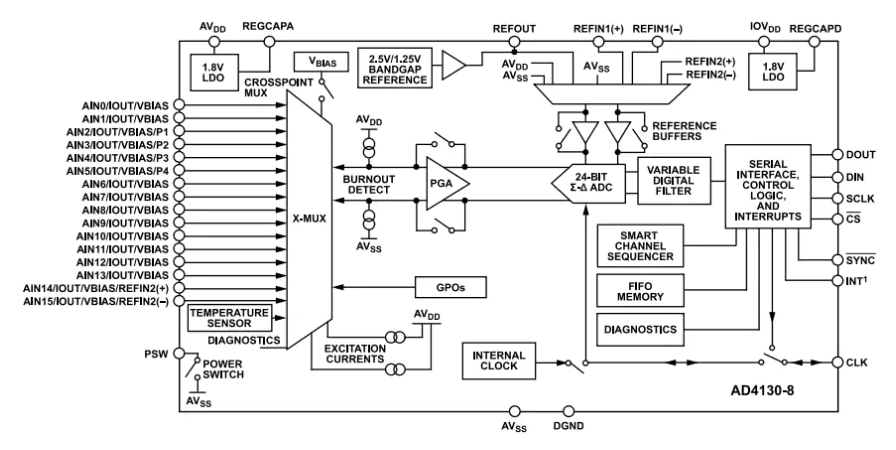

Analog Devices Inc. AD4130超低功耗24位Σ-Δ模数转换器特性/应用/框图

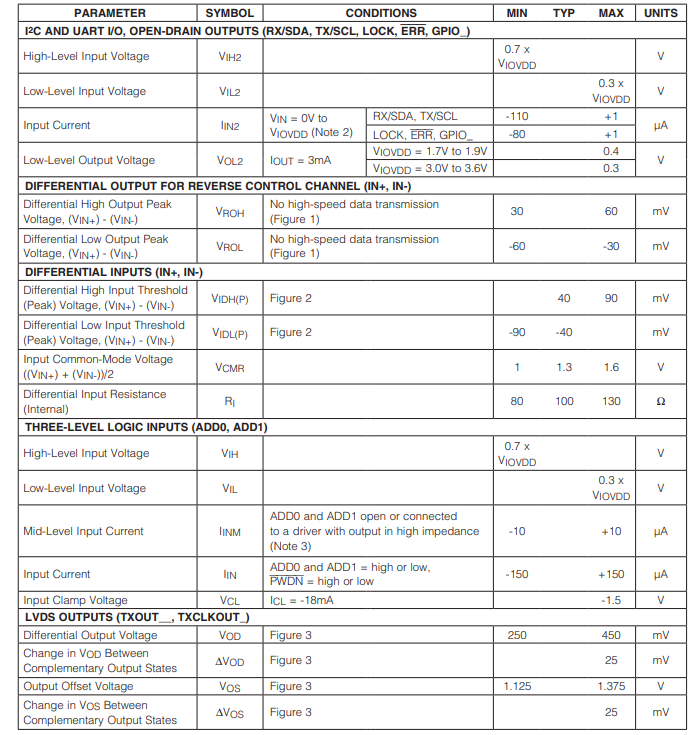

MAX9268多媒体串行链路解串器,具有LVDS系统接口技术手册

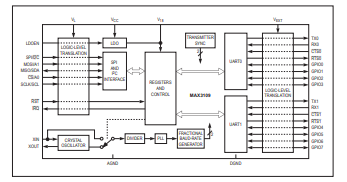

MAX3107SPI/I?C UART,具有128字FIFO技术手册

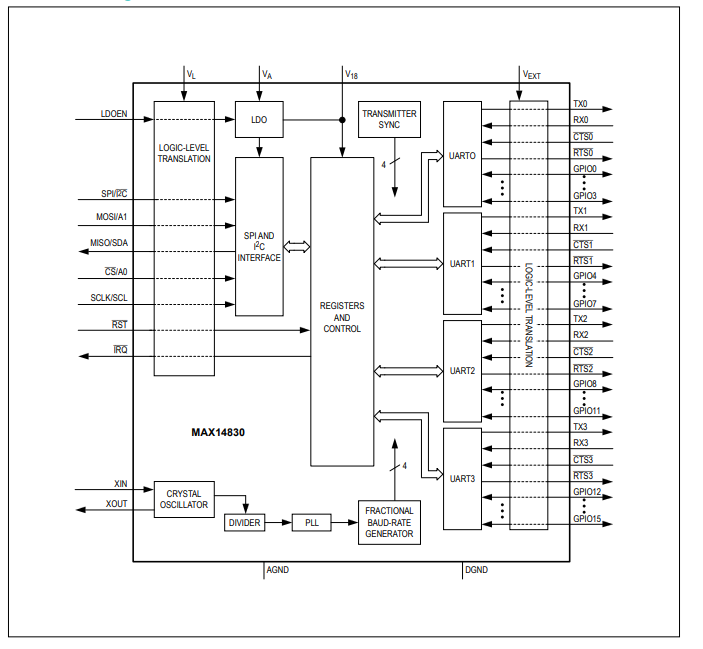

MAX14830四通道串行UART,具有128字FIFO技术手册

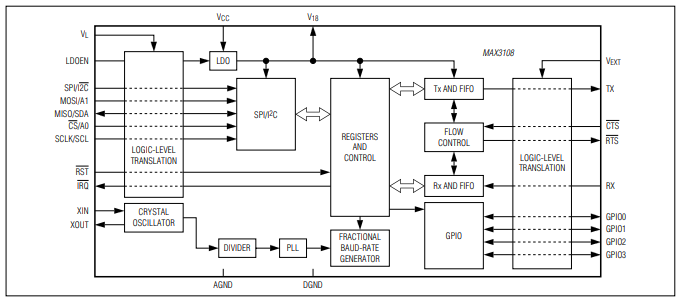

MAX3108 SPI/I?C UART,具有128字FIFO,WLP封装技术手册

基于FPGA的FIFO实现

【瑞萨RA2L1入门学习】+Uasrt输出

SDRAM控制器的设计——Sdram_Control.v代码解析(异步FIFO读写模块、读写SDRAM过程)

使用SCL编写FIFO功能块

具有FIFO(先进先出)设置的UARTJ串行接口控制

具有FIFO(先进先出)设置的UARTJ串行接口控制

评论