1. ú¯îå

ARMv8È´çÝú¯ø£ÆÅAüçêÅȘ¥ÇARMv8-AÈˋ¥É¿¿È˜òúARM¿¨ùƒöˆôºæÐÅôÅÒúµÑ½øÄÅôèÒ¥óçáØ£¡—¥É¿¿È˜òú§■20áõâÇȘARM¥É¿¿ÝðÑ₤æŸÇµçáØ£ÇöÀÈù■Ø»àŠçáExecution StateÀÂException LevelÀÂSecurity StateçàÅôäÄÅåȘØîƒÙ¤ëöØûúÑåƒèçáARM¥É¿¿çáàüøˆÈ˜ÆŤÉǵýŸƒÁêùÀÈ

Ø·ÇùȘ݃öáÇÆARMv8-AýºèºçáÝ°ƒ¯¢ˆò¥È˜Ñåù■§½ÅÅØ£¡—¥·çËçá§ÕèÉȘò¿Çµ¥ØÇÆí«äÍèüȘÑåARMv8ÆÅØ£¡—¥·çËçáêù§ãÀÈ

2. Ý°ƒ¯

ÆÅØ£çÐòú¢èØåàñÑ´çáȘARMçÛèºòÝȘÑåIntelø¼ç¥çáPCòÅ°ÀȘû£ÆÅÈ´Øýý£¡ØÆÅÈˋØ£çÐçÐçáñúñøøÛüŠÀÈ柰¾çáARMv4È´ARM7üçêÅÈˋȘç§æŸ§■çáARMv7È´Cortex-A,-M,-RüçêÅÈˋȘѥòúíŠÑå¿Î¤áÝà§üû¶¡ÅçáØóÑ₤èÒÝ¡çáȘƒëÅåáÉѽîåȘ£ªÆÖARMÇÎâÚó¼çáèÒݡȘò¥øíößñ´¤ëPCüÁäÃýÂôÜÀÈ

ç¨ÇÆARMv7¢ˆò¥È˜úÕ¢—¢ˆò¥ÆÅÅˋæˆÝðȘARMçáòÅ°À¢ˆò¥âˋí¿ç§ØóÑ₤èÒÝ¡øÛëãçáóðù■êšÆ·È˜íãØýòúARMv7£ÛñøöˆAÈ´ApplicationÈˋÀÂRÈ´Real-timeÈˋ¤ëMÈ´MicrocontrollerÈˋ໡—üçêÅçáåÙطȘóðòçøòƒëòú໡—ü¡ñøòÅ°ÀȘóðøÅçáAüçêÅȘƒëòúíŠÑåÅåáÉ؈úµ§ü¡ÔçáÆÎÆûÀÈ

äÄÝÞòúåÖCortex-A9øÛ¤µÈ˜ARMçáÇÎâÚÅåáÉÆŤÉǵçáäáÔȘ§Ë§Ëçáö■Ø»êùØ£ÅˋPCÆû£ÏÀÈØ·Çù£ªÆÖARMçáâÁPCýºóñȘàÓó§¯ÍçÓáåȘ¢ˆò¥Çµê¢Æ¢üøÀÈÇùòÝȘARMçáÇÎâÚáÉêÎȘØîƒÙÆÅ£º£ÃÆÎÆûÆÖóðù■êšÆ·êùȘàÓóµØçèÒÝ¡ÀÂñ±öþó¼çàȘçÝà£È˜óðÆéòóØâà£òúçë¿Î¤áÀÈ

ÆŠÇùë˜òÝȘÅôçáú¼òóí»åÖåëáÞȘø¼Øˆ¯■â´ÇµáÖÇÌÈ´Large MemoryÈˋÀÂÅÕáã£₤È´VirtualizationÈˋ¤ë¯ýà¨È´SecurityÈˋÀÈVirtualizationåÖARMv7èüØîƒÙÆÅ¥·çËçáÆý¥±òçüøȘSecurityØýÆÅ¢èáÉ£ªÆÖçÝú¯¥É¿¿âˋí¿È˜ö´ÆÅLarge memoryçáÅÒúµÈ˜ÆÅçÐ¥˜òøÀÈ

ÆèÆÖÇÎâÚó¼ÅåáÉå§âÇå§ú¢È˜åùÅÅÆÖóðèüçáàÚ¥±ØýâÇ姡ÇåÆȘ¡ÇåÆç§çËØ£ÆÎÆûÑåáÖÇÌçáÅÒúµ¢èáÉ°˜°—32-bit¥É¿¿ùªáÉøÏ°øçáæŸÇµáÖÇÌÈ´4GÈˋȘíãƒëòúLarge memoryÅÒúµçáóÞØ·ÀÈý£¿»È˜¤µâÇçáCortex-A15È´ARMv7¥É¿¿Èˋë´¿»Large Physical Address Extensions (LPAE) ¥¥ò¾È˜¢èØåøÏ°ø¡ÔÇÿ40bitsçáöÿâÚçÄøñ¢í¥ðÀÈç¨òÉüßÆÖ32-bitçáø¡êŸ¥₤ȘÅÕáãçÄøñ¢í¥ðØâƒèø£ÆÅ32bitsÈ´4GÈˋȘàÓ¿«ÆÅÆÎÆûÅÒ؈¡■ǵçáÅÕáãáÖÇÌȘå¾ûǯšÈ¢ø£áÉÑ´ØÍØ£¡—Åôçá¥É¿¿È˜ò¿Æû64-bitçáø¡êŸ¥₤È´Øý¥ÇöØûú°ÈùççáARM64ÈˋÀÈ

¤êößØèöòȘåÖüø§æÑöȘÅÒ؈°˜¿»4GÅÕáãáÖÇÌçáÆÎÆû°Àƒ¯È˜òúñú°ÈèìçáÀÈç¨ARM£¿òúÑ´ØÍêùØ£¡—Åôçá¥É¿¿--ARMv8ȘöˆòýûÇáÄÈ¢üôûÌòúARMçá§ãòëÈ´ø£ÆÅö¯ÇµçῨùƒýéÆÅö¯ÇµçáâÚáŸÈÀÈˋȤ

Trends. ThatÀ₤s really what ARM has to look at when defining a new architecture. That is the nature of our business, we need to look a long way forward, and plan.

çÝà£È˜ARMv8ýÂý£§—§—òúöˆêù§ãƒ—ÅÕáãçÄøñçáöòäãȘù■Øý؈§ãƒ—üøÆťɿ¿çáØ£ÅˋöòäãÀÈý£¿»È˜ÅôçáöòäãÆøâÇêùȤأ¡—Åôçá¥É¿¿È¢Æû£ÏöˆòýûÇ؈ò¿ÆûÅôçá¥É¿¿È¢Ø·ÇùȘARMv8çáÑ´ØÍȘÝÄÅŠüàôºæÐàÓüôú¯äÃä¾¥±È¤

1ÈˋÑåèü¥ÌàïÀÈ

2ÈˋáɧプüøÇ̥ɿ¿çáØîøˆöòäãÀÈ

3ÈˋüÁÝàüøÇ̥ɿ¿È˜ÝÄÅŠƒÔÝ¡Æéòóû¼üåçáÅôäÄÅåȘááéôàÚ¥±ÇÆâÇý£ò¿ÆûíãÅˋÅôäÄÅåÀÈ

ØåèüƒëòúARMv8-aýºèºçáÝ°ƒ¯È˜ØýòúARMv8-a¥É¿¿øÛùªØåòúÀ¯íã¡—ÀÝîªæÆçáøݧÆåÙØ·ÀÈáúûÇç§çæòúòýûÇîªæÆáÄÈ¢öØûú¥äŽ§ÕèÉÀÈ

3. ARMv8-a¥É¿¿¥·§Õ

£ªÆÖèüûÌçáú¯äÃä¾¥±È˜ARMv8-a¥É¿¿çáø¼ØˆäÄÅå¯■â´È¤

1ÈˋÅôå—Ø£äæ64-bitçáø¡êŸ¥₤Ș°óæ¼A64ÀÈ

2ÈˋÆèÆÖÅÒ؈ü·ú¯¥ÌàïARMv7ȘùªØåë˜òÝøÏ°øüøÇÌçá32-bitø¡êŸ¥₤Ș°óæ¼A32¤ëT32È´Øý¥ÇöØûúòšüÊçáARM¤ëThumbø¡êŸ¥₤ÈˋÀÈ

3ÈˋÑ´ØÍAArch64¤ëAArch32ê§äæåùÅÅ£ñƒ°È´°óæ¼Execution stateÈˋȘñøÝÞøÇÅÅ64-bit¤ë32-bitø¡êŸ¥₤ÀÈàÚ¥±¢èØååÖÅÒ؈çáòݤ·È˜úÅ££Execution stateÀÈ

4ÈˋAArch64æŸÇµçá¡áÑ₤Șò¿ÆûÅôçá¡éáŸÈ´exception levelÈˋȘøÄÅô§ãòëêùprocessor modeÀÂprivilege levelçà¡éáŸÈ˜ƒÔäÍ¢èýö¢¥çÖ4íôçá§ÕèÉÀÈ

5ÈˋåÖARMv7 security extensionçᣪÇÀèüȘÅôå—security modelȘøÏ°ø¯ýà¨üÁ¿ÄçáÆÎÆûÅÒúµÀÈ

6ÈˋåÖARMv7 virtualization extensionçᣪÇÀèüȘäÿˋëõí«çávirtualization¢·¥ÉȘÇÆÆý¥±èüøÏ°øÅÕáã£₤ÀÈ

4. AArch64 Exception level

Exception levelȘòúARMv8-aØ»àŠçáØ£¡—Åô¡éáŸÈ˜ÆûÆÖí«¤üøÛú¯¥É¿¿øÅprocessor mode¤ëprivilege levelüÁ¿Äçá¿ÎáÉÀÈ

4.1 ARMv7øÛú¯çáòçüø

öØûúøˆçâȘØåú¯çáARM¥É¿¿È˜ÇÎâÚó¼¢èØå¿Êæ¼åÖÑÁøøáÈò§È´°óæ¼processor modeÈˋüôȘ¯■â´UserÀÂFIQÀÂIRQÀÂAbortÀÂUndefinedÀÂSystemçàȘøÛùªØåÇÌåÖý£ë˜çááÈò§È˜ø¼ØˆÆÅ2¡—ñ§ûÌçᢥôúȤ

1Èˋý£ë˜çáÇÎâÚó¼áÈò§È˜ÆÅý£ë˜çáÆý¥±ñûöòà´üßȘ°óæ¼privilege levelÀÈ

ø¼ØˆÆÅ2¡—levelȘprivilege¤ënon-privilegeÀÈóðøÅø£ÆÅUseráÈò§ò¶ÆÖnon-privilege levelȘóðù■ƒªòúprivilege levelÀÈ

¯ýà¨óÞ¥«È˜ÇµÑÁò»òݤ·È˜àÚ¥±Ñ¥åùÅÅåÖUser modeÀÈØ£çˋÅÒ؈óðù■ýìæ¼È˜å·ÅÒ؈úÅ££ç§üÁÆÎçáprivilegeáÈò§üôÀÈíãòúæŸåÙò¥ÀÂæŸóÆùÄçá¯ýà¨ù¥üŠÈ˜çÝà£È˜ø£ñ⃻æÆȘý£ñâÅÀàùÀÈ

2ÈˋíãÅˋÇÎâÚó¼áÈò§È˜°»UseráÈò§ëãȘóðù■áÈò§£ªÝƒèü¤ë¡¼âÁØš°ÈأأÑåÆÎÀÈѽý£ë˜çááÈò§È˜Ñ¥ÆÅØ£Åˋæ奤ÑâÆÅçá¥áÇÌó¼È˜â»àÓR13(SP)ÀÂR14(LR)çàçàȘ¢èØåò¿áÈò§úÅ££¿»°äÈ´ØýòúØš°ÈÇÎâÚ¿»°äÈˋ¡■öˆ¡ÔÅÏÀÂÝÐâ«ÀÈ

4.2 ARMv7-açáòçüø

ARMv7-a£ªÝƒÝÈê¶êùøÛú¯çáèÒ¥óȘý£ë˜øÛÇÎȘ§¨privilege levelû■û«êùȘ°óæ¼PL0¤ëPL1È´ØýÅÚáºýôç§êùȘ¤µâÇ°—üøêùPL2ȘÆûÆÖÅÕáã£₤âˋí¿È´Virtualization ExtensionÈˋÀÈ

êÚëãȘ嗥Æêùꧡ—áÈò§È¤Monitor¤ëSupervisorȘñøÝÞÆûÆÖsecurityâˋí¿¤ëvirtualizationâˋí¿ÀÈ

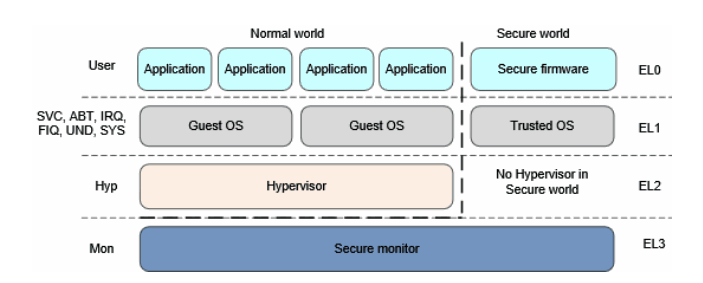

4.3 ARMv8-açáòçüø

¢èáÉARMv8-açáèÒ¥óíÔƒ¾çûøÛú¯çáèÒ¥óÆÅÅˋˆÁôȘƒë¯îprocessor modeçá¡éáŸàËç¶È´£·íÔùççÙ£₤ÈˋêùȘàÀѽǺøÛçáòú4¡—¿äÑ´çáException levelȘ¥·°óEL0-EL3ÀÈë˜òÝȘØýçÙ£₤êùprivilege levelçá¡éáŸÀÈException level݃èÚƒëØîƒÙ¯■¤ûêùprivilegeçáÅéüÂȘ¥ÇELnçáprivilegeùÌæénçáå—ǵѽå—ǵÀÈâÁùóçÄȘ¢èØ姨EL0¿Õò¶ÆÖnon-privilege levelȘEL1/2/3ò¶ÆÖprivilege levelÀÈ

íãÅˋException levelçáüøòçØãØÍòúÈ´àÓüôë¥È˜üगôåSecure modelÆÅ¿ÄçááÖàïÈˋȤ

ARMv8-a Exception levelÆÅ¿Äçáùçû¼àÓüôȤ

1ÈˋòæüàÅÒ؈æÂØãçáòúȘAArch64øÅȘØîƒÙû£ÆÅUserÀÂSVCÀÂABTçàÇÎâÚó¼áÈò§çá¡éáŸÈ˜ç¨ARMv8ÅÒ؈ü·ú¯¥ÌàïȘåÖAArch32øÅȘƒë¯îíãÅˋÇÎâÚó¼áÈò§mapç§êù4¡—Exception levelÀÈ

2ÈˋApplicationö£ÆÖäÄà´çà¥ÑæŸçëçáEL0ȘGuest OSÈ´Linux kernelÀÂwindowçàÈˋö£ÆÖEL1ȘäÿˋÅÕáã£₤øÏ°øçáHypervisorö£ÆÖEL2È´¢èØåý£òçüøÈˋȘäÿˋSecurityøÏ°øçáSeurity Monitorö£ÆÖEL3È´¢èØåý£òçüøÈˋÀÈ

3Èˋø£ÆÅåÖØš°ÈñÂèºòÝÈ´£·íÔØš°ÈÇÎâÚñç£ÄòÝÈˋȘýéáÉúÅ££Exception levelÈ´íãØýòúException levelçáû■û«åÙطȘöˆêùÇÎâÚØš°ÈÈˋÀÈçÝØš°ÈñÂèºòÝȘÆÅê§øøîÀåþȘëÈê¶åÖçÝú¯çáELȘ£·íÔä½æˆç§¡■¡ÔçáELȘELý£áɧç¥ÑÀÈë˜îªÈ˜Øš°ÈÇÎâÚñç£ÄòÝȘØýÆÅê§øøîÀåþȘëÈê¶åÖçÝú¯ELȘ£·íÔç¼ç§¡■çëçáELÀÈ

æÂ1ȤÆÅ¿ÄARMv8-aØš°ÈÇÎâÚçáƒÔäÍü¡§ÖȘ£ÃåÖóðù■öáíôøÅûÒò—ÀÈ

5. security model

ARMv8-açásecurityáÈÅ룪݃îÄÆûêùARMv7 security extensionçáù¥ôñȘø¼Øˆá¢çáÝÈ£ÊØ£Åˋ¯ýà¨ÆÎÆûçáò»ƒïȘâ»àÓøÏ¡ÑçàÀÈù■ý£ë˜ÆÖprivilege levelçààÚ¥±ôÔ¥ÙèüçáÝÈ£ÊȘѽòúØ£øøöÿâÚèüçáú½¡¶È˜¥Çý£ë˜securityæÇä˜üôȘ¢èØåñûöòçáöÿâÚáÖÇÌòúý£ë˜çáÀÈ

ARMv8-a¥É¿¿ÆÅꧡ—security stateÈ´ýö¢¥èüûÌë¥ó˜ÈˋȘSecurity¤ënon-SecurityÀÈø¼Øˆçá¿ÎÅÏòúöÿâÚçÄøñçáú½¡¶È˜Ø奯أÅˋsystem control¥áÇÌó¼çáñûöò¢ÄøóȤ

åÖSecurityæÇä˜üôȘÇÎâÚó¼¢èØåñûöòùªÆÅçáSecure physical address spaceØ奯Non-secure physical address spaceÈ£

åÖNon-securityæÇä˜üôȘø£áÉñûöòNon-secure physical address spaceȘúØý£áÉñûöòSecure system control resourcesÀÈ

6. virtualization

Æý¥±ÅÕáã£₤¯■â´ø¡êŸ¥₤ÅÕáã£₤ÀÂØš°ÈÇÎâÚÅÕáã£₤ÀÂMMUÅÕáã£₤ÀÂIOÅÕáã£₤çàÑÁ¡—ØÕäãȘÝà§ü¡ÇåÆȘíãâÿüàý£ûÒò—êùÀÈ

7. æɧÃ

݃ö᥷ç˧ÕèÉêùARMv8-aøÅçáØ£Åˋ¡éáŸÈ˜¤µÅ½öáíô§¨£ÃøÄçпÄæÂØš°ÈÇÎâÚáÈÅëÀÂsecurityáÈÅëÀÂvirtualizationáÈÅëÀÈ

ÝÁ¥ÙȤhfy

-

ÇÎâÚó¼

+¿ÄæÂ

¿ÄæÂ

68öáíô

19935ð₤ââê¢

236353 -

ARM

+¿ÄæÂ

¿ÄæÂ

134öáíô

9373ð₤ââê¢

378681 -

ARMv8

+¿ÄæÂ

¿ÄæÂ

1öáíô

35ð₤ââê¢

14489 -

ÅÕáãáÖÇÌ

+¿ÄæÂ

¿ÄæÂ

0öáíô

78ð₤ââê¢

8272

ñÂý¥óâôÜúŠüà çúô¥

ñèäÖD2000 opsçÓáåýºóñ¿Ì¡þùçû¼òÕ

ë˜Ø£ùÛó§çá RISC-V ¥É¿¿çá MCUȘ¤ë ARM ¥É¿¿çá MCU üÁÝàȘåùÅÅùìÑààÓ¤öÈ¢

RISC-V¥É¿¿CPUçáRAS§ãƒ—ñ§¯¡

åÖIAR Embedded Workbench for ArmøÅò¿ÆûArm Cortex-R52 NEON

Arm ¿¨ùƒûÌü· PC òÅ°Àçá ?Arm Niva? èŸÑà§ãÑê

STC8H çË󘣺 + RA8889/RA6809ȤøÄÅôÑ´ØÍúÑàŠò§Çˢħ££Ë_¡Ôê¼°ˋÀÂçëîÆ°ìÀÂêУªÇÀçáàù£º§ÓûÌÈ´Ø£Èˋ

ARMæŸú¢°˜Çµ¤ùCortex-X925ÆŠÅÀûæű§ðO1çáèŸÑà§ãö—

ArmñÂý¥£ªÆÖArmv9¥É¿¿çáCortex-A320ÇÎâÚó¼

£ªÆÖArmv9¥É¿¿çáMediaTekäšÓÃ8400ØóÑ₤Ńó˜öòòâ

Ø£öáüõ§ãArm¥É¿¿Armv9.6-AøÅçáæŸÅô¿ÎáÉ

ARM¥¥ò¾òúòýûÇÈ¢¿ºáÖÆÅááÅˋARM°Ï¥ØáÄȢأóÞâÇêù§ãØ£üôÈÀ

Armv9 CPUøÅSVE2çáòç¥òÆûâ»

àÓ¤öîÏü¯ARMÈ¢

ARM COREøÏ°øøÅÑüúÑäæôÞÈ¢GICøÅÑü¢Äøóó¼øÏ°øøÅÑüúÑäæôÞÈ¢

ARMøÄÅôÑ´ØÍARMv8Åô¥É¿¿È˜ARMv8Åô¥É¿¿äÄÅå§ãùç

ARMøÄÅôÑ´ØÍARMv8Åô¥É¿¿È˜ARMv8Åô¥É¿¿äÄÅå§ãùç

óâôÜ