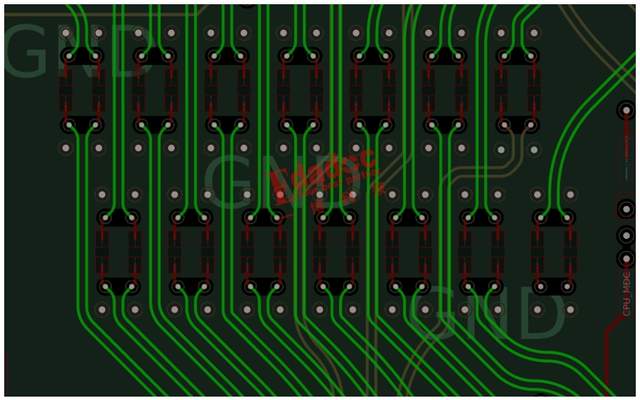

可以使用hyperlynx?专业的pads或pads+标准轻松定位和修复pcb串扰问题。从PCB布局导出设计后,在批处理模式下运行模拟和/或交互模式以识别潜在的串扰问题。Walker BoardSim耦合区域使您能够准确定位网络耦合最多的区域。同时,导出net linesim对耦合部分进行编辑,消除串扰问题。然后,确定要更改的布局。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pcb

+关注

关注

4372文章

23554浏览量

412045 -

耦合

+关注

关注

13文章

598浏览量

101784 -

设计

+关注

关注

4文章

822浏览量

70666

发布评论请先 登录

相关推荐

热点推荐

高速AC耦合电容挨得很近,PCB串扰会不会很大……

觉得恐惧了?

恐惧?恐惧啥呢,那当然是大家都会担心对与对之间的串扰啊,在满足物质生活之后(能塞到PCB板之后),肯定要慢慢开始注重精神生活了!鉴于有不少的粉丝,包括公司设计部的同事都来问过Chris

发表于 07-22 16:56

NEXT(Near-End Crosstalk,近端串扰)

一、什么是NEXT(近端串扰)? NEXT(Near-End Crosstalk,近端串扰)是指在线缆传输信号时,靠近发射端处,相邻线对之间因电磁干扰所产生的

OLI-P——分布式偏振串扰测量利器

在保偏光纤系统中,偏振串扰是导致性能劣化的核心因素之一。传统偏振检测手段仅能获得链路整体消光比,而分布式偏振串扰测量通过连续、高精度地捕捉整条光纤链路的偏振耦合分布,成为保障系统可靠性

电子产品更稳定?捷多邦的高密度布线如何降低串扰影响?

在高速PCB设计中,信号完整性、串扰、信号损耗等问题直接影响电路板的性能稳定性。随着5G通信、服务器、高速计算、汽车电子等行业对高频、高速信号传输的需求增加,如何优化PCB布线以降低*

PCB设计距离一样时,你们知道电路板两对过孔怎么摆串扰最小吗?

的文章中,例如(链接《过孔的设计孔径是真的很重要,但高速先生也是真的不关心》)描述了单对过孔自身的设计对性能的影响。那我们这篇文章就来讲讲如何做好两个过孔之间的PCB串扰这个老大难的问题哈。

相比于

发表于 02-26 09:40

ADC电路的串扰怎么解决?

,ADC是SAR型 18位单通道全差分输入的ADC。ADC的后端是MCU,MCU将数字信号处理之后再画到显示屏上显示实时波形。

调试发现显示的信号有串扰,表现为某一路信号悬空之后,相邻的那一路信号上就会出现噪声。将采样的时间延长也无法消除

发表于 01-07 06:15

使用TMUX1109做ADC差分同步采样,出现了很严重的串扰怎么解决?

各位工程师好!我在使用TMUX1109做ADC差分同步采样,现在出现了很严重的串扰问题,我软件是在每次通道切换完成后100us才开始采样的,但是每个通道的波形始终有串扰,而且非常严重

发表于 11-29 11:09

DAC61416通道间出现串扰的原因?怎么解决?

在使用DAC61416输出方波电压时,先在Toggle引脚输入PWM信号,以便实现方波电压输出,但输出电压之前,每个通道先置零,且置零的时间不同,然后就出现通道间的串扰;图中是相邻4通道波形,奇怪的是串

发表于 11-25 08:35

博眼球还是真本事?参考平面不完整信号串扰反而好

,PCB走线的串扰也是除了我们关心的损耗之外信号质量重要的影响因素,串扰的原理在以往的文章中已经描述很多了,这里就不再again and a

发表于 11-11 17:27

高频电路设计中的串扰问题

在高频电路的精密布局中,信号线的近距离平行布线往往成为引发“串扰”现象的潜在因素。串扰,这一术语描述的是未直接相连的信号线间因电磁耦合而产生的不期望噪声信号,它如同电路中的隐形干扰源,

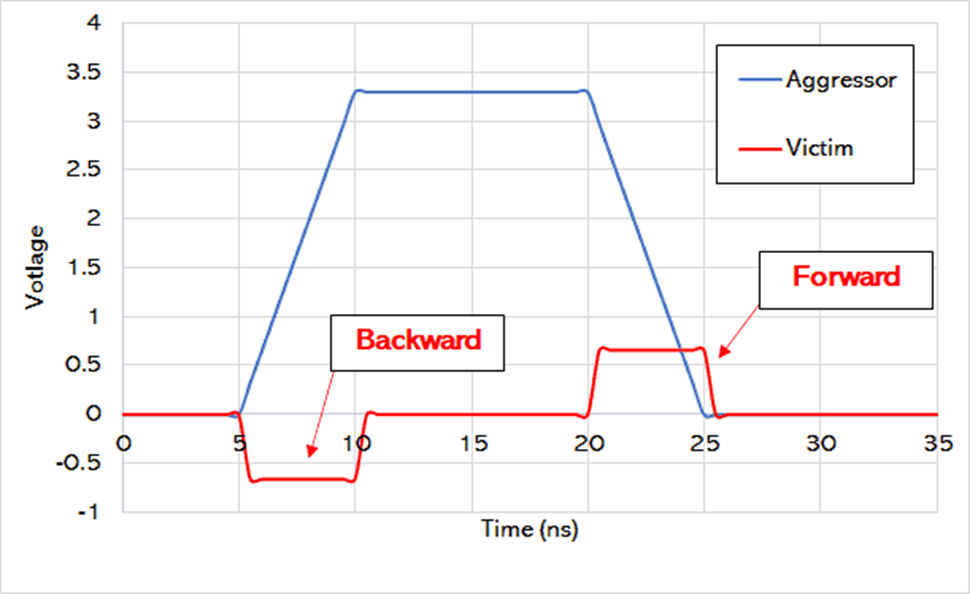

信号的串扰介绍

信号串扰(Crosstalk)是指在信号传输过程中,一条信号线上的信号对相邻信号线产生的干扰,这种干扰是由于电磁场耦合或直接电容、电感耦合引起的。根据耦合类型和位置的不同,信号串扰主要

轻松定位和修复pcb串扰问题

轻松定位和修复pcb串扰问题

评论