欢迎访问有关如何使用基本VHDL和Basys 3板构建秒表的说明。我们很高兴与您分享我们的项目!这是2016年秋季在SLO的Cal Poly开设的CPE 133课程(数字设计)的最终项目。我们构建的项目是一个简单的秒表,用于启动,重置和暂停时间。它以Basys3板上的三个按钮作为输入,并且时间显示在板的四位数七段显示器上。经过的时间以 seconds:厘秒格式显示。它使用开发板的系统时钟作为输入来跟踪经过的时间,并将时间输出到七段显示器的四位数。

步骤1:材料

该项目所需的材料:

从Xilinx安装了1台装有Vivado Design Suite WebPack的计算机(首选版本2016.2)

1 Digilent Basys3 Xilinx Artix-7 FPGA板

步骤2:设置输入和输出

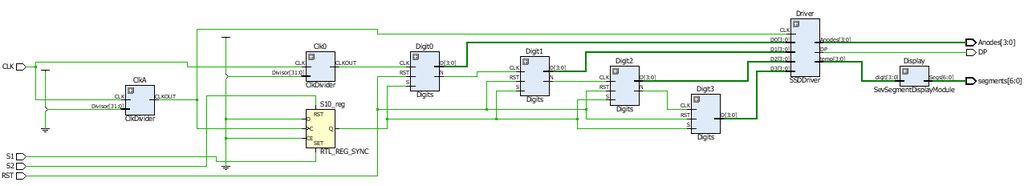

上图显示了秒表主模块的顶级框图。秒表接受输入“ CLK”(时钟),“ S1”(开始按钮),“ S2”(暂停按钮)和“ RST”(复位),并具有4位输出“阳极”,7位输出“段”和一位输出“ DP”(小数点)。当输入“ S1”为高时,秒表开始计时。当“ S2”为低时,秒表暂停时间。当“ RST”为高电平时,秒表将停止并重置时间。电路中有四个子模块:时钟分频器,数字计数器,七段显示驱动器和七段显示编码器。秒表主模块将所有子模块链接在一起,并链接到输入和输出。

步骤3:制作时钟

时钟分频器模块接收一个系统时钟,并使用一个除数输入来创建一个不大于系统时钟速度的时钟。秒表使用两个不同的时钟模块,一个创建一个500 Hz的时钟,另一个创建一个100 Hz的时钟。时钟分频器的原理图如上图所示。时钟分频器接收一个位输入“ CLK”,一个32位输入“除数”和一个位输出“ CLKOUT”。 “ CLK”是系统时钟,“ CLKOUT”是结果时钟。该模块还包括一个“非”门,当计数达到除数的值时,它将切换信号“ CLKTOG”。

步骤4:计数到十

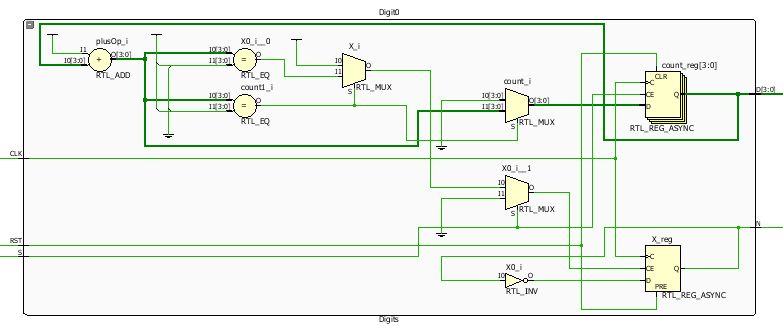

数字计数器对从0到10的每个数字进行计数,并为下一个数字创建另一个时钟,以使该数字在计数达到10时振荡。模块接收3个单位输入“ S”, “ RST”和“ CLK”并产生一个单位输出“ N”和一个4位输出“ D”。输入“ S”是输入中的启用。当“ S”为高电平时,时钟打开;当“ S”为低电平时,时钟关闭。 “ RST”是复位输入,因此当“ RST”为高电平时时钟将复位。 “ CLK”是数字计数器的时钟输入。 “ N”是时钟输出,成为下一位数字的输入时钟。输出“ D”表示计数器所在数字的二进制值。

步骤5:显示数字

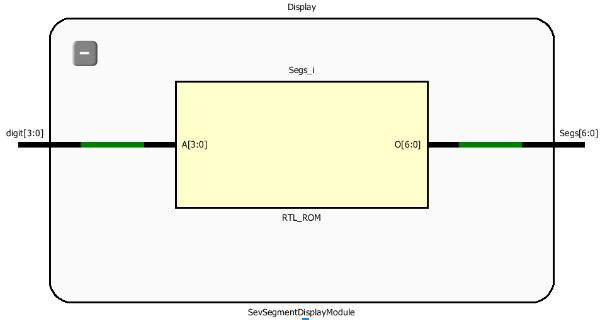

这七个-segment显示编码器将对从七段显示驱动器模块接收到的二进制数进行编码,并将其转换为比特流,对于每个显示段,该比特流将被解释为“ 1”或“ 0”值。二进制数由模块作为4位输入“数字”接收,并产生7位输出“段”。该模块由一个单例处理块组成,该块为从0到9的每个可能的输入值分配一个特定的7位流。七位流中的每个位代表显示器上数字的七个部分之一。流中各段的顺序为“ abcdefg”,其中“ 0”表示为给定数字点亮的段。

步骤6:如何显示秒表

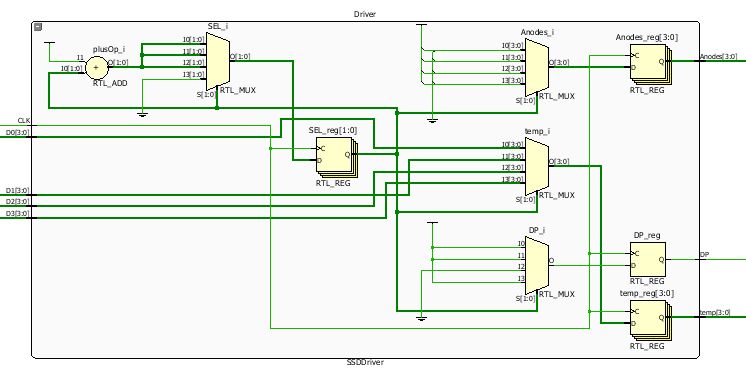

在七段显示驱动器模块中,有四个4位输入“ D0”,“ D1”,“ D2”和“ D3”,每个输入代表4位数字。被显示。输入“ CLK”是系统的时钟输入。一位输出“ DP”代表七段显示器上的小数点。 4位输出“ Anodes”确定显示七段显示器上的哪个数字,而4位输出“ temp”取决于2位控制输入“ SEL”的状态。该模块使用4个多路复用器作为控制输入“ SEL”和三个输出。 “阳极”,“温度”和“ DP”。

第7步:将它们整合在一起

一个从中运行的‘if’过程块500Hz时钟用于创建开始和暂停按钮。然后,通过声明每个单独的子模块的组件并使用各种信号,将秒表主模块中的所有子模块链接在一起。数字子模块采用前一个数字子模块的时钟输出,第一个采用100Hz时钟。然后,数字子模块的“ D”输出变为七段显示驱动器模块的“ D”输入。最后,七段显示驱动程序模块的“ temp”输出变为七段编码器模块的“ temp”输入。

步骤8:约束

使用3个按钮(W19,T17和U18)输入“ RST”,“ S1”和“ S2”。 W19是重置按钮,T17是开始按钮(S1),而U18是暂停按钮(S2)。还需要使用端口W5限制时钟输入的输入。另外,请记住将此行添加到时钟约束中:

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {CLK}]

也请链接阳极和电路板上的分段,因此秒表显示在约束文件中所示的七段显示器上。

步骤9:测试

通过按三个按钮来确保设备正常工作:以各种可能的方式推动并按住它们,以便发现代码中可能存在的问题。

责任编辑:wv

-

vhdl

+关注

关注

30文章

820浏览量

130077 -

秒表

+关注

关注

3文章

81浏览量

22374 -

basys3

+关注

关注

0文章

4浏览量

4596

发布评论请先 登录

为什么我选择VHDL入门

请问如何使用UUU进行独立内核构建?

为自定义板构建具有scarthgap 6.6.52支持的yocto映像时遇到报错如何解决?

浅谈Verilog和VHDL的区别

使用XC3S1500-4FGG456C控制ADS1248,读不到AD数据,为什么?

Verilog与VHDL的比较 Verilog HDL编程技巧

Verilog vhdl fpga

使用低成本MSP430 MCU简化7段LED秒表应用说明

如何使用基本VHDL和Basys3板构建秒表

如何使用基本VHDL和Basys3板构建秒表

评论