https://vhdlwhiz.com/should-i-learn-vhdl-if-verilog-is-becoming-more-popular/

https://www.sigasi.com/opinion/jan/verilogs-major-flaw/

https://digilent.com/blog/verilog-vs-vhdl/?srsltid=AfmBOopW22oVlEJQsfh9kTQePkD-7TUmSL58-S9MFdGj_i25Z1Kb20I3

https://www.fpga4student.com/2017/08/verilog-vs-vhdl-explain-by-example.html

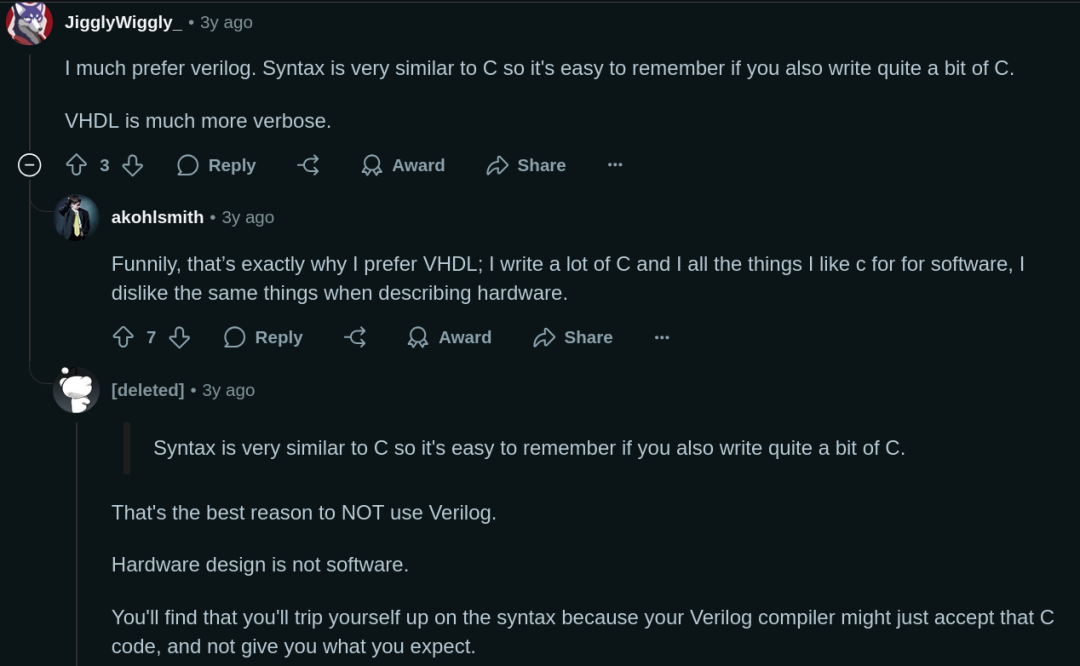

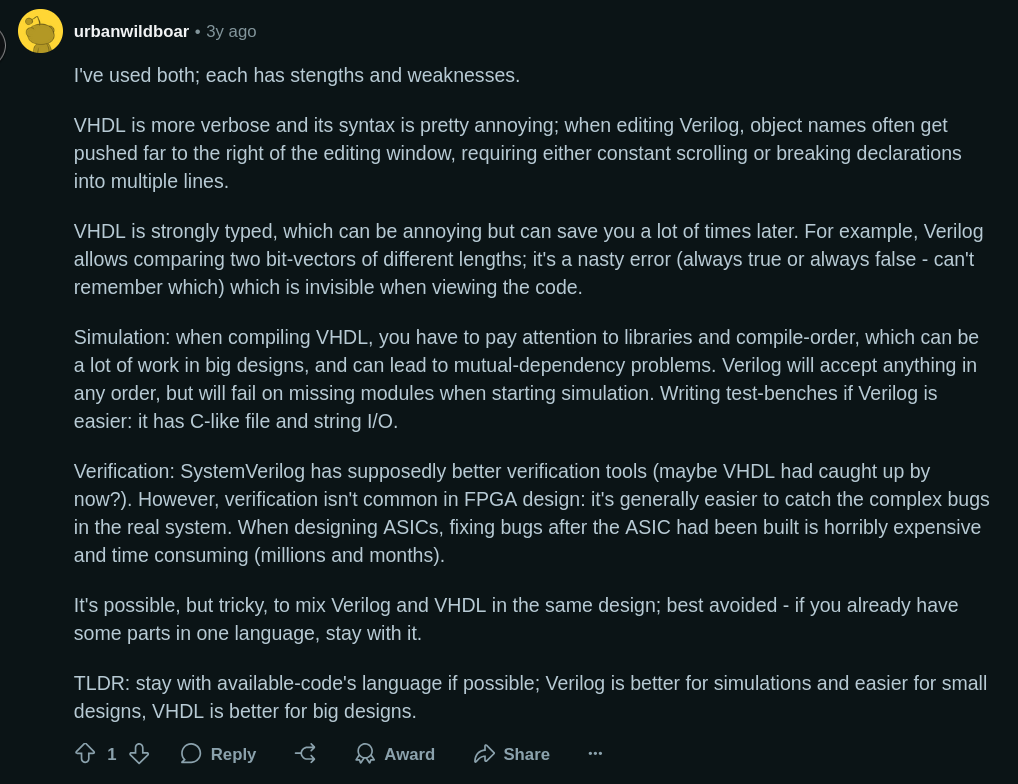

?支持 Verilog 的观点

?支持 Verilog 的观点

?支持 VHDL 的观点

?支持 VHDL 的观点

https://www.reddit.com/r/FPGA/comments/upcaj5/verilog_vs_vhdl/

?

?-

vhdl

+关注

关注

30文章

820浏览量

130084 -

KiCAD

+关注

关注

5文章

268浏览量

9610

发布评论请先 登录

做APPSFPGA的vhdl源码,fpga如何修改pgen送数据到数据总线然后复位?

AN90034用于功率MOSFETs的SPICE和VHDL-AMS中的Nexperia精密电热模型

浅谈Verilog和VHDL的区别

用于功率MOSFET的SPICE和VHDL-AMS精密电热模型

Verilog与VHDL的比较 Verilog HDL编程技巧

用“麦琳文学”打开人工智能,我配拥有一个好的AI学习方法吗?

Verilog vhdl fpga

FPGA编程语言的入门教程

明明我说的是25G信号,你却让我看12.5G的损耗?

为什么我选择VHDL入门

为什么我选择VHDL入门

评论