汽车音响导航系统中DDR高速信号的PCB设计(2)

2012年02月06日 10:51 来源:《科技创新导报》 作者:王文静 我要评论(0)

为控制传输线的阻抗及延时等的影响, 要先确定以下的布线设计标准:

*高速信号线条宽度,以保证传输线特性阻抗值:差分信号Zo 100Ω,其他信号Zo≒50Ω。

*为减少传输线间的串扰,确定最小间距值。实际布线时要尽可能加大间距。

*可用过孔的孔直径及过孔焊盘直径:

①Build-up积层激光冲压孔②内层盲埋孔(L2到L5使用)③通孔(L1到L6用)④各种过孔焊盘间最小间距。

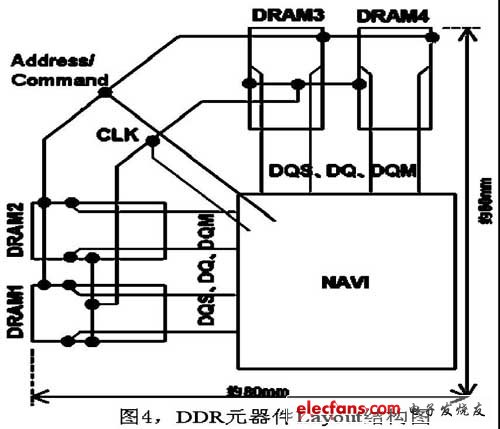

3.3 DDR SDRAM器件的布局结构图

DDR的数据传送通常是一个发射端对应多个接收端的结构, 为实现数据的同步传送,延迟时间的控制尤为重要。在构建器件Layout的时候重点考虑传输线分歧节点的选定,各段传输长度相等等要求。如图4,将DDR相关电路中的元器件都放在同一个面上, 并通过" 星型及Y 型拓扑结构"实现CLK、Data数据组,及Address/Command等各数据组之间的等长布线控制。

3.4 高频信号的布线优先顺序

依照设计要求的严格程度从最重要的信号线开始布起,顺序为:

CLK→Data→Address/Command

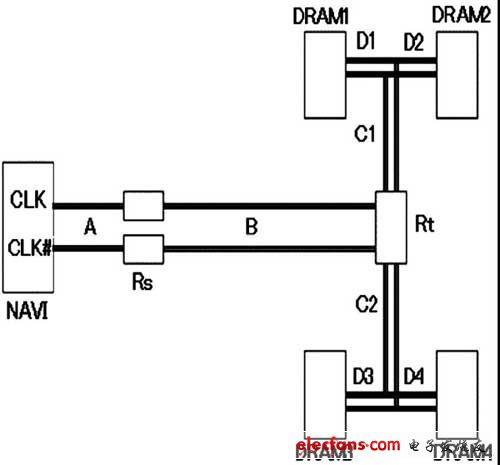

3.5 CLK差分信号的布线方法

针对DDR200中使用的CLK差分信号,布线拓扑图如图5 .布线注意点如下:

①差分阻抗要实现100Ω。

② 差分对CLK与CLK# 要等长布线,但总长度不要过长。

即CLK( A - B - C 1 - D 1 ) = CLK( A - B -C1-D2)= CLK( A - B - C 2 - D 3 ) = CLK( A - B -C2-D4)3.6 DATA组的布线方法。

图5 CLK布线拓扑图

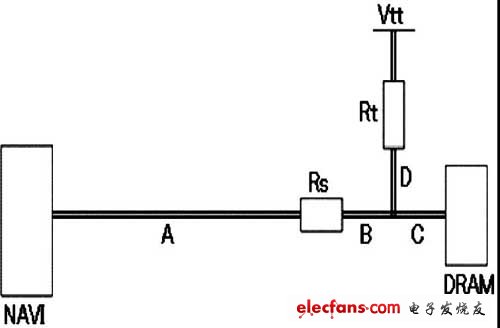

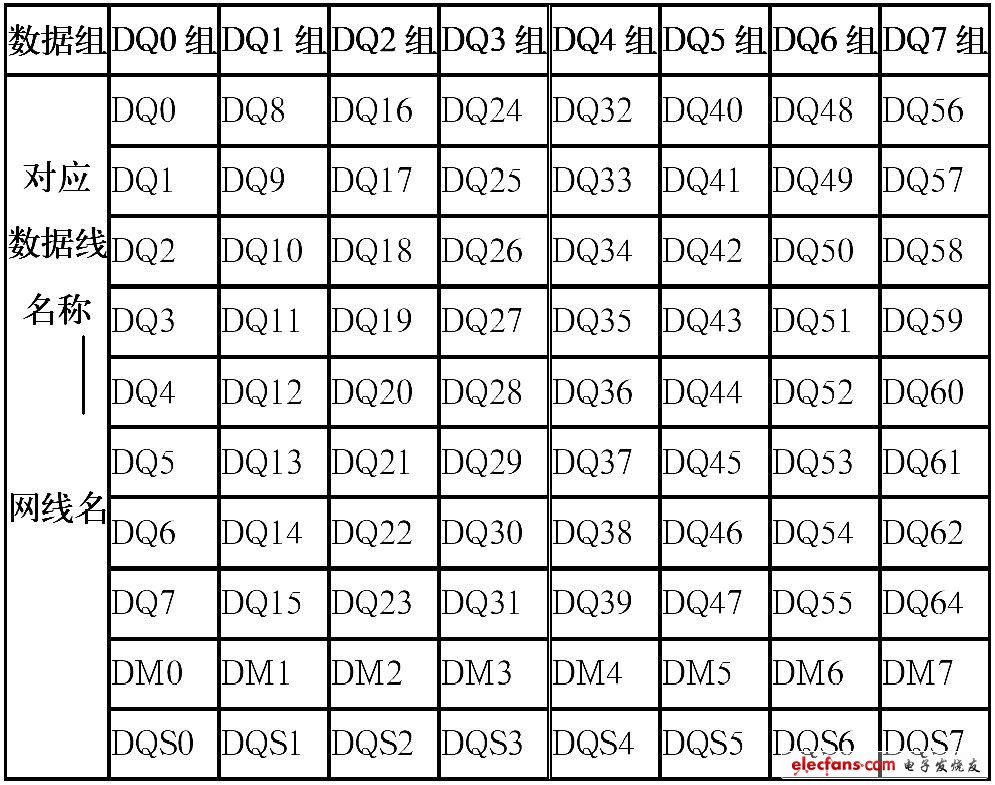

如图6, 标明了DATA组所选的布线拓扑图。布线注意点如下:

① 所有D A T A 信号从N A V I - C P U出发到每个D R A M 的长度都要相等( 即A - B - C段)。

②等长布线的误差可以按同一Bit列及各组Bit间的误差来控制,如表2。

图6 DATA数据组的布线拓扑图

表2

本文导航

- 第 1 页:汽车音响导航系统中DDR高速信号的PCB设计(1)

- 第 2 页:DDR SDRAM信号的布线标准

- 第 3 页:Address/Command的布线方法

标签: