在系统的设计中,光子计数IP核与Mieroblaze软核之间通过FSL总线进行通讯,并且对FSL总线上的FIFO缓冲进行了深度扩充,大大增强了光计数数据的传输可靠性。由于系统将门光子计数的三种模式,以IP核的方式实现,相对于市场上商用的计数器来说,实现方式灵活,易于配置和扩展,这种方式为门光子其他可能潜在的计数需求留下了扩展的基础,并具有较低的设计和生产成本。

相关推荐

74161设计12进制计数器

74161设计12进制计数器,1.74161为十六进制计数器,设计十二进制计数器时1片就可以满足要求。2.新建BDF文件及保存工程同前篇。3.将所需要的元器件和引脚拖入区域内并完成连接,如图1所示图1十二进制计数器连接图4.建立VWF文件,仿真后得到结果如图2

2021-07-22 06:33:31

Microblaze和FSL怎么连接?

你好我正在尝试将microblaze连接到一个新的custimized IP。我可以使用FSL总线吗?我可以使用vivado连接它们吗?我应该在IP HDL代码和微网格中做什么样的更改以及它们的接口?有什么文件可以帮助我?

2020-04-21 10:19:36

光子计数器

`光子计数探测器混合像素探测器,为您的实验室精心准备PILATUS混合像素探测器的设计是X射线探测领域的一次革命性成果,其能够实现最好的数据质量。该探测器将单光子计数和混合像素技术这两项关键技术

2014-03-03 19:21:07

计数器及时序电路原理及实验

计数器及时序电路原理及实验 一、实验目的1、了解时序电路的经典设计方法(D触发器、JK触发器和一般逻辑门组成的时序逻辑电路)。 &

2009-10-10 11:47:02

计数器显示的问题

刚开始接触Multisim,我用的是Multisim14,今天画了一个电路图 实现十进制计数器显示的功能,但仿真是报错 Transient time point calculation did not converge ,找不出原因,希望大家帮我找找错在哪里了哈

2016-08-14 20:18:15

计数器显示的问题

刚开始接触Multisim,我用的是Multisim14,今天画了一个电路图 实现十进制计数器显示的功能,但仿真是报错 Transient time point calculation did not converge ,找不出原因,希望大家帮我找找错在哪里了哈

2016-08-14 20:18:16

计数器极及其应用

; 2、掌握中规模集成计数器的使用及功能测试方法 3、运用集成计数计构成1/N分频器二、 实验原理计数器是一个用以实现计数

2009-10-11 10:00:11

计数器的结构和工作原理

目录C51定时器计数器电路图定时/计数器的结构和工作原理相关寄存器C51定时器计数器电路图定时/计数器的结构和工作原理定时/计数器的实质是加1计数器(16位),由高8位和低8位两个寄存器TH1

2022-01-24 07:04:15

计数器设计目的

实验目的1.1 计数器设计目的1) 每隔 1s,计数器增 1;能以数字形式显示时间。2) 熟练掌握计数器的各个部分的结构。3) 计数器间的级联。4) 不同芯片也可实现六十进制。1.2 计数器设计组成

2021-07-29 07:17:33

Labview自动门模拟

`自动门模拟(难度等级:★★)(1)设计任务采用计数器模块控制实现模拟自动门的运行。(2)基本要求采用事件结构完成相应功能。采用图片来模拟自动门的打开和关闭。指示灯显示开门或关门的状态。显示进入

2019-12-27 21:34:06

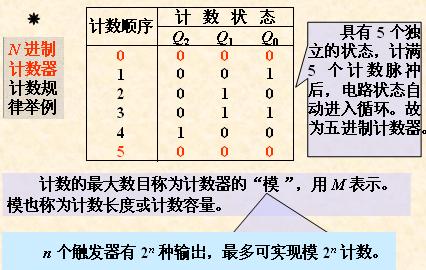

N进制计数器的实现

N进制计数器的实现 一、用集成计数器可以实现任意进制的计数器二、集成计数器控制功能的归类三、集成计数器的级联扩展四、复位法组成任意进制加法计数器五、置位法组成任意进制加法计数器六

2008-07-05 13:41:26

【FPGA开源教程连载】第四章 IP核应用之计数器

。这里实现了例化设计好的计数器IP核,且将其进行两级级联。分析综合无误后点击RTL viewer可以看如图5-15所示的原理图。图5-15 两级级联的计数器原理图为了测试仿真编写测试激励文件,新建

2016-12-22 23:37:00

【proteus练一练2.24】用计数器中断实现100以内的按键计数

/*名称:用计数器中断实现 100 以内的按键计数 说明:本例用 T0 计数器中断实现按键技术,由于计数寄存器初值为 1,因此 P3.4 引脚的每次负跳变都会触发 T0 中断,实现计数值累加

2012-02-24 09:36:02

【正点原子FPGA连载】第一章MicroBlaze简介--摘自【正点原子】达芬奇之Microblaze 开发指南

Insrtction System Computer)优化结构和Harvard总线结构,广泛适用于Spartan、Virtex和Artix等系列的FPGA。MicroBlaze软核嵌入式处理器是高度可定制的IP核

2020-10-16 16:28:50

以计数器IP核为例了解IP使用流程

。这里实现了例化设计好的计数器IP核,且将其进行两级级联。分析综合无误后点击RTL viewer可以看如图5-15所示的原理图。图5-15 两级级联的计数器原理图为了测试仿真编写测试激励文件,新建

2019-03-04 06:35:13

关于计数器的疑问

最近在看《现代操作系统》,他提到了时钟维持实际时间,在每个时钟滴答将计数器加1即可实现。但要注意位溢出(32位计数器),可以通过以下方法解决:使用64位计数器:缺点是这种方法使得计数器加一操作的代价很高,1s内维护很多次计数器。我不太懂红色字体的意思

2018-05-04 11:36:41

在FPGA中设计实现24进制加法计数器的设计

1、实现一个24进制加法计数器的设计本实验设计实现一个24进制的加法计数器,它由晶体振荡器、分频器、计数器和数码管显示器组成,图6.1是该加法计数器的示意图。晶体振荡器产生稳定的50MHz的脉冲信号

2022-07-05 15:14:27

在SoPC上实现的波形发生器

基于FPGA的嵌入式系统的开发工具包。本文介绍基于SoPC的波形发生器在EDK工具包下的设计与实现。本设计采用嵌入式软处理器核 MicroBlaze以及自主编写的包括实现DDS在内的多种IP Core

2009-06-25 08:12:37

基于IP核的PCI总线接口设计与实现

本文的应用背景为某一工业测控系统,该系统采用FPGA实现测量数据的采集和控制信号的输出,通过定制PCI接口IP实现一个32位目标设备的PCI总线接口转换。PCI核选用AlteraPCI编译器所包括

2018-12-04 10:35:21

如何在ARM核软件中实现硬件双输入计数器?

大家好!我目前正在研究的项目需要一个计数器,该计数器具有基于两个非周期时钟/计数方向信号的增量或递减其值的能力(与只需要与一个时钟/计数方向对一起工作的通用计数器形成对比)。我可以想到几种在ARM核

2019-10-25 12:47:24

定时/计数器实现功能

定时/计数器实现功能:(1)定时功能:定时/计数器说明(最高单次计时时间是71毫秒=65535*1.085us,1.085us是机器周期):使用51定时/计数器步骤:定时/计算器控制寄存器:设置定时

2021-12-01 07:17:27

数据采集卡的trigger端口输入脉冲信号,使其触发计数器计数?

目标:获取一段时间内的单光子计数器的计数值。当前思路是:使用延迟脉冲信号发生器发送脉冲信号给数据采集卡PCIE-6374的Trigger端,使其触发计数器进行计数。问题:怎样设置DAQ助手?或者怎样去学习设置?没有百度到相关的方法,恳请大家帮助。

2020-12-25 20:02:01

有办法使用Vivado本身为Microblaze创建FSL接口吗?

嗨,大家好,我正在使用Vivado 2014.4有没有办法使用Vivado本身为Microblaze创建FSL接口?如果是,我可以使用此FSL将FIFO连接到MB吗?请建议。谢谢你们,提前。谢谢&问候,专一

2020-04-06 17:25:00

求一款双MicroBlaze软核处理器的SOPC系统设计

处理器间通信和中断方面仍需进一步的研究。本文在处理器间通信和中断控制方面进行了深入的研究。MicroBlaze是一个被优化过的可以在Xilinx公司FPGA中运行的软核处理器,可以和其他外设IP核一起完成

2021-03-16 07:44:35

浅析计数器的组成部分及其功能

计数器(Counter)由基本的计数单元和控制门所组成,是在数字系统中对脉冲的个数进行计数,以实现测量、计数和控制功能,且兼有分频功能的仪器。计数器按进位制不同,分为二进制计数器和十进制计数器;按

2021-12-08 08:32:28

调用ip核生成一个4位计数器

我们调用ip核生成一个4位计数器后想用该计数器模块生成一个8位的计数器,这里就需要级联两个计数器这个是counter模块:module counter ( cin, clock, cout, q

2021-11-11 07:41:25

顶层为原理图的能显示16进制减法计数器设计

顶层为原理图的能显示16进制减法计数器设计1.用VHDL设计一个二选一电路,并用ModelSim Simulator 仿真验证。 要求该二选一电路能实现16进制数的两位数据串行输出(或称动态输出

2009-10-11 08:51:38

频率计数器的实现原理是什么

这里我们所讲的开发板是CT107D,频率计数器这一部分,比较容易。物理连接上,只需要把单片机开发版上的P34管脚和SIGNAL用跳线连接即可。下面,我们将直接进入代码分析和频率计数器的实现原理分析

2022-02-23 07:36:22

定时器/计数器基础

15-1.实现定时的方法15-2.定时器/计数器的结构和工作原理 15-3.定时器/计数器的控制15-4.定时器/计数器的工作方式 15-5.定时器/计数器应用 软件定时软件延时不占用硬

2009-03-23 12:17:51 48

48

48

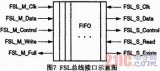

48FSL总线IP核及其在MicoBlaze系统中的应用

本文对 MicroBlaze 的几种主要总线接口摘要进行比较,详细分析、介绍FSL 总线的结构、特点、工作原理和配置方法。通过一个矢量汉字还原的应用实例,具体描述在FPGA片上系统设

2009-11-30 15:08:04 11

11

11

11近红外单光子计数器

近红外单光子探测器 SPD4近红外单光子探测器SPD4是基于InGaAs雪崩光电二极管的超灵敏探测仪器。可以探测范围覆盖900 nm~1700 nm波段的光子,最高可达30%的量子效率,最低至1.0

2023-03-16 13:48:40

什么是二进制计数器,二进制计数器原理是什么?

什么是二进制计数器,二进制计数器原理是什么?

计数器是数字系统中用得较多的基本逻辑器件。它不仅能记录输入时钟脉冲的个数,还可以实现

2010-03-08 13:16:34 30351

30351

30351

30351计数器,计数器的工作原理是什么?

计数器,计数器的工作原理是什么?

在数字系统中使用最多的时序电路是计数器。计数器不仅能用于对时钟脉冲进行计数还可以用于分频、定时,产生

2010-03-08 13:50:14 59934

59934

59934

59934基于Xilinx MicroBlaze多核嵌入式系统的设计

MicroBlaze 核是嵌入在Xilinx FPGA之中的属于32位RISC Harvard架构软处理器核。针对Xilinx MicroBlaze软处理器的核间互连,实现多处理器核之间的快速通信的目的,采用了PLB和FSL总线混连的方法,

2011-07-20 17:22:21 68

68

68

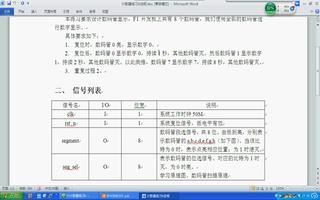

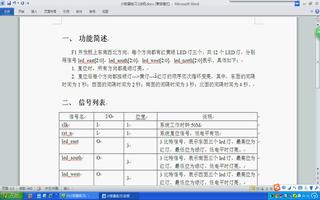

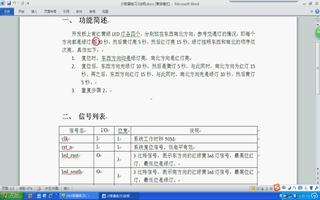

68基于FSL总线的门光子计数器设计

所谓门光子计数器就是针对单自旋量子调控实验研究中对单个光子探测的需求所研制的。光子计数IP核与Mieroblaze软核之间通过FSL总线进行通讯,并且对FSL总线上的FIFO缓冲进行了深度扩充

2011-08-13 15:11:29 1411

1411

1411

1411

基于AXI总线的MicroBlaze双核SoPC系统设计

目的是利用嵌入在Xilinx FPGA中的MicroBlaze核实现基于AXI总线的双核嵌入式系统设计以及共享实现LED灯的时控.

2012-03-09 14:17:01 91

91

91

91基于Multisim的计数器设计仿真

计数器是常用的时序逻辑电路器件,文中介绍了以四位同步二进制集成计数器74LS161和异步二-五-十模值计数器74LS290为主要芯片,设计实现了任意模值计数器电路,并用Multisim软件进行了

2013-07-26 11:38:41 134

134

134

134计数器的控制及应用

计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成

2017-09-25 10:13:37 8

8

8

824进制计数器的设计

集成计数器常见的是多位二进制计数器及十进制计数器,当需要实现其它进制计数器时,通常利用现有的集成计数器进行适当的连接而构成。对于当设计要求没有限定计数器的状态编码时电路设计的灵活性问题已有文献进行

2017-11-09 16:36:16 81

81

81

81以较低的设计和生产成本推广到其他光子计数器的设计和实现

。系统采用的是一种基于MicroBlaze系统FSL总线的可扩展计数器设计架构,该架构能够灵活的添加不同的计数功能,并通过统一的FSL总线和Microblaze CPU与PC通信。在该架构的基础上实现了针对量子单自旋调控实验中常用的计数模式。

2017-11-24 16:56:39 548

548

548

548

74LS161集成计数器电路(2、3、4、6、8、10、60进制计数器)

端,可以串接计数器使用。单片161可以实现16以内任意进制的加法计数功能。实现60进制加法计数器需要2片161,它们之间的连接方式又分同步和异步两种。下面一起来看看怎么实现的。

2018-01-18 10:56:39 353099

353099

353099

353099

机械计数器结构及原理图

计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成

2018-02-24 15:31:08 45454

45454

45454

45454计数器原理

计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成

2019-01-24 14:35:40 63341

63341

63341

63341MOD计数器和时序图

计数器的工作是通过每个时钟脉冲将计数器的内容提前一个计数来计数。当被时钟输入激活时推进其数字或状态序列的计数器被称为以“递增计数”模式操作。同样,当被时钟输入激活时减少其数字或状态序列的计数器被称为以“倒计数”模式操作。在UP和DOWN模式下工作的计数器称为双向计数器。

2019-06-23 07:47:00 12721

12721

12721

12721

什么是计数器芯片?

什么是计数器芯片? 一般来说,计数器芯片就是用来实现计数这种最基础运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数

2021-07-13 14:09:37 12366

12366

12366

12366"stm32f0按键计数器程序_数字系统设计, 8个经典计数器电路方案合辑"

计数器(Counter)由基本的计数单元和控制门所组成,是在数字系统中对脉冲的个数进行计数,以实现测量、计数和控制功能,且兼有分频功能的仪器。计数器按进位制不同,分为二进制计数器和十进制计数器

2021-11-25 18:06:07 32

32

32

32Johnson约翰逊计数器Verilog实现

扭环形计数器,约翰逊计数器,每次状态变化时仅有一个触发器发生翻转,译码不存在竞争冒险,在n(n≥3)位计数器中,使用2n个状态,有2^n-2n个状态未使用;

2022-06-15 09:27:57 1971

1971

1971

1971基于FPGA的十进制计数器

本方案是一个基于 FPGA ?的十进制计数器。共阳极 7 段显示器上的 0 到 9 十进制计数器,硬件在 Xilinx Spartan 6 FPGA 板上实现。

2022-12-20 14:52:25 2

2

2

2同步计数器和异步计数器是什么 同步计数器和异步计数器的主要区别?

在数字电子产品中,计数器是由一系列触发器组成的时序逻辑电路。顾名思义,计数器用于计算输入在负或正边沿转换中出现的次数。根据触发触发器的方式,计数器可以分为两类:同步计数器和异步计数器。了解这两种计数器的工作原理以及它们之间的区别。

2023-03-25 17:31:07 18646

18646

18646

18646

同步计数器和异步计数器各有什么特点

同步计数器和异步计数器是两种常见的数据结构,它们都用于控制对共享资源的访问。它们的主要作用是实现多个线程之间的同步和并发控制。尽管它们都被用于同步的目的,但它们有很多不同的特点和用例。 同步计数器

2023-12-15 10:49:43 512

512

512

512计数器怎么用 计数器的作用有哪些

计数器是一种被广泛应用于各个领域的实用工具,在我们的日常生活中随处可见。无论是进行时间统计,协助工作任务的完成,还是用于科学研究和编程技术,在各个领域都起到了重要的作用。本文将详细介绍计数器

2024-02-03 10:04:14 588

588

588

588 电子发烧友App

电子发烧友App

评论