声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电源

+关注

关注

185文章

18396浏览量

256873 -

稳压器

+关注

关注

24文章

4732浏览量

96450 -

图像传感器

+关注

关注

68文章

1984浏览量

130847

发布评论请先 登录

相关推荐

热点推荐

什么是共模抑制比?

共模抑制比详解在探头的数据手册上,共模抑制比性能参数是核心指标之一。共模抑制比又名CMRR,通常用分贝(dB)来表示,其计算公式为:其中其中本司光隔离产品CMRR在直流或低频下能达到120dB以上

海洋仪器电源抑制比测试方案26800元起

在电子技术日新月异的今天,电源抑制比(PowerSupplyRejectionRatio,简称PSRR)宛如一把精准的标尺,衡量着电子电路对电源噪声和电压波动的

ups不间断电源—轻松搞定UPS(不间断电源)噪音大难题

一、检查负载情况

1. 降低负载:检查UPS(不间断电源)所承载的负载是否超过其设计的额定容量。如果负载过大,建议降低负载以减轻(不间断电源)的工作压力,从而

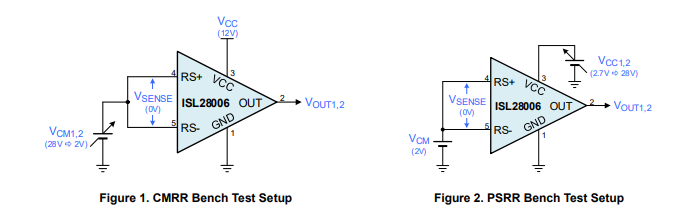

ISL28006:测量共模和电源抑制比

虽然电流检测放大器(如ISL28006)的数据手册以电气规格的形式展示了器件性能,但有时客户需要通过基准测试来确认电气参数。尤其重要的是共模抑制比(CMRR)和电源抑制比(PSRR),

耦合器的噪音控制技术 耦合器性能测试标准与方法

率的材料可以减少信号传输过程中的噪音。 设计优化 :通过优化耦合器的结构设计,如调整耦合器的尺寸和形状,可以减少寄生电容和电感,从而降低噪音。 屏蔽技术 :使用屏蔽材料可以减少外部电磁干扰对耦合器的影响,降低噪音。

详解LDO电路的电源抑制比

电源抑制(Power Supply Rejection)能力是SoC系统中电源模块很重要的指标,在当今数字和模拟电路高度集成的趋势下,一个能提供稳定输出电压的系统模块显得尤为重要,而这个模块又很容易受到供电

使用PCM5242,当喇叭输出最大音量时伴有“沙,沙”低噪音,爆破音很大怎么解决?

使用PCM5242,当喇叭输出最大音量时伴有“沙,沙”低噪音,爆破音很大

功放前端4通道波形信号1khz时很完美,功放后端失真披锋较多,看情况应该是后端问题,请问有没有什么建议?

发表于 10-10 08:23

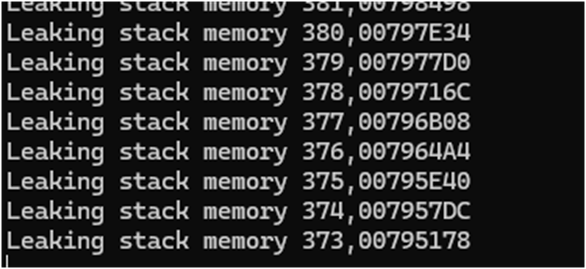

堆栈和内存的基本知识

本文主要聊聊关于堆栈的内容。包括堆栈和内存的基本知识。常见和堆栈相关的 bug,如栈溢出,内存泄漏,堆内存分配失败等。后面介绍软件中堆栈统计的重要性,以及如何使用工具工具软件中堆栈使用的范围,并给出在软件开发中,如何降低堆栈问题,优化堆栈的一些实践。

影响电路共模抑制比的因素有哪些?如何去提高电路的共模抑制比?

此电路用来检测脑电波的信号,性能要求此电路的共模抑制比要达到不低于80dB,而现在实测只能达到67dB,想知道,影响电路共模抑制比的因素有哪些?如何去提高电路的共模抑制比?

发表于 08-20 07:21

运放的共模抑制比和电源抑制比对输出精度的影响是什么?

的共模抑制比为120dB,单纯考虑共模抑制比的影响电流60A,运放输出值理论为Vo=0.0335*60,该怎么计算输出的误差呢?Gain取大于1和小于1影响是怎么样的?

2、电源抑制比

发表于 08-15 07:43

如何理解运放的电源抑制比参数?

电源抑制比PSRR有三个参数,如OPA333

1、电源抑制比为1uV/V

2、长期稳定性为1uV

3、通道分离,直流为0.1uV/V

特

发表于 08-12 06:37

电源抑制比的基本知识及如何降低噪音

电源抑制比的基本知识及如何降低噪音

评论