Vivado HLS有助于降低整体系统功耗,降低材料成本,提高系统性能并加快设计生产率。 我们将向您展示如何使用C,C ++或SystemC创建更高效的规范。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

33文章

1797浏览量

132486 -

C++

+关注

关注

22文章

2119浏览量

75519 -

Vivado

+关注

关注

19文章

835浏览量

69003

发布评论请先 登录

相关推荐

热点推荐

如何在Unified IDE中创建视觉库HLS组件

最近我们分享了开发者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 传统 IDE)和开发者分享|AMD Vitis HLS 系列 2:AMD

Linux系统性能指南

Linux服务器运行了很多应用,在高负载下,服务器可能会出现性能瓶颈,例如CPU利用率过高、内存不足、磁盘I/O瓶颈等,从而导致系统卡顿,服务无法正常运行等问题。所以针对以上问题,可以通过调整内核参数和系统的相关组件,优化应用程

使用AMD Vitis Unified IDE创建HLS组件

这篇文章在开发者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 传统 IDE) 的基础上撰写,但使用的是 AMD Vitis Unified IDE,而不是之前传统版本的 Vitis HLS

升降速曲线对直线电机系统性能影响的研究

速曲线对直线电机系统性能影响的研究.pdf【免责声明】本文系网络转载,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请第一时间告知,删除内容!

发表于 06-17 08:48

如何使用AMD Vitis HLS创建HLS IP

本文逐步演示了如何使用 AMD Vitis HLS 来创建一个 HLS IP,通过 AXI4 接口从存储器读取数据、执行简单的数学运算,然后将数据写回存储器。接着会在 AMD Vivado Design Suite 设计中使用此

Vivado HLS设计流程

为了尽快把新产品推向市场,数字系统的设计者需要考虑如何加速设计开发的周期。设计加速主要可以从“设计的重用”和“抽象层级的提升”这两个方面来考虑。Xilinx 推出的 Vivado HLS 工具可以

功耗对IGBT性能的影响,如何降低IGBT功耗

在电力电子的广阔领域中,绝缘栅双极型晶体管(IGBT)作为核心器件,其性能优劣直接关乎整个系统的运行效率与稳定性。而功耗问题,始终是IGBT应用中不可忽视的关键环节。今天,就让我们一同深入

频域示波器的技术原理和应用场景

的传输质量和特性,为进一步的优化和改进提供依据。

综上所述,频域示波器作为一种功能强大的电子测量仪器,在电子工程、通信、科研等领域具有广泛的应用前景和重要的实用价值。通过利用其频谱测量和分析功能,工程师可以深入了解信号的频率特性,优化电子系统性能,

发表于 03-11 14:37

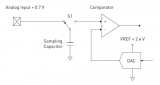

如何降低电子开关的功耗

电子开关是现代电子系统中不可或缺的组成部分,它们控制电流的流动,实现设备的开启和关闭。然而,随着电子设备功能的增强和集成度的提高,功耗问题也日益突出。降低电子开关的

电力驱动测试系统的技术原理和应用

广泛的应用领域和重要的技术价值。通过不断优化和完善测试系统的技术原理和应用方法,可以进一步提高电力驱动设备的性能和质量水平,推动新能源汽车产

发表于 12-19 14:54

PCIe延迟对系统性能的影响

随着技术的发展,计算机系统对性能的要求越来越高。PCIe作为连接处理器、内存、存储和其他外围设备的关键接口,其性能直接影响到整个系统的表现。

栅极驱动芯片选型低功耗原因

,减少能源浪费,并降低设备的运行成本。 2. 提升能效 栅极驱动芯片作为功率转换和驱动控制的关键元件,其功耗直接影响整个系统的能效。选择低功耗的栅极驱动芯片,可以在保证

优化 FPGA HLS 设计

优化 FPGA HLS 设计

用工具用 C 生成 RTL 的代码基本不可读。以下是如何在不更改任何 RTL 的情况下提高设计性能。

介绍

高级设计能够以简洁的方式捕获设计,从而

发表于 08-16 19:56

AH7691D低功耗、高效率、低纹波52V转12V 1.5A安防POE电源芯片

原因导致的设备损坏风险,进一步提高了系统的整体可靠性。

综上所述,这款低功耗、高效率、低纹波52V转12V 1.5A的安防POE电源转换器以其卓越的

发表于 08-16 17:49

Vivado HLS深入技术助于降低整体系统功耗,提高系统性能

Vivado HLS深入技术助于降低整体系统功耗,提高系统性能

评论