声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1646文章

22069浏览量

619708 -

赛灵思

+关注

关注

33文章

1797浏览量

132457 -

PCIe

+关注

关注

16文章

1350浏览量

85542

发布评论请先 登录

相关推荐

热点推荐

火爆开发中 | 开源FPGA硬件板卡,硬件第一期发布

接口形态邀您投票啦!

在开源FPGA开发板的设计中,PCIe 接口形态的选择至关重要,直接影响着开发板的性能、适用场景和使用体验。目前,常见的 PC

发表于 07-09 13:54

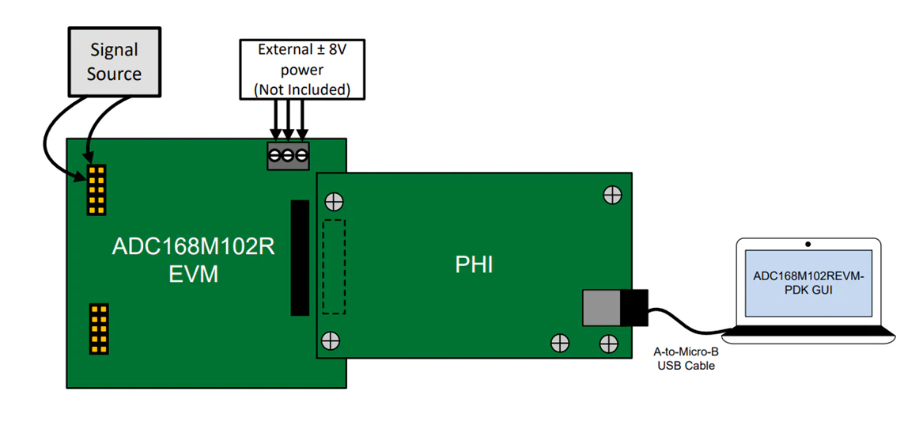

Texas Instruments ADC168M102REVM-PDK性能演示套件数据手册

Texas Instruments ADC168M102REVM-PDK性能演示套件 (PDK) 用于评估16位、8通道1MSPS同步采样模数转换器 (ADC) ADC168M102R-SEP

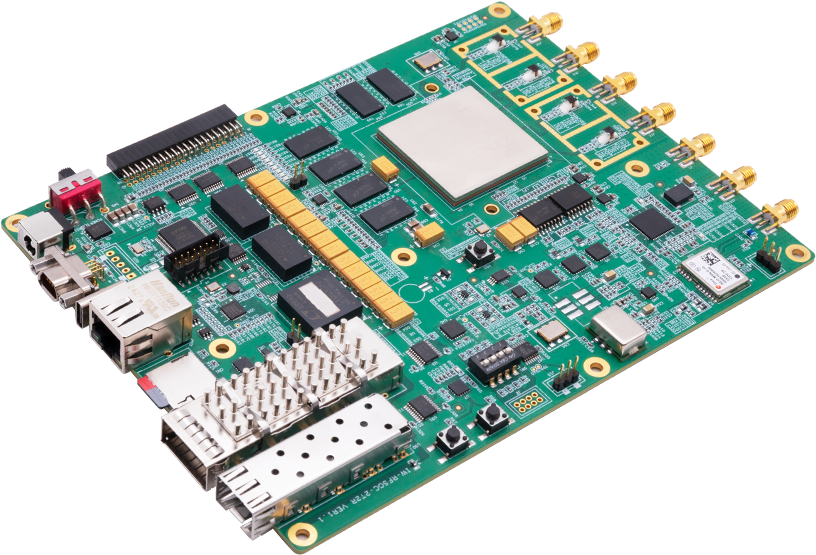

高性能紧凑型 RFSoC FPGA 开发平台 AXW22,重塑射频开发体验

UltraScale+ RFSoC?Gen3 系列 ZU47DR 芯片 ,将射频直采转换器、高性能 FPGA 逻辑与多核 ARM 处理器融合,简化了系统架构、降低了功耗和延迟,减少了

正点原子AU15开发板资料发布!板载40G QSFP、PCIe3.0x8和FMC LPC等接口,性能强悍!

正点原子AU15开发板资料发布!板载40G QSFP、PCIe3.0x8和FMC LPC等接口,性能强悍!

正点原子AU15开发板搭载Xilinx Artix UltraScale+ 系列FP

发表于 05-30 17:04

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

Ultrascale是赛灵思开发的支持包含步进功能的增强型FPGA架构,相比7系列的28nm工艺,Ultrascale采用20nm的工艺,主要有2个系列:Kintex和Virtex

RZ T2H PCIe裸机程序开发和Linux下的配置介绍

,还提供2个PCIe Gen3通道等高速外设。本文主要介绍PCIe外设的功能、裸机下EP模式的程序开发、以及在Linux下,如何编译网卡的流程。

如何用MCU MSP430F5342链接控制ADS1298ECG模拟前端性能演示套件?

RESP circuitry)

我希望用MCU MSP430F5342 链接控制“ADS1298ECG 模拟前端性能演示套件”,

请问1).两边(MSP430F5342端, 和ADS1298ECG 端)如何相连?

2). 必须使用两个电源吗?(因为两个开发板)

可以使用一个吗?

发表于 12-18 07:26

AMD推出了Versal Premium Series Gen 2,这是业界第一个支持CXL 3.1和PCIe Gen6的FPGA平台。

AMD推出了Versal Premium Series Gen 2,这是业界第一个支持CXL 3.1和PCIe Gen6的FPGA平台。 ? AMD为数据中心、航空航天、通信和T M市

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性

Xilinx7系列FPGA集成了新一代PCI Express集成块,支持8.0Gb/s数据速率的PCI Express 3.0。本文介绍了7系列FPGA PCIe Gen3的应用接口及

美光研发出世界首款PCIe Gen6 SSD

美光公司近期宣布,已成功研发出世界首款PCIe Gen6 SSD,这款设备可实现超26GB/s的顺序读取速度,以此满足未来数据中心需求,再度彰显其在存储技术方面的卓越竞争力。就在最近,他们刚刚推出

UltraScale FPGA器件中PCIe Gen3模块的性能演示

UltraScale FPGA器件中PCIe Gen3模块的性能演示

评论