声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1646文章

22101浏览量

620859 -

连接器

+关注

关注

99文章

15525浏览量

141567 -

赛灵思

+关注

关注

33文章

1797浏览量

132593

发布评论请先 登录

相关推荐

热点推荐

高速总线接口的类型介绍

串行RapidIO,高速串行通信协议,旨在链接DSP、FPGA、网络处理器等芯片,具有低延迟、高带宽(支持25Gbps、2.5Gbps、3.125Gbps的

高速数据采集卡设计:887-基于 RFSoC 47DR的8T8R 100Gbps 软件无线电光纤前端卡

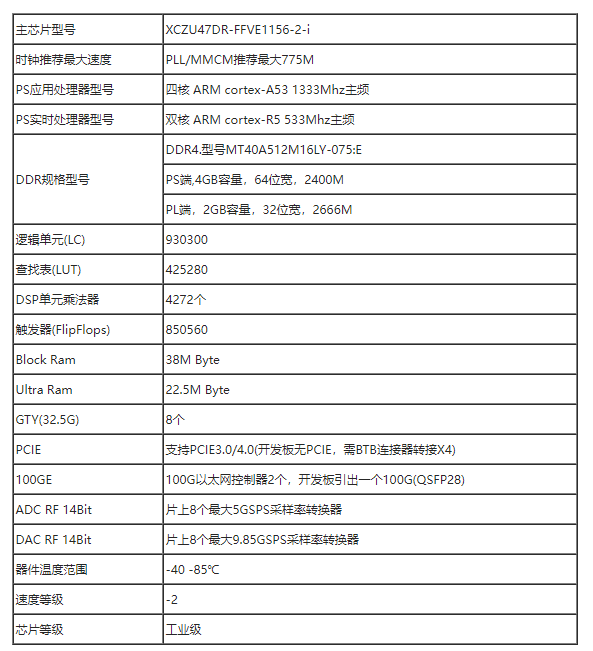

一、 板卡概述 ? ? ?板卡使用Xilinx最新的第三代RFSOC系列,单颗芯片包含8路ADC和DAC,64-bit Cortex A53系列4核CPU,Cortex-R5F实时处理核,以及大容量FPGA。对主机接口采用100Gbps

聊聊高速PCB设计100Gbps信号的仿真

这些影响因素会变得更加敏感,所以我们需要花更多的时间来调整这些参数,在25Gbps速率下,长孔和短孔用同样的尺寸参数影响不大,但到了100Gbps以上,不同层需要不同的过孔参数,这样就会多出更多的建模

发表于 03-17 14:03

ST25DV64与HR11 NFC模块之间如何实现数据传输?

主要目的:实现在两个NFC模块之间进行数据传输

在网络上搜索了一下,大概有以下方式:

1、使用FTM模式;

2、使用NDFF协议,比较复杂,目前只是想实现简单的两个模块之间读写

发表于 03-10 08:00

SFP模块在网络拓扑中的作用

,以实现高速数据传输。 2. SFP模块的类型 SFP模块有多种类型,包括: SFP+ :支持10Gbps传输速率,常用于10G以太网。 SFP28 :支持25Gbps

xilinx FPGA IOB约束使用以及注意事项

采用了IOB约束,那么就可以保证从IO到达寄存器或者从寄存器到达IO之间的走线延迟最短,同时由于IO的位置是固定的,即存在于IO附近,所以每一次编译都不会造成输入或者输出的时序发生改变。 二、为什么要使用IOB约束 考虑一个场景,当你用FPGA写了一个spi模块,将时钟、

ADS6149采样率250Mhz,后级接Xilinx FPGA,输入1Mhz正弦波,在FPGA接口采样得到异常采样点,为什么?

将ADS6149配置为测试模式,配置输出ramp波形,在FPGA内部做ramp数据检测,测试半小时,无错误数据。

将ADS6149配置为测试模式

发表于 12-25 07:57

【米尔-Xilinx XC7A100T FPGA开发板试用】+04.SFP之Aurora测试(zmj)

于芯片(FPGA)与芯片(FPGA)之间通信,它用于使用一个或多个收发器在设备之间传输数据,其连

发表于 11-14 21:29

25G SFP28 BIDI光模块介绍

,CPRI/eCPRI,IEEE802.3CC 25GBASE-LR以太网等标准,广泛应用于数据中心、城域网、无线网络、传输网络等。

产品特征

最大速率高达25.78Gbps,采用

发表于 11-11 10:23

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性

Xilinx7系列FPGA集成了新一代PCI Express集成块,支持8.0Gb/s数据速率的PCI Express 3.0。本文介绍了7系列FP

明明我说的是25G信号,你却让我看12.5G的损耗?

子的:

在截取的这一串数据信号中,时钟信号通过上升和下降沿对数据信号进行采样。对于高速信号来说,每一位的“1”或者“0”的位宽的倒数就是我们的速率25Gbps。那问题来了,时钟信号的上升和下降沿都对

发表于 10-23 09:11

以太网的传输介质和工作模式

以太网是一种广泛应用的局域网(LAN)技术,它通过特定的传输介质和工作模式,在多个设备之间高效地传输数据。本文将从以太网的

Xilinx FPGA之间的25Gbps传输数据模式介绍

Xilinx FPGA之间的25Gbps传输数据模式介绍

评论