XDC 是 Xilinx Design Constraints 的简写,但其基础语法来源于业界统一的约束规范SDC(最早由 Synopsys 公司提出,故名 Synopsys Design Constraints)。XDC 在本质上就是 Tcl 语言,但其仅支持基本的 Tcl 语法如变量、列表和运算符等等,对其它复杂的循环以及文件 I/O 等语法可以通过在 Vivado 中 source 一个 Tcl 文件的方式来补充。观看视频,了解和学习有关XDC约束,包括时序,以及物理约束相关知识。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

33文章

1797浏览量

132479 -

语言

+关注

关注

1文章

97浏览量

24530 -

时序

+关注

关注

5文章

399浏览量

38154

发布评论请先 登录

相关推荐

热点推荐

再创新高,“中国环流三号”实现百万安培亿度高约束模

近日,由核工业西南物理研究院(简称“西物院”)研制的新一代人造太阳“中国环流三号”再次创下我国聚变装置运行新纪录——实现百万安培亿度高约束模(H模),即装置同时实现等离子体电流100万安培、离子温度

西门子再收购EDA公司 西门子宣布收购Excellicon公司 时序约束工具开发商

精彩看点 此次收购将帮助系统级芯片 (SoC) 设计人员通过经市场检验的时序约束管理能力来加速设计,并提高功能约束和结构约束的正确性 ? 西门子宣布 收购 Excellicon 公司 ,将该公司用于

PCB Layout 约束管理,助力优化设计

本文重点PCBlayout约束管理在设计中的重要性Layout约束有助避免一些设计问题设计中可以使用的不同约束在PCB设计规则和约束管理方面,许多设计师试图采用“一刀切”的方法,认为同

PanDao:实际约束条件下成像系统的初始结构的生成

摘要 :初始点的选择对后续设计过程具有重大影响。除透镜规格外,其它必要的实际约束条件也可能起到非常关键的作用。本研究采用“First Time Right”方法生成受约束的初始系统,并运用

发表于 05-07 08:57

FPGA时序约束之设置时钟组

Vivado中时序分析工具默认会分析设计中所有时钟相关的时序路径,除非时序约束中设置了时钟组或false路径。使用set_clock_groups命令可以使时序分析工具不分析时钟组中时钟的时序路径,使用set_false_path约束则会双向忽略时钟间的时序路径

xilinx FPGA IOB约束使用以及注意事项

xilinx FPGA IOB约束使用以及注意事项 一、什么是IOB约束 在xilinx FPGA中,IOB是位于IO附近的寄存器,是FPGA上距离IO最近的寄存器,同时位置固定。当你输入或者输出

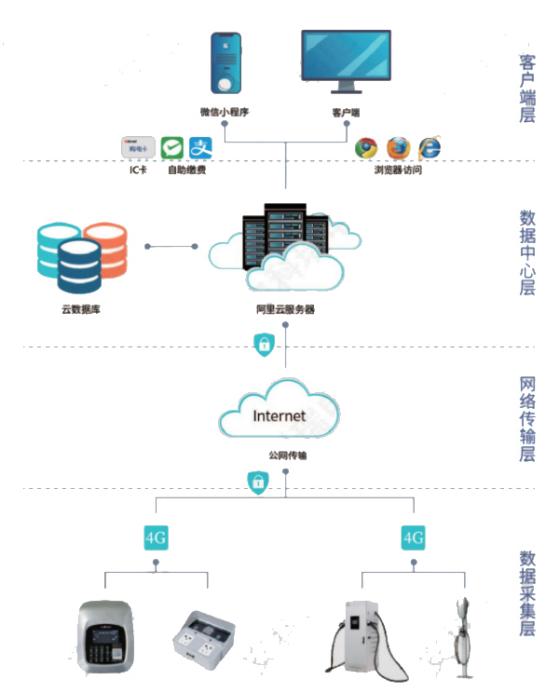

浅谈多目标优化约束条件下充电设施有序充电控制策略

随着电动汽车的普及,充电设施的需求日益增长,如何在多目标优化约束下实现充电设施的有序充电成为亟待解决的问题。新能源汽车的快速发展为清洁能源和可持续交通带来了新机遇,但也引出了许多问题。其中,充电设施的有序充电控制策略在多目标优化约束条件下显得尤为重要。

时序约束一主时钟与生成时钟

的输出,对于Ultrascale和Ultrascale+系列的器件,定时器会自动地接入到GT的输出。 1.2 约束设置格式 主时钟约束使用命令create_clock进行创建,进入Timing

常用时序约束使用说明-v1

为了防止约束失败,我们在Tcl输入框中验证,没有告警或者错误说明约束的写法是正确的set_max_delay 5.00 -from [get_cells key2_detect_inst/state

与非门构成的基本RS触发器的约束条件是什么

触发器的约束条件主要涉及输入信号和输出信号的状态。 以下是与非门构成的RS触发器的一些基本约束条件: 输入信号的约束 : RS = 0 :当R和S都为0时,触发器保持当前状态不变。这是因为两个与非门的输入都是0,输出Q和Q'将保

SR锁存器有约束项的原因

SR锁存器作为数字电路中的一个基础元件,其设计和使用过程中存在约束项的原因是多方面的。这些约束项旨在确保SR锁存器能够稳定、可靠地工作,避免产生不可预测或错误的状态。 一、SR锁存器的基本工作原理

sr锁存器约束条件怎样得出的

,并且能够在输入信号发生变化时保持其输出状态。SR锁存器(Set-Reset Latch)是一种基本的锁存器类型,它由两个交叉耦合的反相器和一个S(Set)输入和一个R(Reset)输入组成。本文将详细介绍SR锁存器的约束条件,以及如何根据这些条件进

XDC约束及物理约束的介绍

XDC约束及物理约束的介绍

评论