人工智能(AI)与机器学习(ML)工作负载(尤其是大语言模型)的指数级增长,正推动高性能计算和AI数据中心架构发生范式转变。对大规模实时推理与训练的需求,不断推动计算和互连技术突破极限。随着模型规模和参数量每四到六个月翻一番,底层基础设施既要提供海量计算吞吐量,还需在数千个加速器之间实现超大的带宽和低延迟的数据传输。

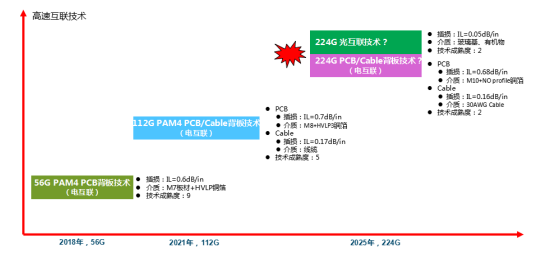

本文从技术层面探讨了在下一代SoC中实现1.6 Tbps端口级无缝互操作性所面临的系统级挑战及应对之策,重点分析了224G串并转换器(SerDes)的作用、新兴的互连协议,并解释了在密集、高速环境中信号完整性和电源完整性的关键作用。

互连挑战:纵向扩展与横向扩展

工作负载需求

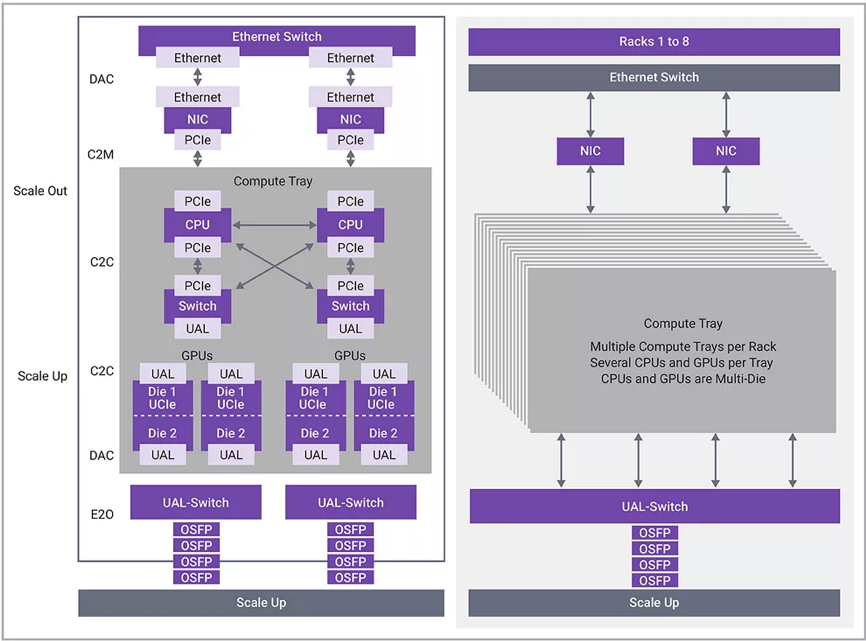

诸如Llama 3之类的最新大语言模型(LLM),在预训练阶段需占用高达700 TB的内存,动用16,000个加速器。单块GPU或单个加速器显然力不从心,必须依赖数万台设备组成紧密耦合的集群方能满足需求。这种体量和规模对网络架构提出了严峻考验,既要支持纵向扩展(机架内部,低延迟)的拓扑结构,又要兼顾横向扩展(机架之间,高带宽)的布局需求。

协议的演进

为满足这些需求,一些新的协议应运而生:

超以太网联盟(UEC):专为横向扩展设计,支持多达100万个节点,提供高带宽、低延迟且不绑定供应商的链路。

超加速器链路(UAL):以纵向扩展为目标,可实现多达1024个加速器的高速、低延迟连接,并支持内存共享和设备直连(D2D)通信。

这两种协议均基于新一代物理层技术:224G SerDes。

▲图1 采用1.6T超以太网和UALink的AI扩展架构

224G SerDes:1.6 Tbps/800Gbps端口的基石

标准和规范

为确保224G SerDes解决方案在全行业范围内实现互联互通且稳定可靠,IEEE、OIF等标准组织正积极制定全面的电气规范和长距离(LR)规范,预计将于2025年完成审定。此外,超以太网1.0版本规范已于近期发布,UALink 200G规范也在今年早些时候正式亮相。这些标准意义重大,提供了一套通用框架,能让不同厂商的组件得以无缝协同,从而进一步推动当今数据中心基础设施的快速部署和扩展。

信道与信号完整性

在224G速率下,奈奎斯特频率相比112G的时候提高了一倍,使得信道损耗与串扰的影响显著增加。在这样的高频环境下,信号路径中的每一个元素,包括PCB走线、连接器和封装等,都会造成更大的损耗。例如,32 AWG双轴电缆在56 GHz时的插入损耗可达约14 dB/m,而典型系统中的总信道损耗更是动辄达到40-50 dB。这种衰减幅度让基于PCB的传统布线方式捉襟见肘,难以满足众多高速链路的需求,因此推动行业采用更加先进的材料和改良的连接器设计,并引入飞线电缆等替代方案,以力保信号完整性。

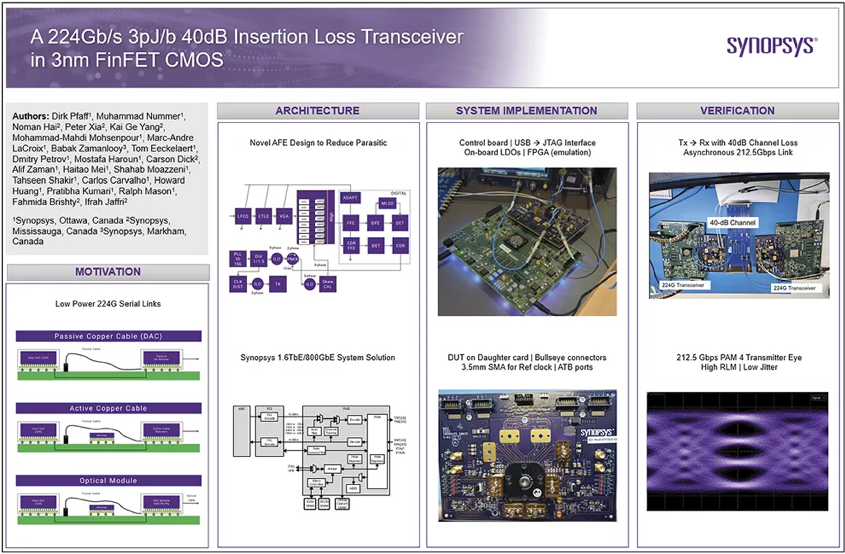

在224G速率下维持稳定的数据传输,需要借助先进的数字信号处理(DSP)和均衡技术来补偿严重的信道损耗。当前的SerDes架构包含以下组件:

高性能前馈与决策反馈均衡(FFE/DFE)

最大似然序列检测(MLSD)

这些接收器模块协同发力,即便在复杂环境中也能确保眼图张开且误码率(BER)处于较低水平,前向纠错(FEC)前的误码率目标比1E-4还要低几个数量级。DSP必须具备灵活的适应性,以支持短距离(芯片到模块)和长距离(背板、飞线或光链路)信道。

224Gbps速率下的架构需求和DSP升级

在更高的速率水平下,SerDes架构中的每个模块都需提质增效。模拟前端(AFE)需要更高的带宽,模数转换器(ADC)则必须实现更低的噪声性能。由于单位间隔(UI)缩短,锁相环(PLL)的抖动容限变得愈发严苛;而DSP必须提供强大的均衡能力来补偿45 dB的信道损耗,通常需借助最大似然序列检测(MLSD)等先进技术来实现。重要的是,即便交换机和加速器集成了200多条SerDes信道,性能上的改进也不能以功耗的同步增加为代价。

▲图2 在ISSCC 2024大会上探讨了新思科技224G架构的进展。

系统级仿真在提升互操作性方面的作用

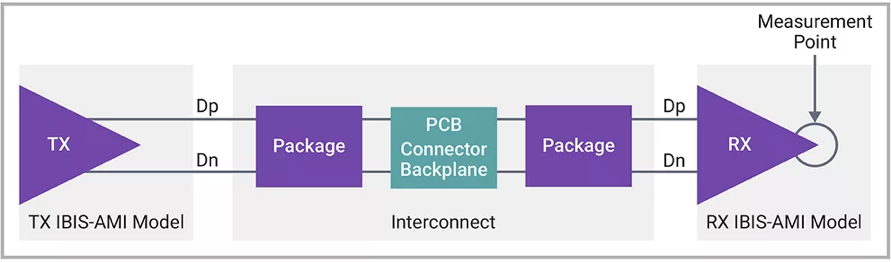

在硬件就绪前,系统开发者需依靠全面的仿真环境来预测和优化性能。这些仿真需要对整个信号路径进行建模,包括:

发射器IBIS-AMI模型

完整的封装提取,涵盖数百条信道的近端与远端串扰

互连建模,涉及PCB走线、连接器、飞线电缆乃至光链路

接收器IBIS-AMI模型

仿真环境使开发者能够评估信号完整性、串扰以及多信道同时切换所带来的影响。通过构建一个从发射器到接收器(包含所有中间互连环节)的虚拟系统,开发者能够预测接收器能否获得张开的眼图及可接受的误码率(BER)

▲图3 为确保224Gbps信号通过互连链路(如封装、PCB、连接器、背板等)从发射端(TX)到接收端(RX)实现无差错传输,必须进行信号完整性(SI)分析。

从仿真到芯片互操作的关键指标与裕量分析

一项核心指标是前向纠错(FEC)前的误码率(BER),其规范要求通常要高于1E-4。然而,稳健的系统设计需要在工艺、电压和温度(PVT)变化范围内保留裕量。仿真还需评估前向纠错(FEC)的实际效能,通过对比所有PVT极端条件下的FEC前与FEC后误码率,确保系统在最坏情况下仍能可靠运行。

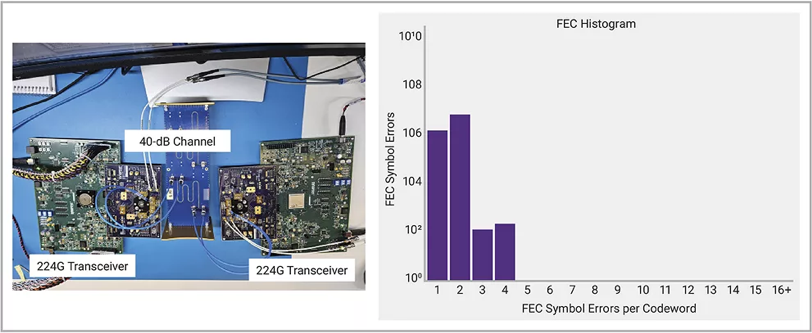

硬件验证与信道特征分析

当芯片就绪后,需结合实际硬件对模型进行验证。例如,对于224G SerDes,需使用实际芯片、互连链路和电缆,对损耗达40–45 dB的系统信道进行特征分析。同时测量近端与远端串扰,并将结果与仿真预测值对比,以闭环验证模型的准确性。

▲图4 在SI分析中,应使用PHY SI模型(包括TX/RX IBIS-AMI、芯片S参数)和互连模型(优选S参数格式)。

SerDes的性能无法孤立评估。必须通盘考量整个系统,包括互连链路、电缆、连接器、封装和PCB。

要在高性能计算(HPC)环境中正常运行,仅按照IEEE或OIF规范设计SerDes,并依据电气规范来测试发送端(TX)的合规性或接收端(RX)抖动容限(JTOL)显然远远不够。SerDes需要与生态系统供应商通力协作,为系统集成商提供经过预先测试和验证的解决方案,确保组件部署到机架并形成连接后能够实现无缝集成。例如,与高密度电缆组件、OSFP可插拔模块、1-2米直连铜缆(DAC)、来自不同厂商的近芯片NPC、CPC组件(损耗达45-50 dB)进行互操作性测试,可为机架内部及机架间连接路径的真实场景系统验证奠定坚实基础。这些互操作性测试可确认SerDes与互连链路、封装、PCB形成的端到端信道能够协同运转,从而在HPC系统中达到所需性能。

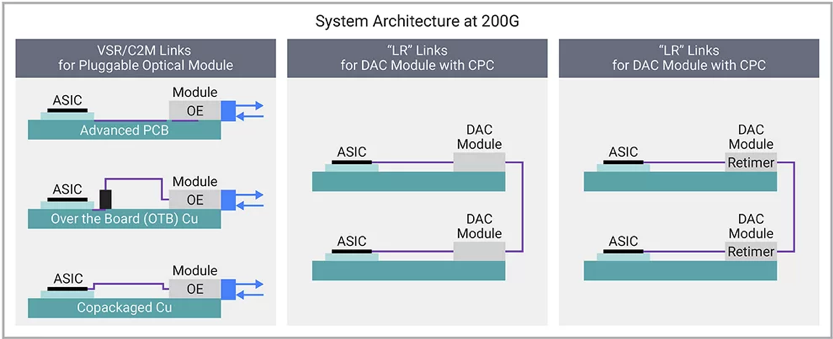

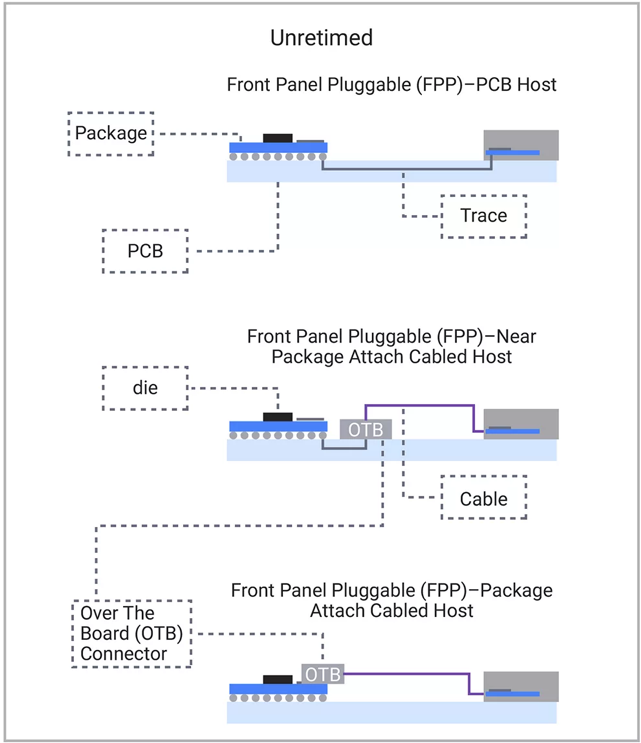

▲图5 采用224G SerDes的C2M VSR与LR机架到机架连接

展望未来:448G及以上速率

随着行业将目光投向224G之外,向448G SerDes的过渡已悄然启动。这一跨越式升级不仅需要将数据速率提升一倍,更需重新构思调制方案与信道定义,以应对新频率下特有的挑战。

调制方式和信道演进

铜互连:对于448G铜介质传输,行业正逐步采用PAM-6调制方式,奈奎斯特频率约为86.7 GHz。OIF和IEEE等标准组织正积极为短距离、中距离和长距离应用制定新的信道规范,以确保在各类部署场景下实现稳定性能。

光链路:在光信道中,PAM-4调制凭借经实践检验的高频性能和信号完整性(奈奎斯特频率约为112 GHz),预计仍将作为标准方案,能够在满足更高数据速率需求的同时,兼顾光组件设计与部署的实际可行性。

光信道特性将决定PHY调制方式与复杂度,反之亦然。

▲图6 具有互操作性互连拓扑的448G系统

向448G的演进,将全方位加码对系统各环节的要求,从先进材料、连接器技术,到更为复杂的DSP与均衡技术,都要更进一步。电力传输、散热管理与系统集成领域也都需要推陈出新,才能在更高的速率下维系信号完整性与能效水平。

结语

在下一代HPC和AI/ML SoC中实现1.6 Tbps的无缝互操作,是一项复杂的跨学科挑战,远超SerDes设计的范畴。要取得成功,需依赖以下几个方面:

创新的SerDes架构:集成先进的均衡技术、自适应DSP和高能效设计,以攻克信道损耗严重的难题。

高性能互连:综合运用铜介质和光技术,同时密切关注整个系统的信号完整性与电源完整性。

全面的系统建模与验证:采用严谨的仿真和硬件验证手段,确保系统在各种条件下都能稳定运行。

生态系统协作:在芯片、封装、互连和系统集成等领域建立紧密合作关系,以加速推进创新与部署进程。

随着224G SerDes解决方案投入量产,448G技术也已崭露头角,行业已具备充分条件,能够为下一代AI和HPC的发展提供所需的带宽、可扩展性与可靠性。为在今后取得持续的进步,不仅要依靠整体的系统工程设计、健全的标准制定,还有秉持对互操作性的不懈追求。唯有如此,才能确保未来的数据中心能够跟上人工智能和高性能计算不断增长的需求。

新思科技224G PHY IP可满足高性能数据中心应用日益增长的高带宽和低延迟需求,凭借先进的设计、分析、仿真和测量技术,具备优越的信号完整性和抖动性能,不仅超出IEEE 802.3和OIF标准的电气规范要求,而且支持UALink 200G协议。

-

转换器

+关注

关注

27文章

9198浏览量

153139 -

soc

+关注

关注

38文章

4434浏览量

224097 -

新思科技

+关注

关注

5文章

888浏览量

51942

原文标题:迈向448G:SerDes解决方案助力下一代SoC实现1.6 Tbps无缝互操作

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高通下一代顶级SoC骁龙855,以打造下一代5G设备

古希腊掌管224G 的神 | Samtec 224G PAM4 高速互连大合集!

展望未来英特尔FPGA设计,介绍新型224G PAM4收发器

新思科技应对人工智能(AI)系统级芯片提出下一代架构探索解决方案

基于5G网络和云服务的下一代Samtec汽车解决方案

新思科技助力基于下一代Armv9架构的SoC设计成功

是德科技推出助力片上系统(SoC)制造商验证新一代电气接口技术

新思科技系统级解决方案赋能Arm全新计算平台,携手加速下一代移动SoC开发

浅谈下一代数据中心中的224G PAM-4架构

224G 高速互联对 PCB 及覆铜板需求及激光锡球植球机的助力(上)

224G 高速互联对 PCB 及覆铜板需求及激光锡球植球机的助力(下)

448G的路径 | Samtec与Cadence合作的224G测试平台具备可扩展性、成本优势

第一个?国产224G高速产品实现量产!

新思科技224G SerDes解决方案助力下一代SoC设计

新思科技224G SerDes解决方案助力下一代SoC设计

评论