以下文章来源于郝旭帅电子设计团队,作者郝旭帅

本篇主要讨论vivado进行仿真时,GSR信号的理解和影响。

利用vivado进行设计xilinx FPGA时,写完设计代码和仿真代码后,点击run simulation(启动modelsim进行仿真)。

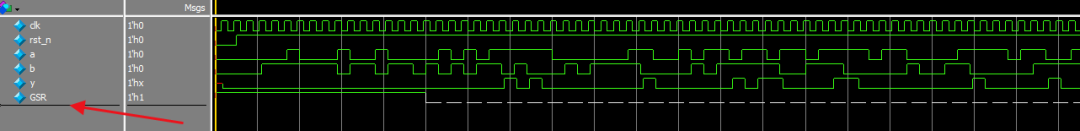

除了能够看到我们所写的仿真代码中的信号外,还会看到一个GSR信号,前面等于1,在100ns左右变为0的虚线。

为什么会有这个信号?

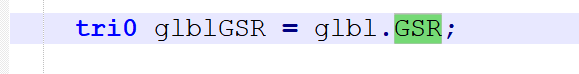

vivado在启动仿真时,会默认添加一个文件:glbl。GSR信号就在这个当中。

有什么影响吗?

一般来说:在进行仿真时,都是直接将其删除,或者直接选择忽略他,并不影响任何东西。

那么这个信号的意义是什么呢?

感觉好像是无意义的。

有一天在进行时序仿真时,发现了一个bug。

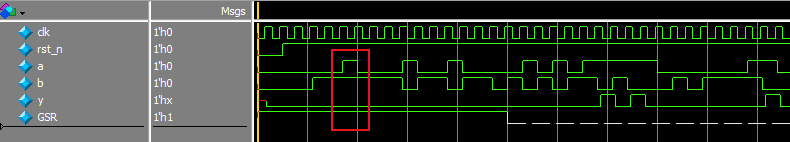

上图是一个时序逻辑(异步复位的寄存器)输出的与门逻辑,在GSR为高电平期间,a和b都为高电平了,y应该输出高电平,但是并没有。而在GSR为0期间,y输出都是正常的。

那么感觉就有可能是GSR的问题。

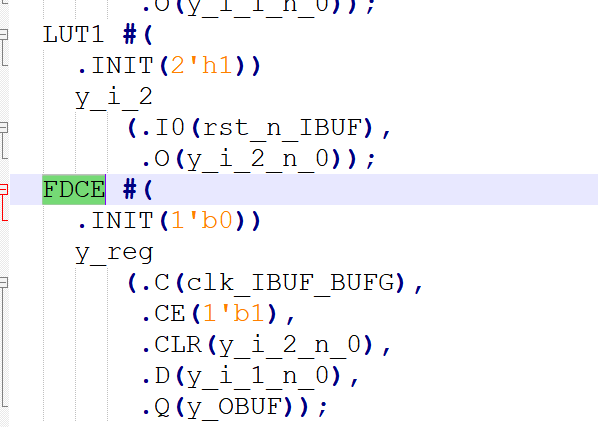

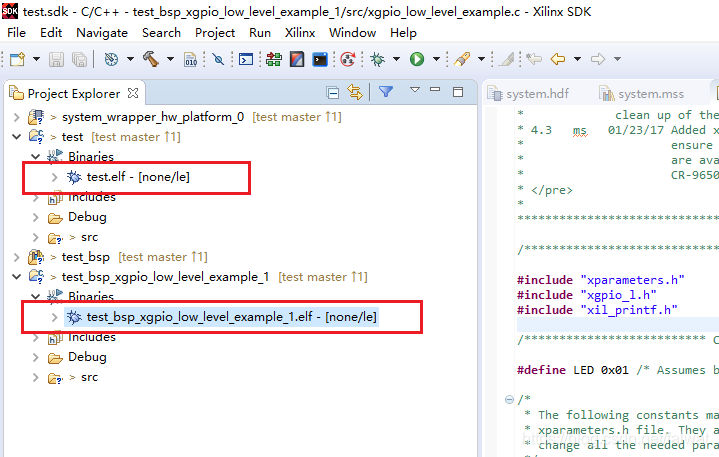

找到时序仿真的文件,内部是使用FPGA器件内部的部件所组成的电路。(找到仿真库,找到仿真所使用的文件)

注:后仿真使用的不是咱们所写的verilog文件,而是经过综合之后的文件。

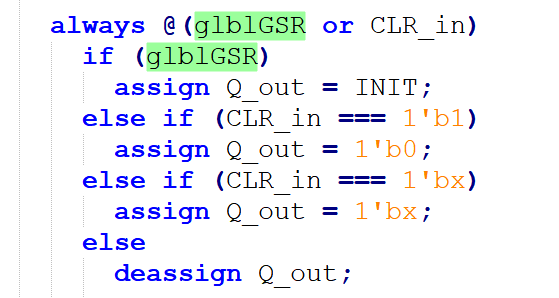

再次通过寻找库文件(在unisims库中),找到FDCE的文件内部。

发现这个这个fdce是和GSR信号有关系的。

也就是说在GSR为高电平期间,输出值一直是默认值,不会随着D信号的改变而改变。

那怎么办呢?

要不然去修改GSR信号拉低的时间,要不然去推后我们仿真时,信号有效的位置。

建议:我们做仿真(特别是时序仿真)时,复位的时间大于100ns(给予有效信号的时间放到100ns之后)。

简单解析GSR:FPGA内部的一个全局复位信号,用于强制寄存器状态。

在 Vivado 仿真中,GSR 信号是理解设计初始化(时间零行为)和全局复位的核心。仿真器默认会在 t=0 激活 GSR 一段时间,模拟 FPGA 配置完成后的硬件行为,将所有受控寄存器强制设置到它们的初始状态。之后 GSR 释放,用户设计的逻辑(包括用户复位信号)才开始正常运行。在波形中观察 glbl.GSR 的时序以及寄存器在 t=0 附近的变化,是验证设计启动和复位行为是否符合预期的关键步骤。除非有特殊调试需求,一般不应禁用或修改默认的 GSR 仿真行为。

-

仿真

+关注

关注

52文章

4332浏览量

136594 -

信号

+关注

关注

11文章

2863浏览量

78836 -

Vivado

+关注

关注

19文章

837浏览量

69492

原文标题:vivado进行仿真时,GSR信号的理解和影响

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何用Python实现Vivado和ModelSim仿真自动化?

基于VB的GSR实时信号监护系统

Vivado软件仿真DDS核的过程中应该注意的问题

Vivado下的仿真详细过程

如何使用Vivado中的Synopsys VCS仿真器进行仿真

Vivado调用Questa Sim或ModelSim仿真小技巧

vivado仿真时GSR信号的影响

vivado仿真时GSR信号的影响

评论