文章来源:学习那些事

原文作者:小陈婆婆

本文主要讲述3D封装与CoWoS封装。

集成扇出(InFO)

自戈登·摩尔1965年提出晶体管数量每18-24个月翻倍的预言以来,摩尔定律已持续推动半导体技术跨越半个世纪,从CPU、GPU到专用加速器均受益于此。

如今这一规律正从单一晶体管缩微(1.0时代)向晶圆级系统集成(WLSI)的2.0时代演进——通过将超大芯片拆解为独立功能单元,结合2D/3D封装与硅通孔、扇出等前沿技术,在保持甚至加速晶体管密度增长的同时,实现性能、功耗、面积与成本(PPAC)的协同优化。

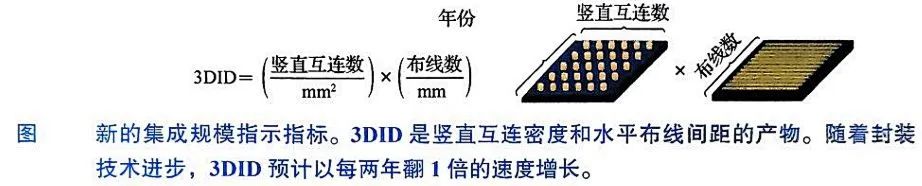

新指标3D互连密度(3DID)的提出,更量化了系统级封装的扩展能力,配合SoIC等颠覆性3D集成技术,正为摩尔定律的持续生效注入新动能,开启半导体技术指数级增长的新篇章,本文分述如下:

3D封装和片上集成系统(SoIC)

CoWoS封装

3D封装和片上集成系统(SoIC)

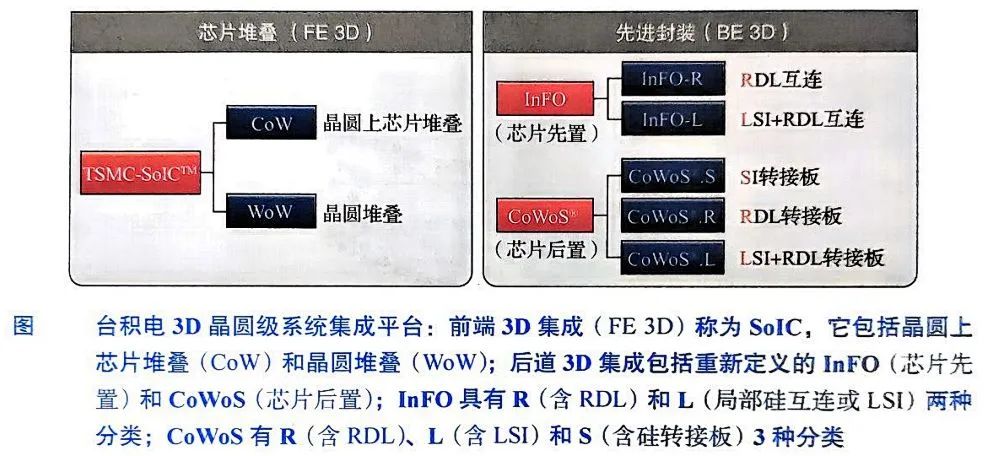

在半导体系统集成领域,3D Fabric技术平台的演进正推动封装工艺从单一互连方案向多维协同架构跨越。作为晶圆级集成技术的集大成者,3D Fabric通过整合扇出型互连(InFO)、硅转接板集成(CoWoS)及晶圆级系统集成(SoW/SoIS)等模块化工艺,构建起覆盖前端制造与后端封装的完整技术生态。

其中,InFO技术以芯片预嵌入为核心,通过扇出型重布线层实现高密度横向扩展,其工艺流程本质在于先固定芯片位置再构建互连网络,这种"芯片先行"的策略为复杂系统提供了灵活的布局空间;而CoWoS则采用"再布线优先"的逆向思维,在芯片贴装前完成多层高密度互连结构的沉积,结合硅转接板的垂直贯通能力,有效平衡了信号完整性与热管理需求。

值得注意的是,实际生产中两者并非非此即彼的选择,通过混合集成模式——部分芯片采用InFO方式嵌入,其余模块通过CoWoS实现精密对接——系统架构师得以在局部互连密度、芯片形貌适配及散热路径优化间找到最佳平衡点,这种工艺组合的灵活性在异构计算时代尤为重要。

作为3D Fabric体系中的颠覆性技术,片上集成系统(SoIC)将前道制造工艺引入封装领域,通过晶圆级键合技术实现多芯片的垂直堆叠与无缝集成。其核心优势在于,通过预先对不同工艺节点、不同材料体系的芯片进行严格测试(KGD筛选),确保堆叠单元的功能可靠性,再利用类似前端制程的铜互连技术(节距密度媲美后道铜布线),在微米级甚至亚微米级尺度上实现芯片间的等效单片化集成。这种前道与后道工艺的深度融合,不仅使SoIC集成的多芯片系统在电气性能、机械稳定性上达到传统SoC水准,更通过模块化设计大幅缩短产品迭代周期。当前,SoIC技术已与CoWoS、InFO等后道工艺形成技术闭环,构建起从芯片级到系统级的多维集成解决方案。

CoWoS封装

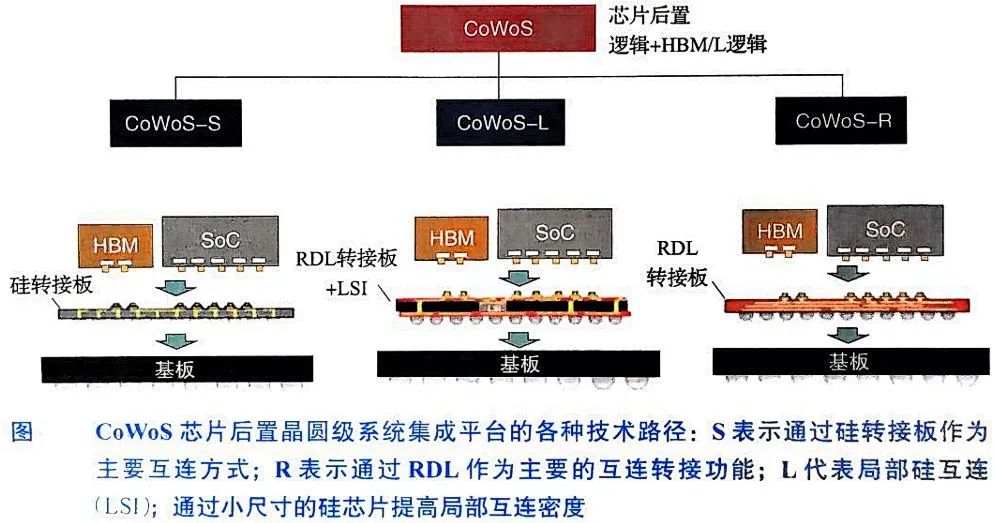

在先进封装领域,CoWoS(Chip-on-Wafer-on-Substrate)技术平台通过模块化设计,构建了覆盖高密度互连、成本优化与异构集成需求的多维解决方案。作为芯片后置工艺的典型代表,CoWoS体系通过预布线层(RDL)与转接板技术的深度融合,实现了从芯片级到系统级的精准性能调控。

CoWoS-S作为基础架构,依托硅转接板(Silicon Interposer)实现芯片间的高密度互连。其核心优势在于硅基材的高热导率与低介电损耗特性,可支持微米级节距的TSV(硅通孔)与微凸点互连,单块转接板即可实现超过1000个I/O通道的密集走线。更值得关注的是,有源转接板技术的引入使硅基板不再局限于被动互连角色——通过集成嵌入式电容、电感或射频模块,该平台可有效缩短信号传输路径,降低寄生效应对高速串行链路(如PCIe 5.0/6.0)的影响。据台积电2024年技术论坛披露,其5nm CoWoS-S工艺已实现转接板层数突破至8层,互连密度达每平方毫米10万个连接点,成功支撑英伟达Hopper架构GPU与Grace CPU的异构集成。

针对成本敏感型应用,CoWoS-R平台以RDL(重布线层)替代硅转接板,通过有机基板上的铜布线实现芯片互连。尽管其线宽/线距(L/S)通常维持在2μm/2μm级别,较硅转接板的1μm/1μm稍显宽松,但有机基材的低成本与易加工特性使其在加速器领域获得广泛采用。AMD MI300系列APU即采用该技术,通过RDL层将GPU与HBM内存垂直堆叠,在保持1.2TB/s带宽的同时,将封装成本降低30%。值得补充的是,三星近期公布的X-Cube 3D技术亦采用类似RDL方案,但其通过混合键合(Hybrid Bonding)将互连节距压缩至4μm,在成本与性能间形成新平衡点。

在需要局部高密度的复杂系统中,CoWoS-L平台通过嵌入式LSI(局部硅互连)芯片解决了传统RDL的密度瓶颈。该技术将微型硅桥接片嵌入RDL层中,在特定区域实现亚微米级互连(如0.8μm节距),同时保留有机基板的大面积布局优势。英特尔在Ponte Vecchio GPU中采用的EMIB(嵌入式多芯片互连桥接)技术即属此类,其LSI芯片通过预先植入的深沟槽电容(DTC)有效抑制电源噪声,使多芯片系统在200W功耗下仍能维持1.2V的核心电压稳定度。行业动态显示,台积电正将CoWoS-L与SoIC技术结合,开发出支持3D堆叠与2.5D互连的混合架构,预计2025年量产的CoWoS-L Gen2工艺将实现LSI芯片与RDL层的无缝集成,进一步缩小先进封装与单片SoC的性能差距。

从技术演进路径看,CoWoS平台正通过材料创新与工艺解耦持续拓展边界。硅转接板向玻璃基板的过渡研究已进入实操阶段,玻璃基板的高平整度与超薄化特性可支持更精密的TSV制造;而RDL层与LSI芯片的协同设计,则推动封装从被动互连向主动功能集成转型。这些进展共同印证了先进封装技术正在从"连接载体"演变为"系统赋能者",为摩尔定律的延续提供关键支撑。

-

半导体

+关注

关注

335文章

29196浏览量

242717 -

晶体管

+关注

关注

77文章

10056浏览量

142693 -

3D封装

+关注

关注

9文章

145浏览量

27939 -

CoWoS

+关注

关注

0文章

157浏览量

11184

原文标题:集成扇出(InFO)应用——3D封装与CoWoS封装

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

浅谈3D封装与CoWoS封装

浅谈3D封装与CoWoS封装

评论