博客作者:Dario Fresu

欢迎来到 “掌握 PCB 设计中的 EMI 控制” 系列的第五篇文章。在本文中,我们将深入探讨电源分配策略,并讨论如何对其进行优化,以在您的 PCB 项目中实现更优的 EMI 性能。

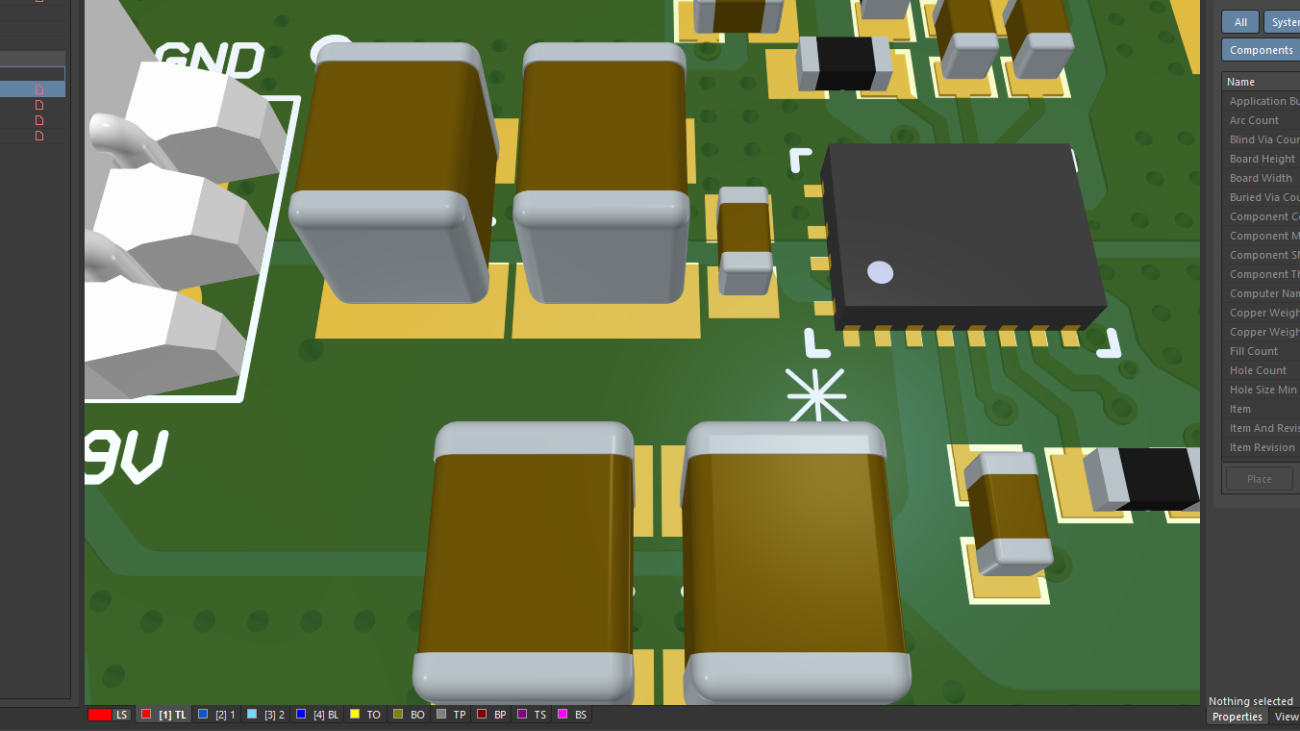

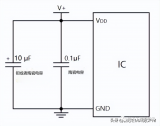

图 1:Altium Designer 中的去耦策略示例

这一环节之所以至关重要,是因为它与 PCB 设计中电磁场的约束紧密相关。

在数字印刷电路板上控制 EMI 并提升信号完整性的关键因素之一是实施有效的去耦策略。这些方法可确保电路板上的集成电路获得干净、稳定的能量供应。

为此,PCB 设计师需要构建强大的电源传输网络,以满足高速切换 IC 的能量需求,确保其从电源获取适量电流。设计一个高效、及时传输能量的 PDN 颇具挑战,需减少损耗并满足高性能阻抗要求。

随着数据速率和信号速度不断提升,设计低阻抗 PDN 变得愈发重要且困难 —— 阻抗曲线与传输信号的频率密切相关,平衡这些因素是维持 PCB 高性能并最小化 EMI 问题的关键。设计高效 PDN 时,常用技术包括集成去耦电容,或在叠层中使用电源平面和多边形铺铜。

然而,一些被广泛接受的方法和误区已被证明不仅无效,甚至会损害电路板性能。

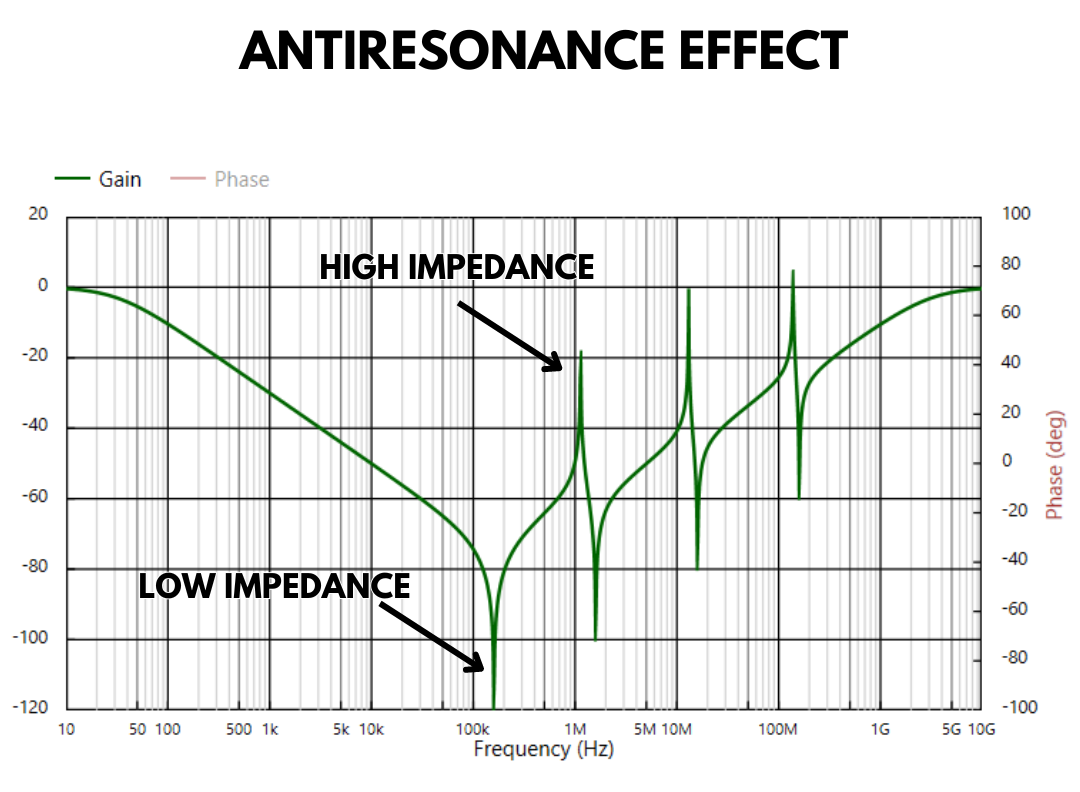

反谐振现象

一种常见技术是使用多种容量的电容器(通常在 10nF 至 1?F 范围内),理论上大电容为 IC 提供能量,小电容滤除高频噪声。尽管这一思路看似合理,但在试图降低 PDN 整体阻抗时可能适得其反 —— 实际电容器并非理想器件,其寄生效应在高频下会显著影响性能。

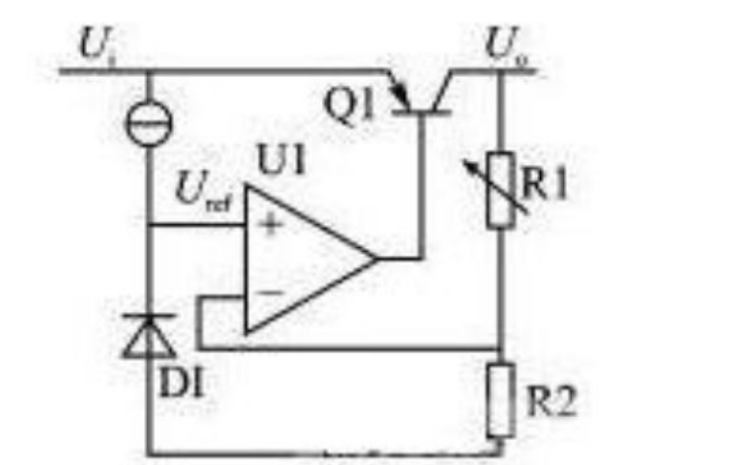

电容器仅在谐振频率以下表现为容性阻抗,超过此频率后,封装内的寄生参数会主导阻抗,使电容器呈现感性特性。使用不同容量的电容器以追求更高总电容和更低阻抗时,会面临显著挑战:每个电容器因特性差异具有独特的阻抗曲线,且谐振频率不同,导致阻抗曲线重叠,在特定频率下产生更高的阻抗峰值(见图 2)。

图 2:反谐振 —— 并联不同阻抗曲线的电容器的影响。

这些不同谐振频率的相互作用会导致阻抗升高,对 PDN 整体性能和去耦策略效果产生负面影响。

解决这一问题的更佳方案是使用相同类型和封装、引线电感尽可能低的 SMD 电容器。并联这些电容器可满足电容需求,同时将高频下的电感降至最低。此外,交替电容器引线极性可减少互感,进一步降低 PDN 的总电感。

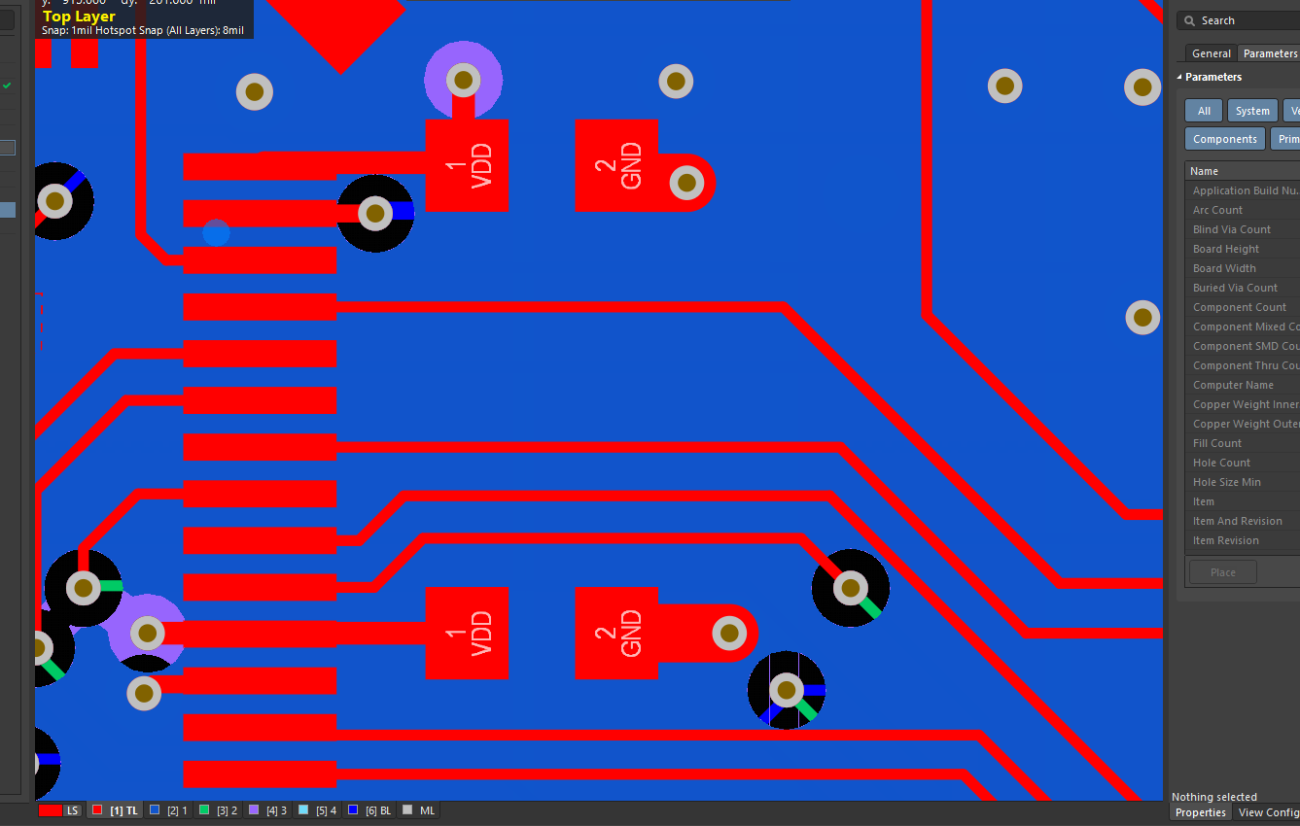

电容器布局

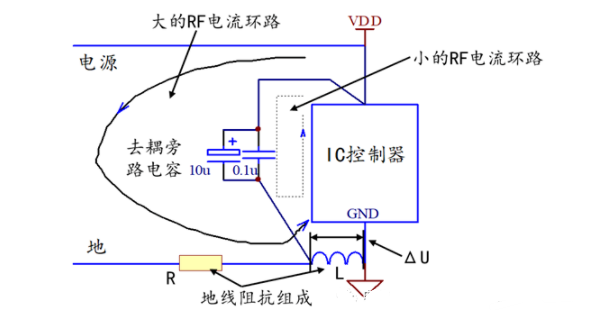

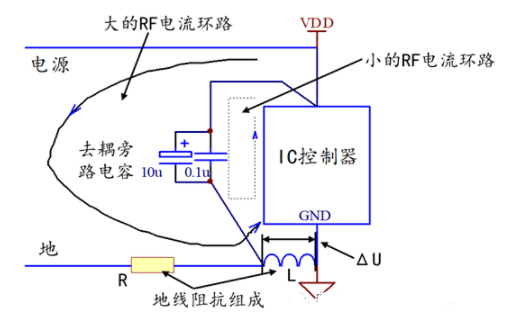

布局去耦电容器时,必须应对电感问题 —— 信号频率越高,电感影响越显著。为此,电容器应尽可能靠近消耗电流的 IC 电源引脚,以缩短电流路径,减少高频下阻碍性能的电感效应。

设计师的核心关注点不应局限于电流的物理传输距离,而应仔细规划电流的具体路径。尽管缩短去耦电容与连接引脚的距离很重要,但其本质是为了最小化走线的寄生电感 —— 这种近距离布局可确保电容器有效向 IC 提供所需电荷,稳定电源并维持信号完整性(见图 3)。

图 3:Altium Designer 中 IC 旁的去耦电容布局示例

因此,优化路径(而非仅缩短距离)可确保电流以最高效率流动,降低 EMI 风险并提升整体电路性能。恰当的路径规划与距离优化同样关键,两者直接影响可能损害电路稳定性和功能的寄生效应。

恰当的路径规划与距离优化同样关键,两者直接影响可能损害电路稳定性和功能的寄生效应。

除确保电容器靠近 IC 外,强烈建议选择 ESR 尽可能低的电容器。ESR 是关键参数,直接影响电容器滤除高频噪声的效率 —— 低 ESR 可降低电容器与 IC 电源引脚之间的总阻抗,更有效抑制电源线的电压波动和噪声。此外,低 ESR 电容器在更宽频率范围内性能更优,进一步助于减少 EMI 并提升设计的电源完整性。

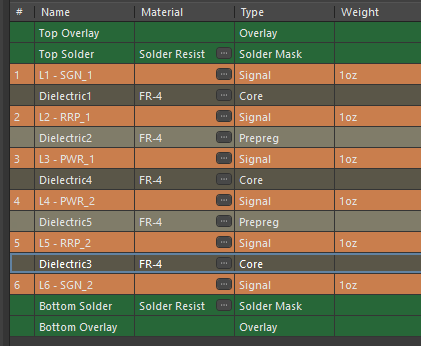

电源平面设计

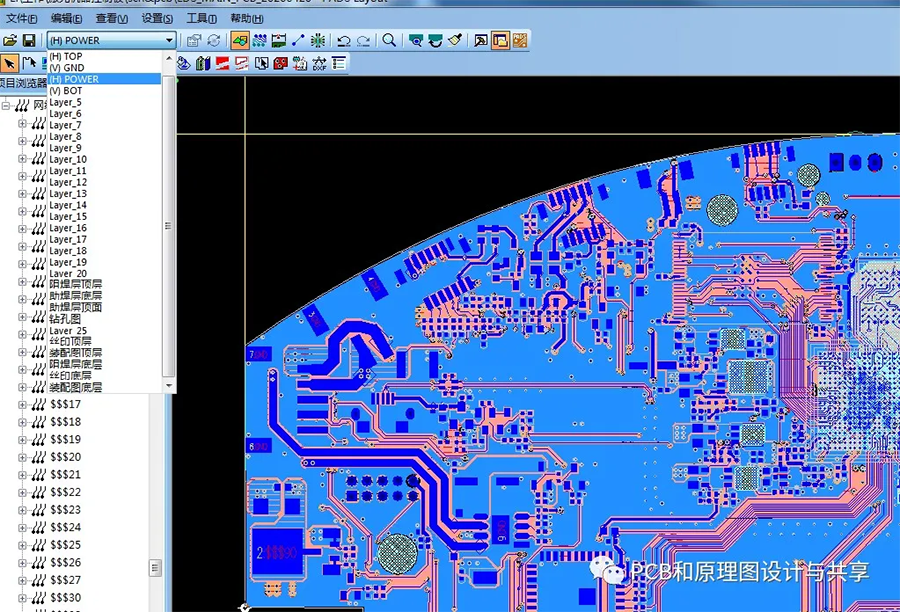

设计多层 PCB 时,建议在叠层内将电源平面与返回参考平面(通常称为 “地” 平面)成对紧密排布。这种布局可增加平面间的分布电容,从而降低 PDN 的整体阻抗。

理想配置是将信号层紧邻返回参考平面(“信号地”),使返回电流以最小环路面积流动,约束信号产生的电磁场,控制 EMI 并减少噪声。这种设置可显著提升信号完整性,降低走线间的串扰和电磁耦合,确保更高信号质量和可靠通信。在返回参考平面另一侧布置电源平面,可确保电源平面有效向 IC 供电,避免高速切换信号产生的噪声干扰。通过将电源平面与信号层分离,同时保持与返回参考平面的紧密耦合,可抑制噪声耦合并为电源传输创造稳定环境,最终保障整个电路的高效运行。这种布局同时增强电源完整性和信号完整性,是高性能多层 PCB 的基础设计实践(见图 4)。

图 4:Altium Designer 中优化的 6 层叠层示例

结合 IC 电源引脚旁的本地电容器与紧密排布的电源和地平面,可形成完整解决方案 —— 改善 PDN、降低 EMI 并维持电路板整体更高信号质量。此外,这种方法有助于在 PCB 上更均匀地分配电源,并减少传统电源布线方式可能产生的电感。

通过将布局合理的电容器与间距紧凑的电源和地平面相结合,可构建更可靠、高效的电源分配系统,确保 PCB 性能优异且免受干扰。

下一篇文章我们将深入探讨串扰抑制,重点介绍 EMI 实践,探索最小化信号间干扰、确保 PCB 设计中更纯净可靠通信的策略。

总结

在进行 PCB 设计时,Altium Designer 提供了一套全面的工具,可简化 PCB 设计师的工作流程,并帮助您构建高效的 PDN 。Altium Designer 的核心功能之一是层堆栈管理器,该工具可根据系统的特定需求为您的 PCB 选择优选叠层配置。

此外,Altium Designer 包含功能强大的集成工具,支持对 PDN 进行详细仿真。这些仿真可帮助您分析并明智地决定如何有效改进电路板设计。

若想提升您的 PCB 设计项目水平并利用这些先进工具,我们鼓励您开启 Altium Designer 和 Altium 365 的免费试用。

这将使您有机会亲身体验这款完整的 CAD 工具如何增强您的设计能力,实现更高效的 PCB 设计。

关于Altium

Altium有限公司隶属于瑞萨集团,总部位于美国加利福尼亚州圣迭戈,是一家致力于加速电子创新的全球软件公司。Altium提供数字解决方案,以最大限度提高电子设计的生产力,连接整个设计过程中的所有利益相关者,提供对元器件资源和信息的无缝访问,并管理整个电子产品生命周期。Altium生态系统加速了各行业及各规模企业的电子产品实现进程。

-

emi

+关注

关注

53文章

3780浏览量

131849 -

altium

+关注

关注

48文章

985浏览量

120644 -

PCB设计

+关注

关注

396文章

4827浏览量

91185 -

Designer

+关注

关注

0文章

137浏览量

36718

原文标题:【技术博客】掌握 PCB 设计中的 EMI 控制之 PDN 去耦策略

文章出处:【微信号:AltiumChina,微信公众号:Altium】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PCB的电源分配网络设计

电容时常数PDS去耦网络的自动实现

PCB PDN design guidelines (PCB电源完整性设计指导) ------PCB去耦准则

PCB电源分配网络的去耦策略

PCB电源分配网络的去耦策略

评论