文章来源:学习那些事

原文作者:前路漫漫

本文介绍了3D封装的优势、结构类型与特点。

3D 封装的优势与发展背景

近年来,随着移动通信和便携式智能设备需求的飞速增长及性能的不断提升,对半导体集成电路性能的要求日益提高。然而,当集成电路芯片特征尺寸持续缩减至几十纳米,乃至最新量产的 5nm 和 3nm 时,摩尔定律的进一步发展遭遇瓶颈。传统 2D 封装因互连长度较长,在速度、能耗和体积上难以满足市场需求。在此情况下,基于转接板技术的 2.5D 封装,以及基于引线互连和 TSV 互连的 3D 封装等应运而生,并迅速发展起来。

3D 封装采用与 2D 封装不同的横向互连方式,缩短了互连长度,具有诸多优势:

(1)能有效利用立体空间,提高封装密度,减小封装体积。封装向 Z 方向发展,节省了 XY 平面的封装面积,与传统封装相比,采用 3D 技术可使尺寸缩小,质量减为原来的 1/50-1/40。

(2)可集成多种芯片和微电子机械系统(MEMS)器件等,有利于实现多功能、更大规模的集成。

(3)缩短了引线长度,降低了寄生电容和电感,提高了信号传输速度。

(4)寄生电容和电感的降低在提升性能的同时,进一步降低了能耗。

(5)节省了封装、组装及系统所需的材料。

3D 封装的结构类型与特点

从互连结构来看,3D 封装可分为封装堆叠、芯片堆叠、芯片埋入、封装内封装、双面封装、通过转接板互连等基本实现形式。这些基本形式可以组合,例如堆叠的封装内某个封装体内部可由多个芯片堆叠,其封装基板内也可埋入芯片。

1.封装堆叠

封装堆叠包括引线框架堆叠、无引脚陶瓷片式载体堆叠、TAB 引线堆叠、基于焊球互连的堆叠 BGA、柔性载带折叠封装、侧面图形互连堆叠等形式。

高密度 3D 堆叠最适用于内存,或底部有高 I/O 数器件(微处理器、DSP、ASIC)的内存。

封装堆叠的优点是单层封装经过测试,有助于提高 3D 封装的良率,且基于现有封装平台较易实现。封装堆叠对单层封装的要求是厚度较薄,若采用回流方式堆叠,封装需能承受多次回流的高温。

由于封装堆叠需要单个芯片的完整封装,因此在封装过程中并未节约成本。

对于周边引脚类型封装,堆叠后信号仍需绕经封装边缘进行互连,其信号路径缩短的效果比芯片堆叠等形式差。

2.芯片堆叠

芯片堆叠是指在单个封装体内部堆叠多颗芯片。其互连方式主要有基于焊线的堆叠、基于倒装 + 焊线的堆叠、基于硅通孔的芯片堆叠、薄芯片集成、芯片堆叠后埋入等。

芯片堆叠面临的主要挑战是芯片良率和热管理。“已知良好的芯片” 比封装体测试更困难,且封装堆叠的产热密度更高。

手机和其他便携式产品中的多个芯片堆叠已大量生产,堆叠芯片的数量也呈上升趋势。随着芯片变薄,堆叠芯片封装的厚度并不比传统单芯片封装厚。与单独封装后再互连相比,芯片堆叠缩短了信号路径长度。

3.芯片埋入

芯片埋入是指将芯片嵌入封装基板结构内部,可通过模压或塑封等方式实现。

模压芯片埋入的具体工艺过程与 FOWLP 工艺相同。层压工艺本文不做介绍。塑封芯片埋入采用环氧树脂模塑料对芯片进行包封,通常用模压成型工艺进行塑封,模压芯片埋入后通过再布线、扇出通孔(TIV)实现垂直互连。层压工艺中使用半固化片,层压工艺芯片埋入后通过激光钻孔和布线工艺实现垂直互连。采用埋入方式能进一步提高封装的集成度,缩小封装尺寸,大幅缩短互连尺寸并提升器件性能。

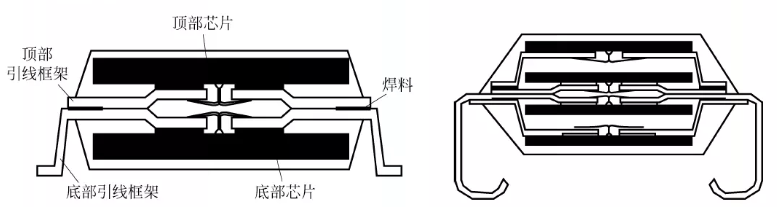

4.封装内封装

封装的成品率与已知良好芯片的测试结果密切相关。封装内封装(Package in Package,PiP)是把经过预测试的封装整合到 3D 堆叠结构中的技术。顶部封装与底部封装基板的连接采用导线键合的方式。2004 年,Flynn Carson 与 Young-Cheol Kim 曾提出 PiP 形式的 3D 封装结构,其做法是将两个已完成测试的封装进行堆叠,上层封装背面的焊盘与下层封装基板上的焊盘通过焊线实现互连,之后再进行进一步的塑封和植球操作,最终形成 BGA 或 FPBGA 封装。上层封装内部为芯片堆叠结构。

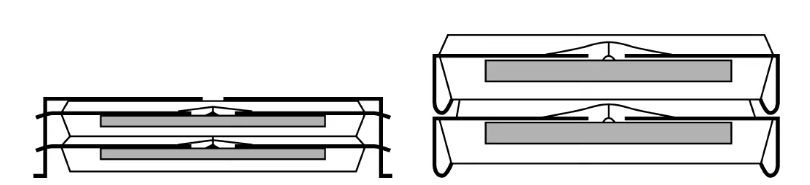

5.双面封装

双面封装指的是将芯片分别贴装在同一引线框架或基板正反两面的封装结构。采用引线框架的塑料封装双面封装为双面引线键合形式。基板型的双面封装则可以有多种形式,包括双面引线键合、双面倒装,或者引线键合与倒装相结合的混合形式。

对于双面塑料封装,需先完成正面的塑封工作,再进行反面的封装操作。

6.混合类型 3D 及其他封装

互连的形式丰富多样,上述分类可能不够全面。而且在实际应用中,并非仅采用单一的互连形式,而是会根据实际需求和工艺特点灵活选择,常常会将多种形式组合使用。

下面对封装堆叠进行介绍。

封装堆叠

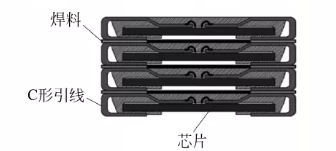

1.基于引线框架堆叠的 3D 封装技术

有一种 C 形引脚的引线框架,该结构中,上一层引线框架 C 形引脚(外引脚)的下表面与下一层引线框架 C 形引脚(外引脚)的上表面通过焊料进行焊接。2000 年,Soon-Jin Cho 等人提出了另一种基于 LOC 的双层堆叠封装。还有基于 LOC 的四重堆叠结构。这些引线框架的引脚长度和引脚弯曲角度都经过单独设计,在完成芯片键合和引线键合后,各引线框架按照各自的朝向进行堆叠,对应引脚之间采用焊料键合,随后进行整体塑封,之后按照常规的引线框架封装工艺完成后续的制作步骤。

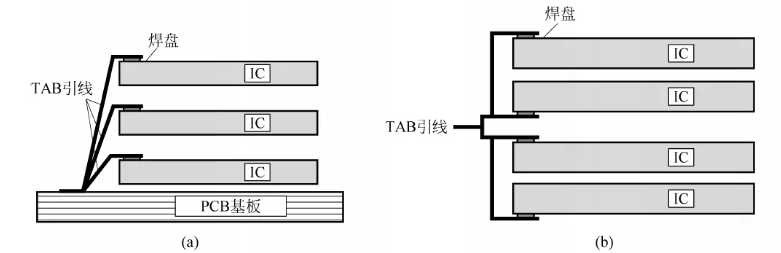

2.TAB 载带堆叠封装

TAB 堆叠 CSP 有两种互连方式:一种是通过热压将 TAB 与 PCB 实现键合;另一种是直接进行 TAB 引线之间的键合。由于堆叠的每个 TAB 需要不同的引脚形状,因此需要使用不同的模具进行切筋成型。单层 TAB 封装完成后厚度较薄,所以堆叠后的封装仍能保持较薄的外形。

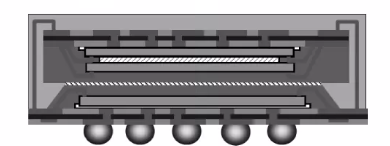

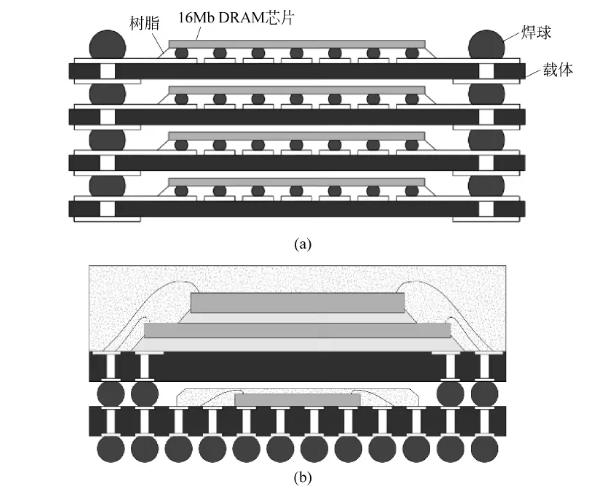

3.基于焊球互连的封装堆叠

基于焊球互连的封装堆叠(或称 BGA 堆叠)存在两种结构形式。在这种结构中,单个 BGA 封装内部可以采用倒装或焊线的连接方式,且单个封装中芯片所在的面与层间互连的焊球可以处于同一侧,也可以分别位于两侧。

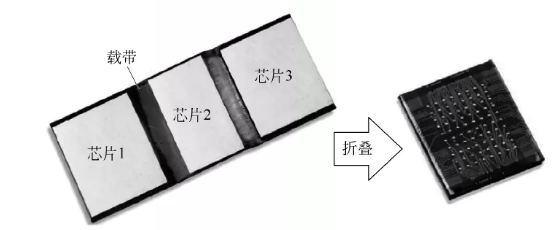

4.柔性载带折叠封装

柔性载带折叠封装通过折叠工艺,将平面装配转化为 3D 装配形式。采用芯片叠层方式处理不同尺寸的芯片叠层(如 ASIC 与 SRAM)时操作更便捷,而在处理相同或相近尺寸的芯片时,需额外添加一个较厚的中介层,以便为焊线预留足够空间,这会使成本有所增加。与芯片叠层方法相比,这种折叠方法对各类芯片的尺寸和高度都具有良好的适用性。

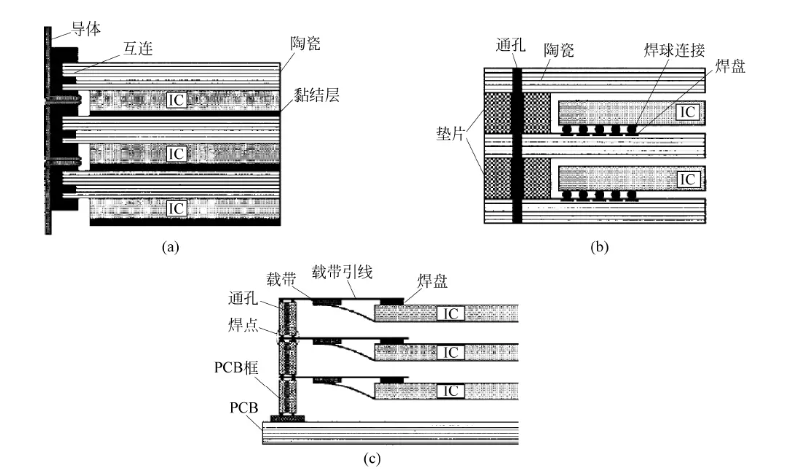

5.基于边缘连接器的堆叠

基于边缘连接器的堆叠技术更贴近 3D 组装技术,主要包含三种类型:①浸锡式垂直互连金属框;②封装基板与垫片通孔的填锡处理;③借助双面 PCB 框,通过焊料连接上下基板。

6.侧面图形互连堆叠

将多层封装进行堆叠后,在其侧面制作互连图案,从而实现不同层之间的互连,这一方式被称为侧面互连。该工艺能够实现更高密度的堆叠封装。

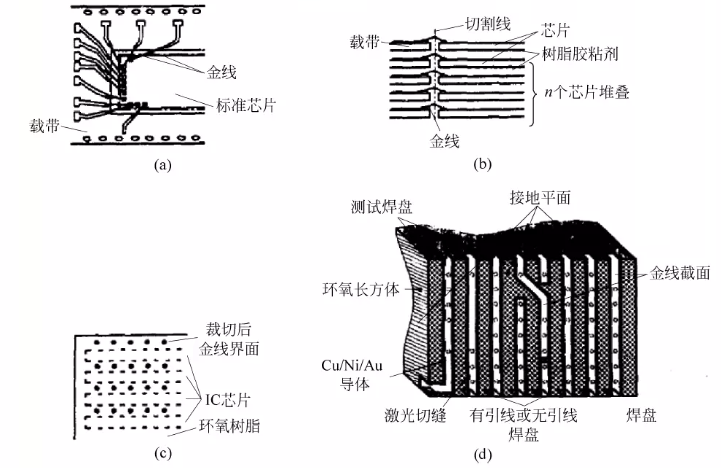

1990 年,Christia Val 与 Thierry Lemoine 提出了一种侧面 3D 互连的堆叠封装结构,其主要工艺流程如下:①在载带上完成芯片与载带的一级互连操作;②对单个集成电路进行测试与老化处理;③进行芯片堆叠并采用环氧树脂胶合;④裁切形成包含多个芯片的长方体;⑤在立方体侧面实现芯片间的二级互连,沉积 Cu/Ni/Au 薄膜后,用激光形成图形;⑥通过焊线或焊料连接方式,将长方体与封装基板 / 框架键合,制作成有引脚或无引脚的封装体。

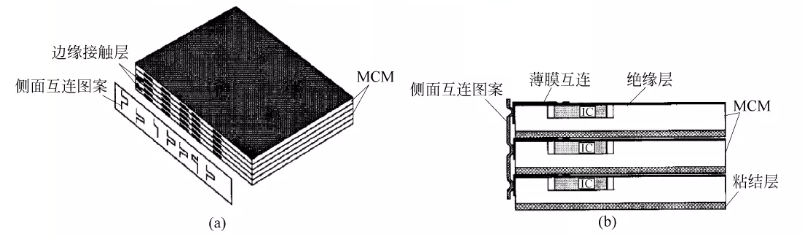

1994 年,GE 公司提出了一种侧面互连的高密度多芯片模组(MCM),其单层制作工艺与平面 MCM 工艺相近,独特之处在于将金属图形化工艺延伸至侧面,具体包括溅射种金层、借助电泳保形涂覆阻挡层、利用 45° 镜面反射激光同时对表面和侧面的阻挡层进行图形化处理、通过电镀工艺增厚互连金属等步骤;之后将单层层叠黏结,进一步在侧面层压硅聚酰亚胺(SPI),并进行侧面开孔与互连制作。

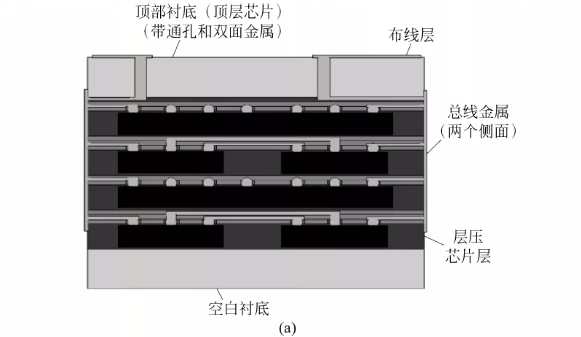

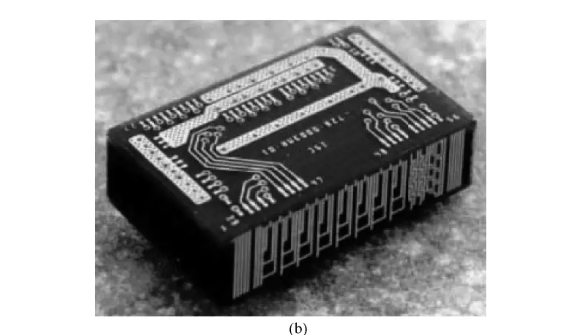

1998 年,IRVINE SENSORS 公司的 Keith D.Gann 等人提出了一种 NEO 堆叠技术,该技术可将不同尺寸或多个芯片的焊盘连接转移至侧边的晶圆级 NEO 层,能够在 50 层 NEO 层中,将 200 个大型闪存芯片堆叠在 0.75 英寸 ×1.2 英寸的面积上,高度仅为 0.5 英寸。通过两个较长的侧面总线实现了高水平的互连。

1999 年,IBM 公司也提出了一种侧面互连的 3D 叠层存储器件。该器件的片间层由三层 PI 层和一层再布线层构成,再布线层可同时实现将层内通孔转移至侧面通孔,进而在侧面进行再布线和焊球制作,以实现对外连接。

-

封装技术

+关注

关注

12文章

582浏览量

68708 -

3D封装

+关注

关注

9文章

144浏览量

27916

原文标题:3D封装技术

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

3D集成电路的结构和优势

3D封装的优势、结构类型与特点

3D封装的优势、结构类型与特点

评论