电子发烧友网报道(文 / 吴子鹏)日前,PCI-SIG 正式公布 PCI Express 8.0(PCIe 8.0)规范的开发计划,目标在 2028 年向会员发布。根据公布的规范,PCIe 8.0 将使速率在 PCIe 7.0 的基础上翻倍至 256.0 GT/s,通过 x16 配置实现 1TB/s 的双向带宽。

从 PCI-SIG 目前公布的细节来看,PCIe 8.0 首先实现了速度的提升,新的标准会开发协议增强功能以提高带宽。不过速度提升之后会带来一系列技术挑战,比如信号完整性与抗干扰能力方面的问题。随着速率从 PCIe 7.0 的 128 GT/s 翻倍至 256 GT/s,信号在铜缆或 PCB 中传输时的衰减、串扰(相邻信号线的电磁干扰)、抖动(信号 timing 偏差)会进一步恶化。同时,外部电磁干扰(EMI)也会加剧,这就要求连接器、线缆和 PCB 设计具备更强的抗干扰能力。另外,连接器的插入损耗、回波损耗(信号反射)会随频率升高而恶化,因此需要重新设计接触件结构并采用低损耗材料。为此,PCI-SIG 在 PCIe 8.0 规范目标中提到要评估新型连接器技术。

高速率传输还需要 PCIe 8.0 平衡延迟与 FEC 之间的矛盾。在高速传输过程中,信号错误率会随速率提升而上升,这必须依赖前向纠错(FEC)技术来修正错误。但 FEC 需要额外的计算和数据冗余(如增加校验位),不可避免地会增加延迟。所以,挑战在于设计 “轻量级 FEC 算法”,在保证纠错能力的同时,最小化计算开销和冗余数据量,从而平衡可靠性与低延迟。基于此,PCI-SIG 会确认相关技术可满足延迟和前向纠错(FEC)目标。

PCIe 的核心优势之一是向后兼容,然而在高速率下,兼容设计的难度大幅增加。例如,物理层需支持多速率自适应,这就要求电路同时兼容不同信号特性,进而增加了均衡器、时钟恢复电路的设计复杂度;协议层需兼容前代的流量控制、事务处理机制,同时引入新的增强功能(如更高效率的带宽利用),这需要避免新功能与旧协议冲突而导致逻辑设计冗余。不过,PCI-SIG 的目标是保持 PCIe 8.0 与历代 PCIe 技术的向后兼容。

PCIe 8.0 还必须考虑散热方面的影响,功耗上升会直接导致芯片(如 PCIe 控制器、交换机)和链路组件(连接器、线缆)的发热量增加,而高温会进一步恶化信号完整性并缩短器件寿命。在芯片级,需要集成更高效的热管理模块;在系统级,需优化散热方案(如液冷、高密度散热鳍片),尤其在超大规模数据中心等密集部署场景中,散热成本可能会显著上升。为此,PCI-SIG 也会确保达成可靠性指标。

综上,PCIe 8.0 的速度跃升本质上是对信号物理特性、功耗控制、兼容性设计的全面挑战,需要从材料、电路、协议、测试等多维度突破现有技术瓶颈,才能实现高带宽、低延迟、高可靠的目标。

PCIe 8.0规范发布之后,有望为人工智能 / 机器学习、高速网络、边缘计算和量子计算等新兴应用提供可扩展的互连解决方案;并将支持汽车、超大规模数据中心、高性能计算(HPC)以及军事 / 航空航天等数据密集型市场。

发布评论请先 登录

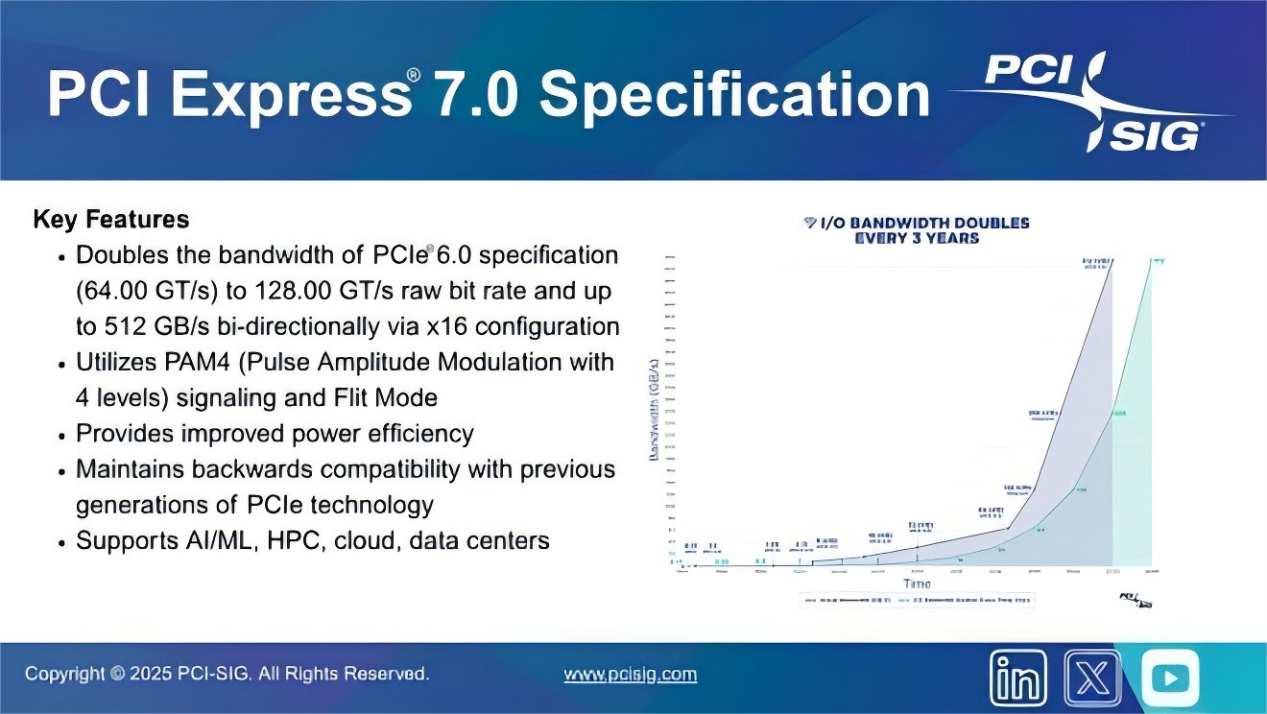

PCIe 7.0发布:16通道双向512GB/s,拥抱光纤未来

PCIe协议分析仪在数据中心中有何作用?

PCIe 7.0最终版草案发布,传输速率128 GT/s,PCIe 6.0加速商业化

在RC测试中执行pcitest-S-r-s 1024后ep系统崩溃了怎么解决?

美光推出速率与能效领先的 60TB SSD

PCIe 4.0与3.0的区别 PCIe设备的故障排除方法

pcie接口类型及其应用

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性

PCIe 8.0 规范公布:1TB/s 带宽、256GT/s 速率

PCIe 8.0 规范公布:1TB/s 带宽、256GT/s 速率

评论