在任意设计流程中,仿真都是不可或缺的关键组成部分。它允许用户在无任何物理硬件的情况下对硬件系统进行确认。这篇简短的博客将介绍如何使用 QEMU + 协同仿真来对 AMD Versal 自适应 SoC Cortex A72 (QEMU) 上运行的固件进行仿真,该固件会访问当前 AMD Vivado Design Suite 仿真中正在进行仿真的 PL 中的 IP。本文将使用 Versal VCK190 和 Vivado 2024.2 来生成仿真环境。

注释:目前这是实验性流程,尚未受到正式的支持。

QEMU 设备树二进制对象

QEMU 使用模型来对 Versal CIPS 进行仿真。每块 AMD 开发板都有预构建的设备树二进制对象 (DTB)。在本博客中使用的是 VCK190 的 DTB。在本系列后续博文中,将介绍用户如何自行编译 DTB,从而与用户自定义系统保持更紧密的一致。目前,该演示的 DTB 文件已随本篇博文一同交付。

硬件设计

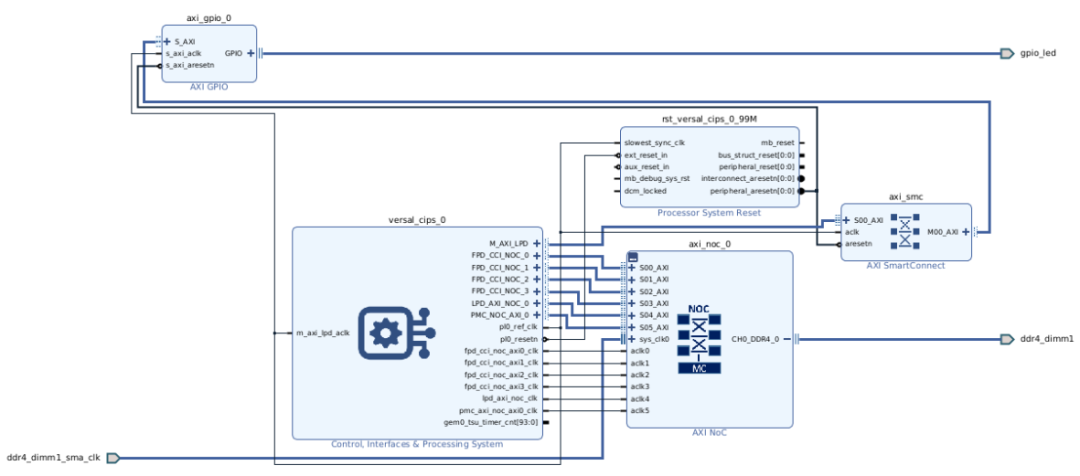

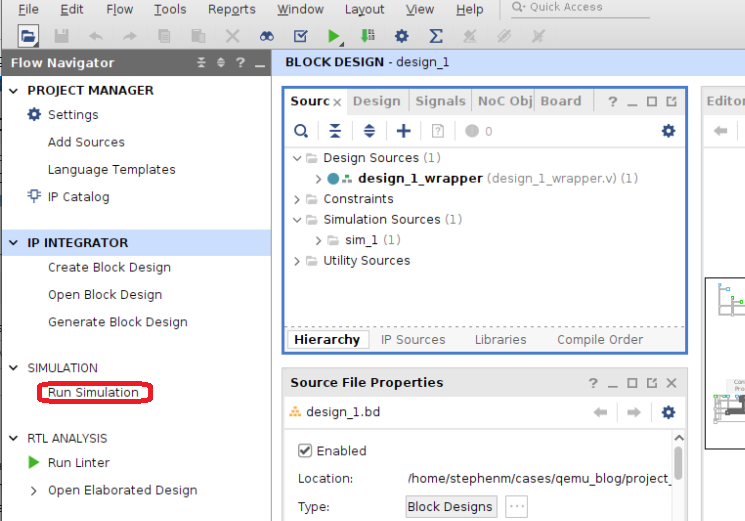

使用 Vivado 2024.2 来生成简单的块设计,如下所示:

设置仿真脚本

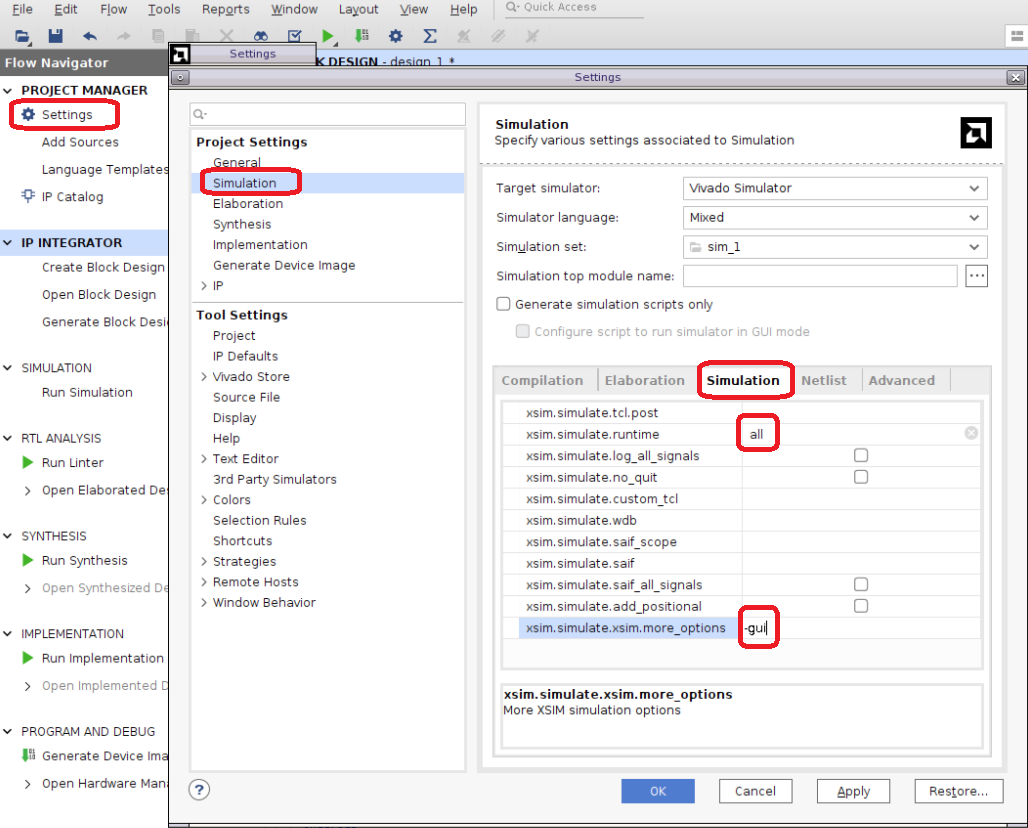

此处使用的是由 Vivado 生成的仿真脚本,但要对这些脚本稍作修改:

希望仿真永久保持运行 (all)

希望运行脚本时启动 GUI (-gui)

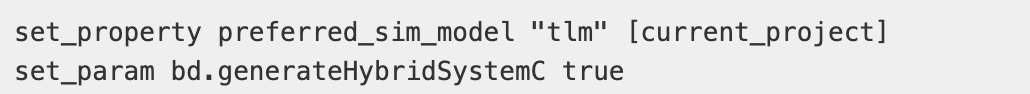

需要指定仿真要使用的仿真模型。在此例中,要使用的模型是 TLM。

为此,只需在 BD 上运行以下 Tcl 命令:

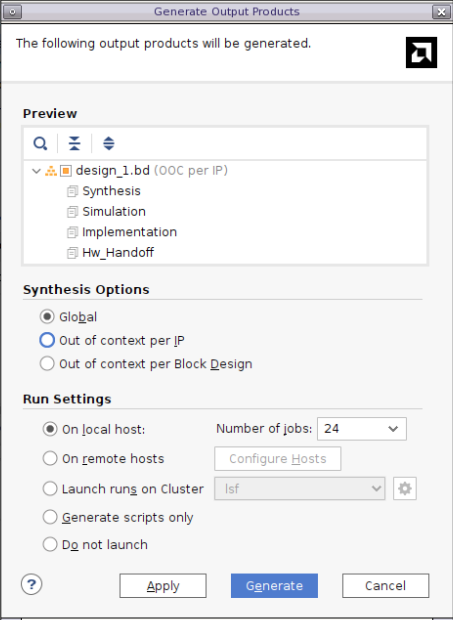

下一步,生成输出文件,将其设为 Global。

生成仿真脚本

生成顶层 RTL 封装文件,然后运行仿真。这样会生成仿真脚本,稍后在 QEMU + 协同仿真脚本中将启动这些仿真脚本。

这样会在 project_1.simsim_1ehavxsim 中生成仿真脚本以供后续调用。

开发者只需使用 Tcl 命令完成这些操作即可,但希望在本篇博文中通过 GUI 演示。

导出硬件以生成 XSA 文件。此文件将在 AMD Vitis 统一软件平台中用于生成工作空间,以供在本系列后续博文中使用。

生成 QEMU

此处将使用以下 QEMU 实参。将 QEMU 实参置于 Linux 脚本中。例如,分别使用 run_qemu_aarch64.sh 和 run_qemu_microblazeel.sh。

Aarch64 QEMU 实参

echo 'INFO: Starting aarch64 QEMU'echo 'INFO: TCP PORT is free 9000'echo 'INFO: qemu-system-aarch64 -nographic -M arm-generic-fdt -serial null -serial null -serial mon:stdio -serial null -display none -boot mode=5 -drive if=sd,index=1,file=qemu_sd.img,format=raw -machine-path /tmp/tmp_dir -sync-quantum 1000000 -hw-dtb board-versal-ps-cosim-vitis-vck190.dtb -m 8G -display none -gdb tcp::9000 -net nic,netdev=eth0 -netdev user,id=eth0,tftp=/tftpboot -net nic'qemu-system-aarch64 -nographic -M arm-generic-fdt -serial null -serial null -serial mon:stdio -serial null -display none -boot mode=5 -drive if=sd,index=1,file=qemu_sd.img,format=raw -machine-path /tmp/tmp_dir -sync-quantum 1000000 -hw-dtb board-versal-ps-cosim-vitis-vck190.dtb -m 8G -display none -gdb tcp::9000 -net nic,netdev=eth0 -netdev user,id=eth0,tftp=/tftpboot -net nic

Microblazeel QEMU 实参

echo 'INFO: Starting microblaze QEMU'echo 'INFO: qemu-system-microblazeel -M microblaze-fdt -serial mon:stdio -display none -device loader,addr=0xf0000000,data=0xba020004,data-len=4 -device loader,addr=0xf0000004,data=0xb800fffc,data-len=4 -device loader,file=pmc_cdo.0.0.bin,addr=0xf2000000 -device loader,file=BOOT_bh.bin,addr=0xf201e000,force-raw=on -device loader,file=plm.elf -hw-dtb board-versal-pmc-virt.dtb -machine-path /tmp/tmp_dir -device loader,addr=0xF1110624,data=0x0,data-len=4 -device loader,addr=0xF1110620,data=0x1,data-len=4'qemu-system-microblazeel -M microblaze-fdt -serial mon:stdio -display none -device loader,addr=0xf0000000,data=0xba020004,data-len=4 -device loader,addr=0xf0000004,data=0xb800fffc,data-len=4 -device loader,file=pmc_cdo.0.0.bin,addr=0xf2000000 -device loader,file=BOOT_bh.bin,addr=0xf201e000,force-raw=on -device loader,file=plm.elf -hw-dtb board-versal-pmc-virt.dtb -machine-path /tmp/tmp_dir -device loader,addr=0xF1110624,data=0x0,data-len=4 -device loader,addr=0xF1110620,data=0x1,data-len=4

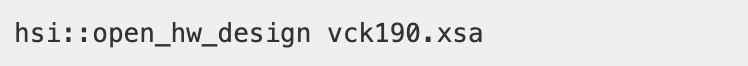

此时需要一些文件。可以使用 HSI 从 Vivado 导出的 XSA 中提取 PLM 文件:

这样会提取 PDI 以及一个解压后的文件夹,其中包含以上使用的 plm.elf 文件。

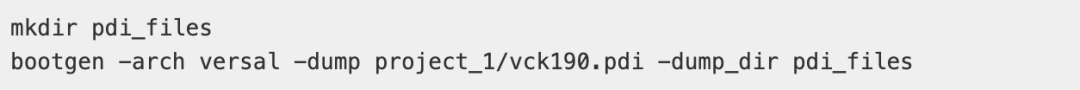

使用以下命令从 PDI 解压 pmc_cdo.0.0.bin 文件:

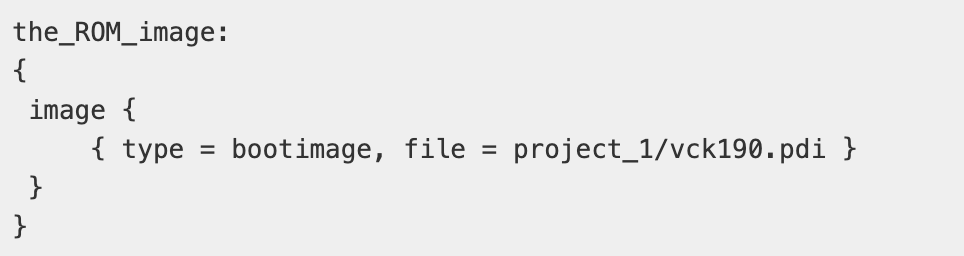

QEMU 目前不支持从 JTAG 启动。在本博客中,将从 SD 启动。因此,需要生成 SD 卡启动镜像与启动头文件。要生成 qemu_sd.img 和 BOOT_bh.bin,首先需要生成包含 PDI 的 BOOT.BIN。

为此,可以生成如下 BIF 文件:

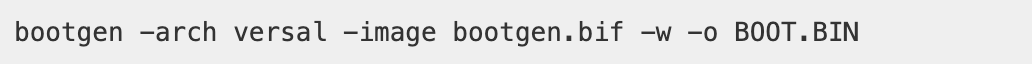

然后,只需在此文件上运行 Bootgen 以生成 BOOT.BIN 即可:

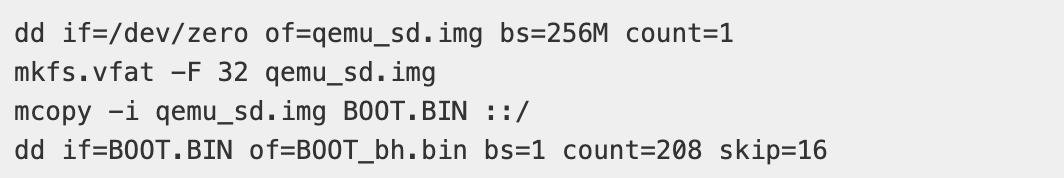

下一步,创建 QEMU 镜像文件 (qemu_sd.img) 并将 BOOT.BIN 添加到此镜像中。最后,生成启动头文件 (BOOT_bh.bin)。

启动 QEMU + 协同仿真

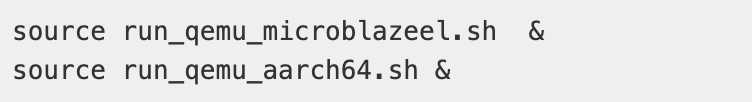

生成 Linux 脚本以调用上述 QEMU Multi Proc 实参。例如:

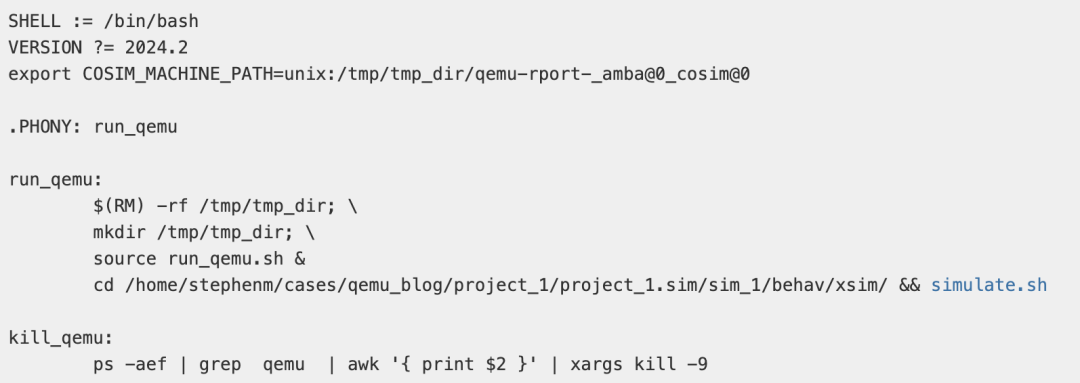

使用 Makefile 启动 QEMU + 协同仿真。使用 tmp 目录充当 TLM 的共享目录。需使用环境变量 COSIM_MACHINE_PATH 将此目录传递给 Vivado 仿真器。

注释:xsim 路径将根据您的工程而定。

文件夹结构如下,为便于使用,已将所有文件置于单个文件夹内。

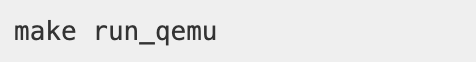

要启动 QEMU + 协同仿真,运行以下命令:

可以看到,一切都按期望方式启动。

要终止 QEMU,请运行以下命令:

后续内容

在下一篇“开发者分享”中,我们将介绍如何在 Vitis 中连接到该 QEMU + 协同仿真,并构建和部署用户应用。

-

amd

+关注

关注

25文章

5603浏览量

136776 -

soc

+关注

关注

38文章

4414浏览量

223590 -

仿真

+关注

关注

52文章

4315浏览量

136238 -

开发板

+关注

关注

25文章

5765浏览量

106303

原文标题:开发者分享|在 AMD Versal? 自适应 SoC 上使用简单的 QEMU + 协同仿真示例

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何在AMD Vitis Unified 2024.2中连接到QEMU

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之 Versal 介绍(2)

Versal? 自适应 SoC 助力 8K 处理 – 为 8K 做好准备(3)

AMD率先推出符合DisplayPort? 2.1 8K视频标准的FPGA和自适应SoC

AMD发布第二代Versal自适应SoC,AI嵌入式领域再提速

AMD Versal? Adaptive SoC CPM PCIE PIO EP设计CED示例

第二代AMD Versal Prime系列自适应SoC的亮点

AMD Versal自适应SoC CPM5 QDMA的Tandem PCIe启动流程介绍

AMD Versal自适应SoC GTM如何用XSIM仿真和观察PAM4信号

AMD Versal自适应SoC器件Advanced Flow概览(上)

AMD Versal自适应SoC器件Advanced Flow概览(下)

在AMD Versal自适应SoC上使用QEMU+协同仿真示例

在AMD Versal自适应SoC上使用QEMU+协同仿真示例

评论