在半导体封装技术向微型化、高集成度加速演进的浪潮中,瑞沃微CSP封装凭借其极致小型化、高集成度和性能优越性,在消费电子、汽车电子等领域展现出显著优势。然而,从成本、量产、质量体系等多维度审视,其仍存在一定劣势。

成本维度:材料与设备投入制约经济性

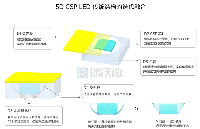

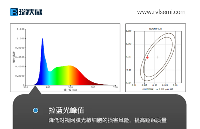

瑞沃微CSP封装采用裸芯片直接散热结构,剥离引线框架与塑封材料,虽降低热阻至4.2℃/W,但需依赖高导热性基板材料,如低CTE(热膨胀系数)基板,其成本较传统材料高出30%以上。此外,为满足高频信号完整性需求,CSP封装需采用化学I/O键合技术重构引脚布局,该工艺需引入高精度光刻设备与原子层沉积(ALD)设备,单台设备投入超千万元,显著推高初期研发成本。在高端照明领域,尽管CSP封装通过反射碗杯结构提升光效10%-15%,但荧光膜技术与精密光学设计导致单颗封装成本较传统SMD LED高出40%,限制了其在中低端市场的普及。

量产维度:工艺精度与供应链瓶颈并存

瑞沃微CSP封装倒装焊二次布线需突破200μm精度,引线键合需控制0.5mm以下超短弧线,对设备稳定性与操作人员技能要求极高。以5G基站芯片量产为例,其5D模块化设计支持单芯片I/O密度突破5000个/mm?,但超细线宽RDL(再分布层)技术良率仅维持在92%-93%,较传统BGA封装低5-8个百分点。供应链层面,高密度基板(如BT树脂基板)国产化率不足30%,核心材料依赖进口,导致交货周期延长至12周以上,难以满足客户紧急订单需求。此外,球窝缺陷(Pillow-head Effect)在无铅制程中频发,需通过优化回流工艺(如延长均热区时间)降低风险,但此举会延长生产周期15%-20%。

质量体系维度:可靠性验证与标准缺失挑战

瑞沃微CSP封装虽通过AEC-Q102认证,但在汽车电子领域,其15年设计寿命要求需经历-40℃至125℃极端温度循环测试,而多层芯片堆叠结构在热应力作用下易出现界面分层,导致抗剪切强度从35MPa衰减至28MPa,影响长期可靠性。在高频通信场景中,CSP封装寄生电感虽低至0.2nH,但毫米波雷达测试显示,其信号传输延迟仍较理想值高出1-2ns,需通过优化TSV(硅通孔)技术进一步改善。此外,行业缺乏统一的CSP封装尺寸与电参数标准,设计复用率不足40%,导致客户需针对不同应用场景定制化开发,增加验证成本与周期。

-

半导体封装

+关注

关注

4文章

296浏览量

14538 -

CSP封装

+关注

关注

0文章

23浏览量

11734

发布评论请先 登录

封装业“成本分水岭”——瑞沃微CSP如何让传统、陶瓷封装渐成 “前朝遗老”?

瑞沃微先进封装:突破摩尔定律枷锁,助力半导体新飞跃

纳芯微发布新一代CSP封装MOSFET NPM12017A系列

解锁照明新境界,瑞沃微 CSP1111 以卓越性能引领未来

CSP1111-3D-2828-规格书

多维度焊接质量监测仪:精准检测,保障安全

2025年电子元器件市场展望:瑞沃微深度剖析机遇与挑战的前瞻预测

瑞沃微:一文详解CSP(Chip Scale Package)芯片级封装工艺

从成本、量产、质量体系等多维度看瑞沃微CSP封装的劣势对比

从成本、量产、质量体系等多维度看瑞沃微CSP封装的劣势对比

评论