来源:FPGA技术实战

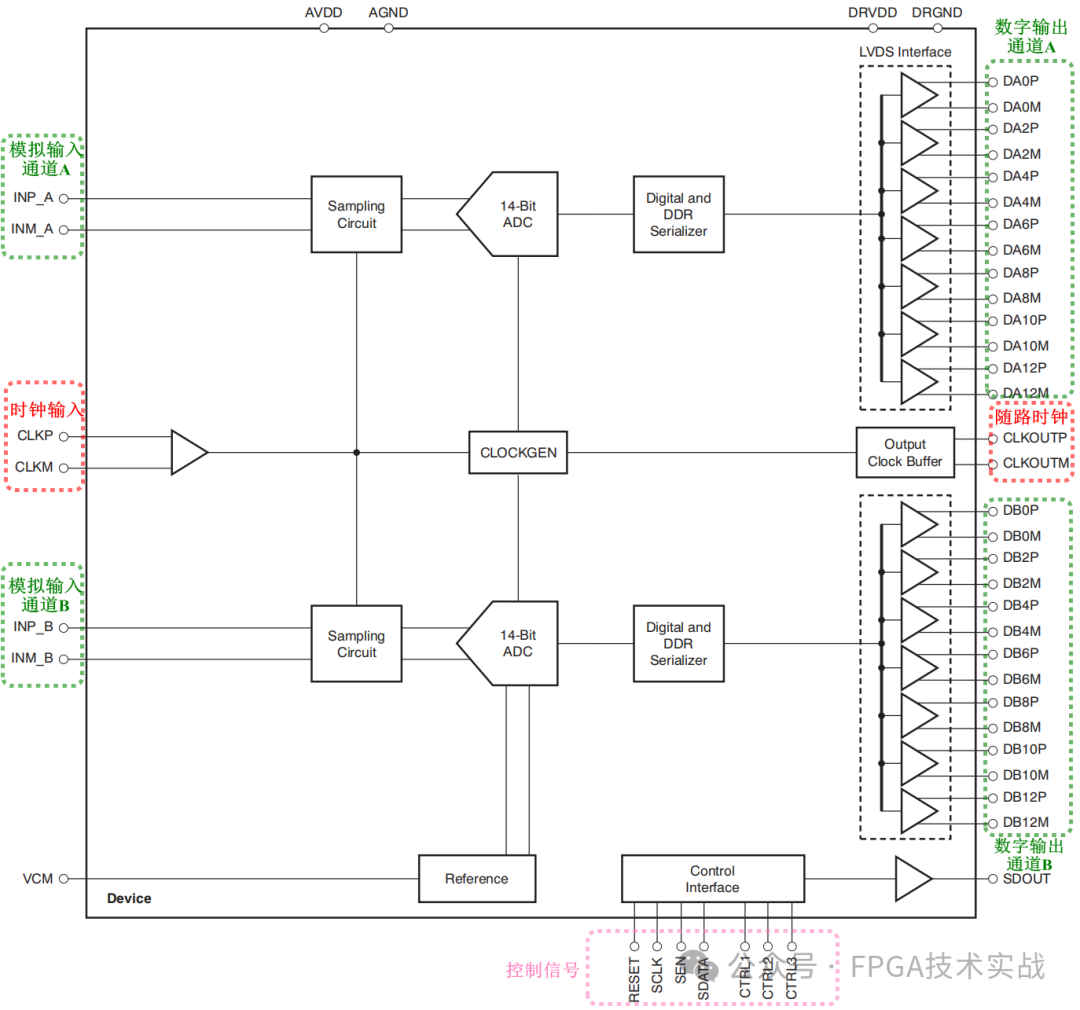

引言:本文描述了ADC和FPGA之间LVDS接口设计需要考虑的因素,包括LVDS数据标准、LVDS接口数据时序违例解决方法以及硬件设计要点。

1. LVDS简介

1.1 什么是LVDS?

LVDS(低压差分信号)标准是业界流行的差分数据传输标准,它是双线、低摆幅差分信号。其优点包括以下几点:

?低电源电压运行

?高速数据传输

?良好的共模噪声抑制

?噪音产生更少

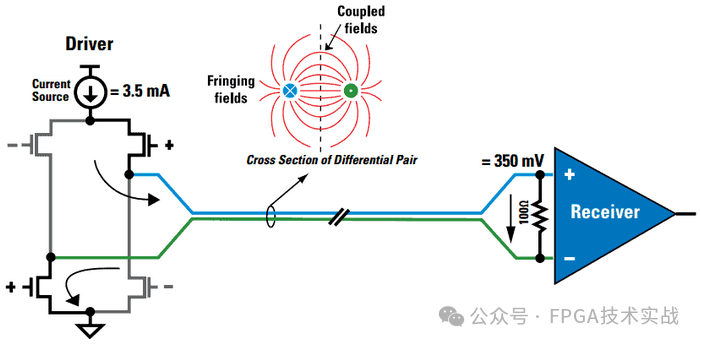

图1:LVDS发送器和接收器

LVDS是在100Ω的受控阻抗介质上进行基带数据传输,其中传输介质可以是PCB走线、背板或电缆。如图1所示,LVDS输出由约3.5mA的电流源组成,该电流源驱动差分对。LVDS接收器具有高直流输入阻抗,因此,LVDS驱动器的大部分电流流过100Ω的终端电阻器,在接收器输入端产生约350mV的电压。

1.2 LVDS标准

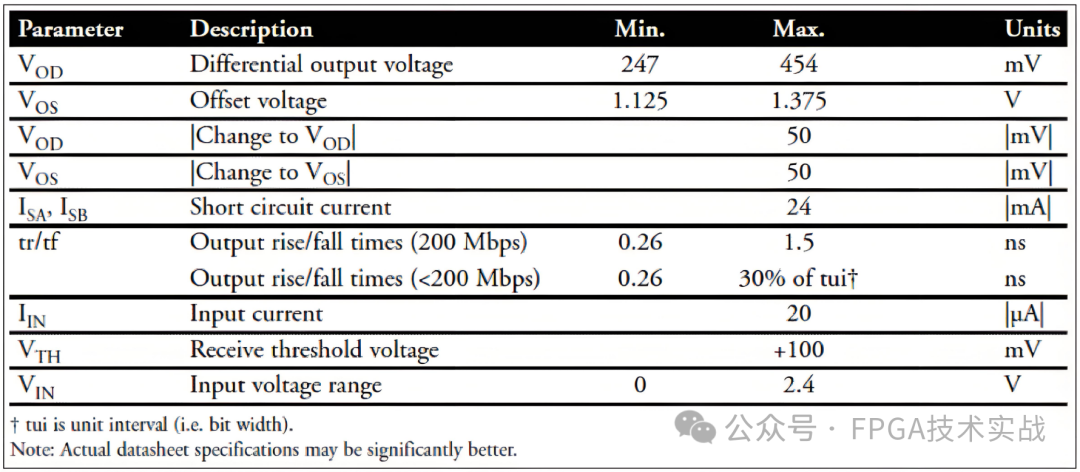

表1所示的ANSI/TIA/EIA-644-A(LVDS)标准定义了LVDS信号。本标准定义了驱动器输出和接收器输入特性,它是一个纯电气标准。它不包括基本规范、协议甚至完整的电缆特性,因为这些都取决于应用。这允许在许多应用中轻松采用,也允许参考标准根据所需的信号质量和媒体长度或类型指定所需的最大数据速率。

表1:ANSI/TIA/EIA-644(LVDS)标准

1.3 LVDS优于单端标准的优势

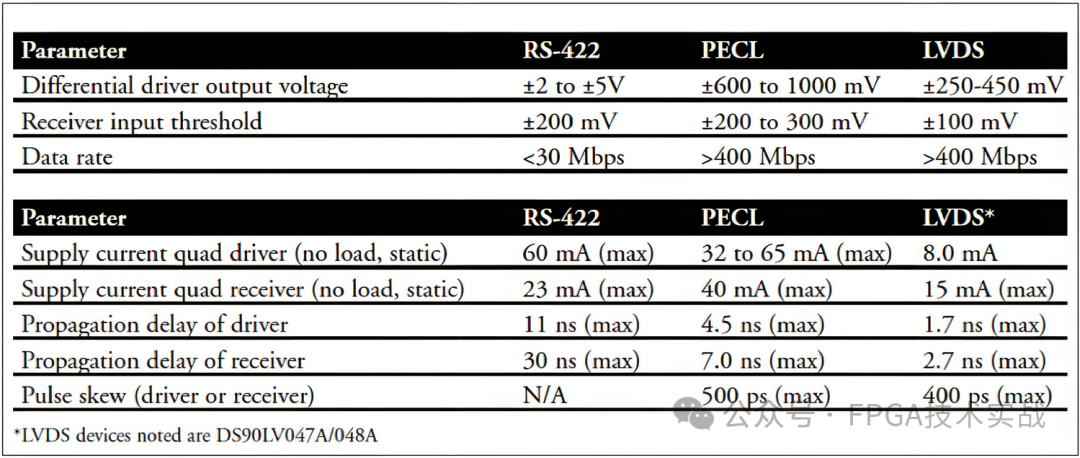

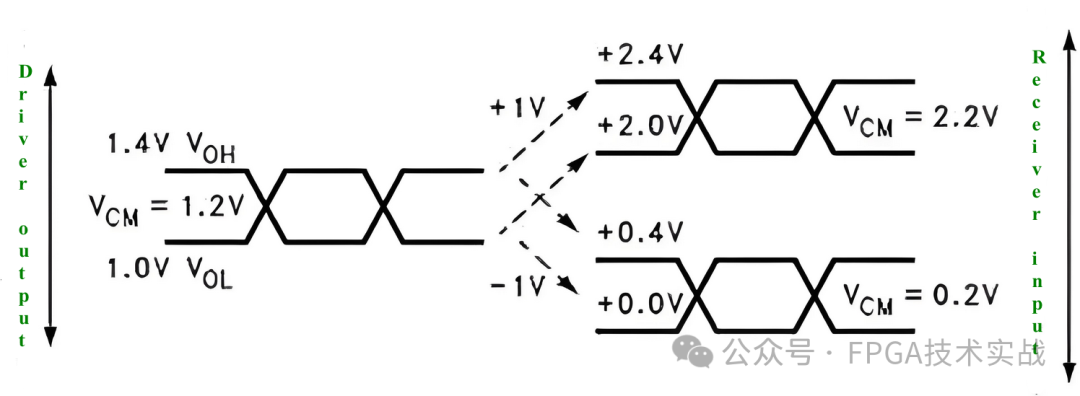

LVDS中使用的差分数据传输方法比CMOS等单端方案更不容易受到共模噪声的影响。因为差分传输使用两条具有相反电流和电压摆动的线来传输数据,而不是CMOS中使用的一条线。LVDS接收器只会查看两个信号之间的差异,可以消除共模噪声。另外,由于磁场的抵消,差分信号也倾向于比单端信号辐射更少的噪声。此外,电流模式驱动器不易产生振铃和开关尖峰,进一步降低了噪声。LVDS与其他信号标准的比较如表2所示。

表2:LVDS与其他信号标准的比较

ANSI/TIA/EIA标准基于一组限制性假设建议最大数据速率为655Mbps,并基于无损耗介质提供了1.923Gbps的理论最大值。数据传输的最终速率和距离取决于介质的衰减特性和来自环境的噪声耦合。

图2:共模电压范围

2. ADC LVDS数据的边沿捕获分析

当LVDS接收器中没有足够的建立和保持时间来捕获数据时,称为边边沿获。由于LVDS对之间的PCB走线长度不匹配,可能会发生数据的边沿捕获。例如,如果6个DDR LVDS对没有以相同的距离路由到FPGA,则边沿捕获发生在12位ADC中。在边沿捕获期间,一些数据位可能会改变其值,导致FPGA不能正确采样ADC数据。

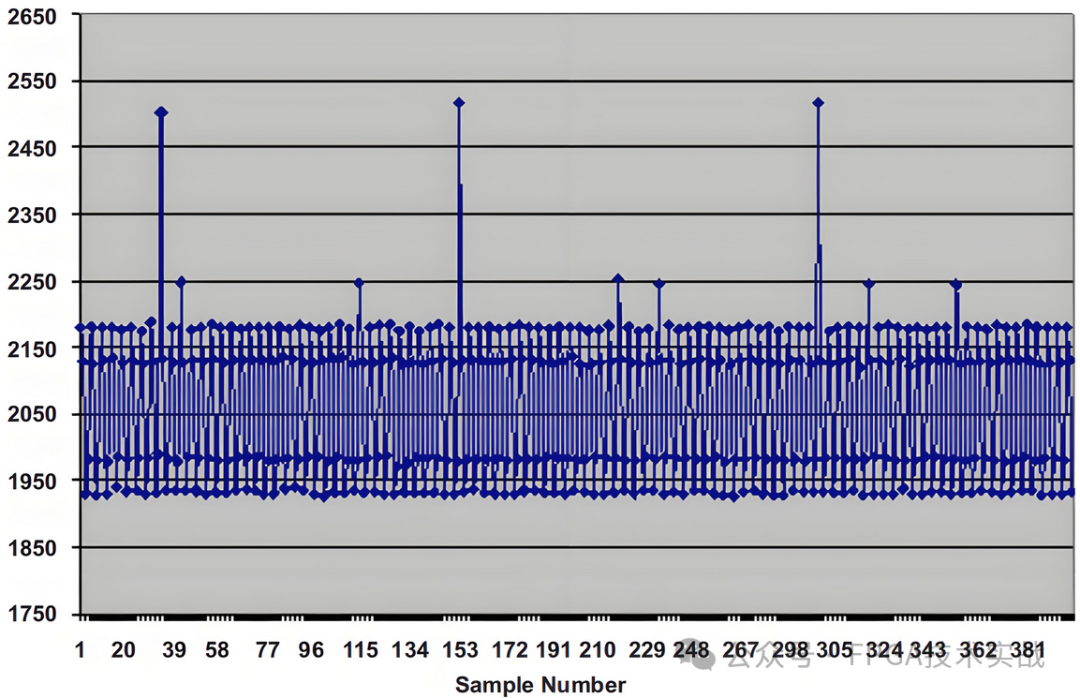

图3:显示了从ADS6129 12位ADC在FPGA内捕获的边沿捕获数据

由于ADC数据的边缘捕获,在图3中观察到峰值。在这种情况下,对比特D6和D8观察到边沿捕获。峰值是由于D6和D8位的建立和保持时间违规造成的。x轴表示采样数,y轴表示12位ADC的信号幅度。

3. 处理边沿捕获问题

边沿捕获问题可以通过两种方法来解决。一种方法是使用ADC LVDS功能来改变LVDS数据线相对于LVDS输出时钟的延迟。另一种方法是使用FPGA内部的延迟组件。

3.1 使用ADC内部的延迟特性

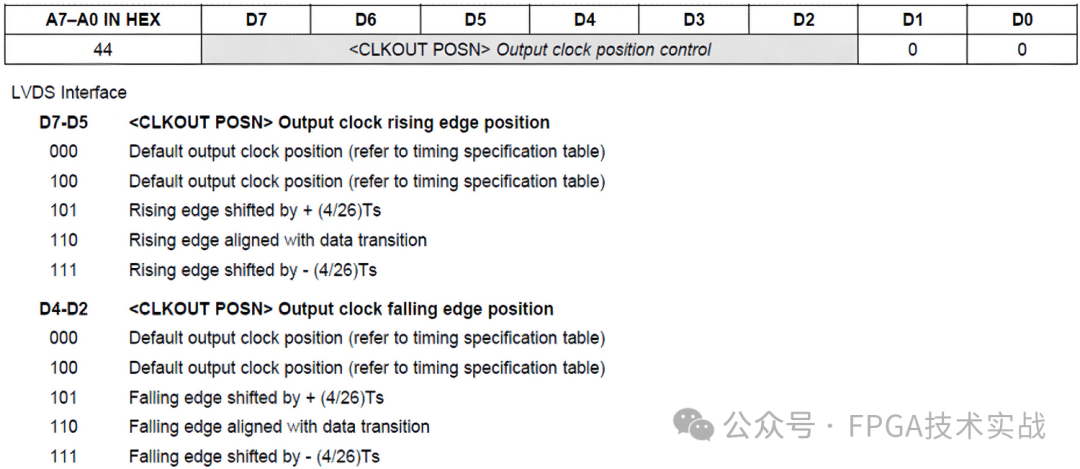

通过使用ADC的串行接口或并行模式调整输出时钟边沿,ADC LVDS数据可以相对于时钟延迟。只有调整输出时钟边沿才有可能改变所有LVDS对相对于输出时钟的建立和保持关系。图4提供了ADS6129串行模式下时钟位置偏移功能的详细信息。

图4:串行模式下ADS6129的时钟位置偏移特性

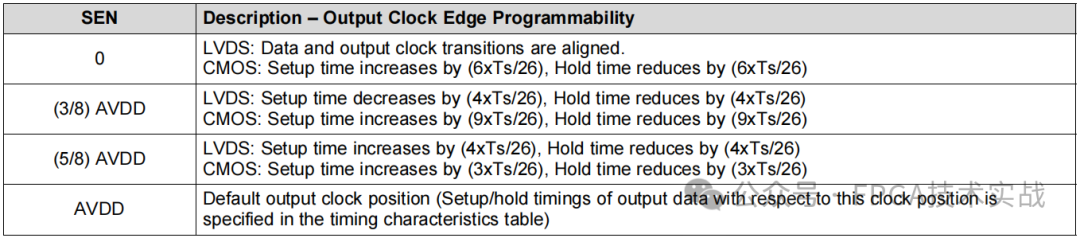

另外,ADS6129为并行模式控制时,可以通过控制SEN引脚电压来控制时钟延迟,如表3所示。

表3:SEN–模拟控制引脚

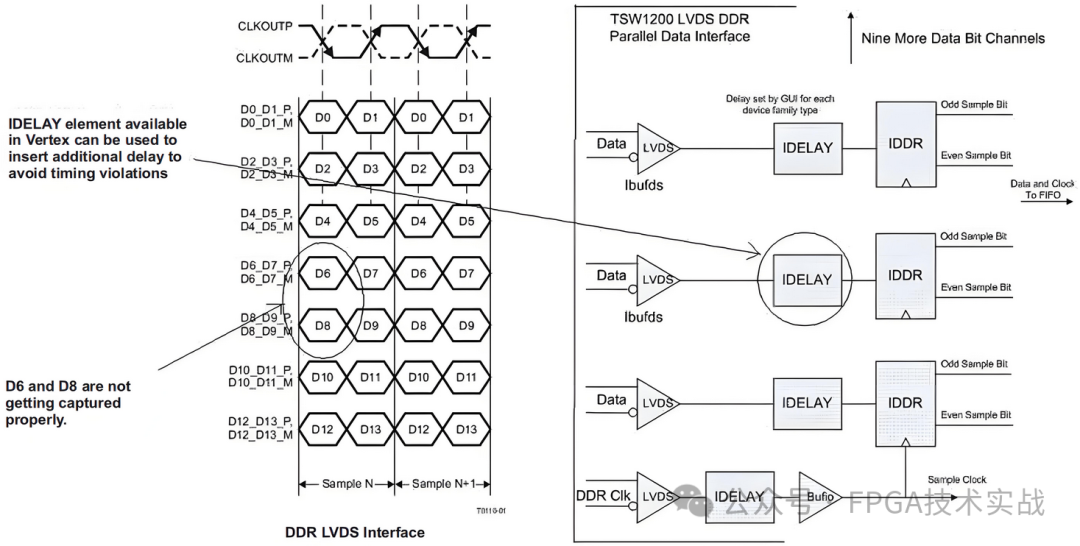

3.2 使用FPGA内部的延迟特性

解决边沿捕获问题的另一种方法是利用FPGA内部的延迟特性。FPGA的每个LVDS对都有延迟组件。例如,Xilinx FPGA具有称为“IDELAY”的延迟元件,可用于更改每个LVDS对的单独延迟。FPGA的IDELAY非常灵活,可以插入任何LVDS ADC对和FPGA之间。对于图2所示的边沿捕获问题,LVDS对D6_D7和D8_D9需要使用IDELAY组件进行延迟。此外,LVDS数据对之间的偏斜也可以通过在FPGA内使用此IDELAY组件来补偿。

图5:FPGA延迟块与ADC LVDS数据

4. 使用ADC测试模式功能检查ADC和FPGA LVDS数据时序

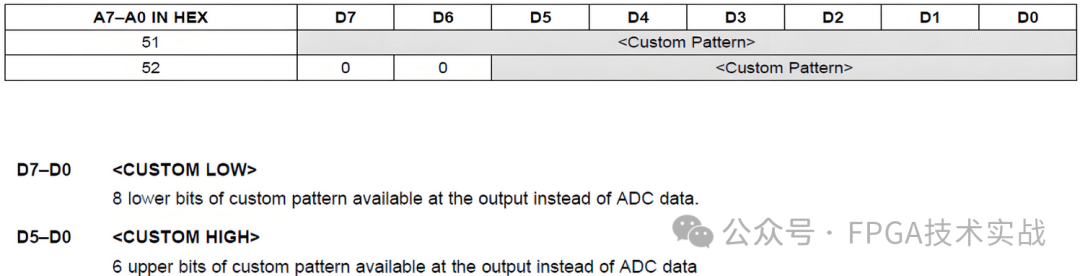

为了验证建立和保持时间,系统设计人员可以使用测试模式生成可以在FPGA内部验证的特定模式。在测试模式下,可以使用用户自定义模式对每个上升沿和下降沿的位翻转进行编程。这是用FPGA测试ADC LVDS数据接口健康状况的最佳方法。图6提供了ADS6129和ADS6149的这种测试模式特征的信息。

图6:ADC内部的自定义测试模式选项

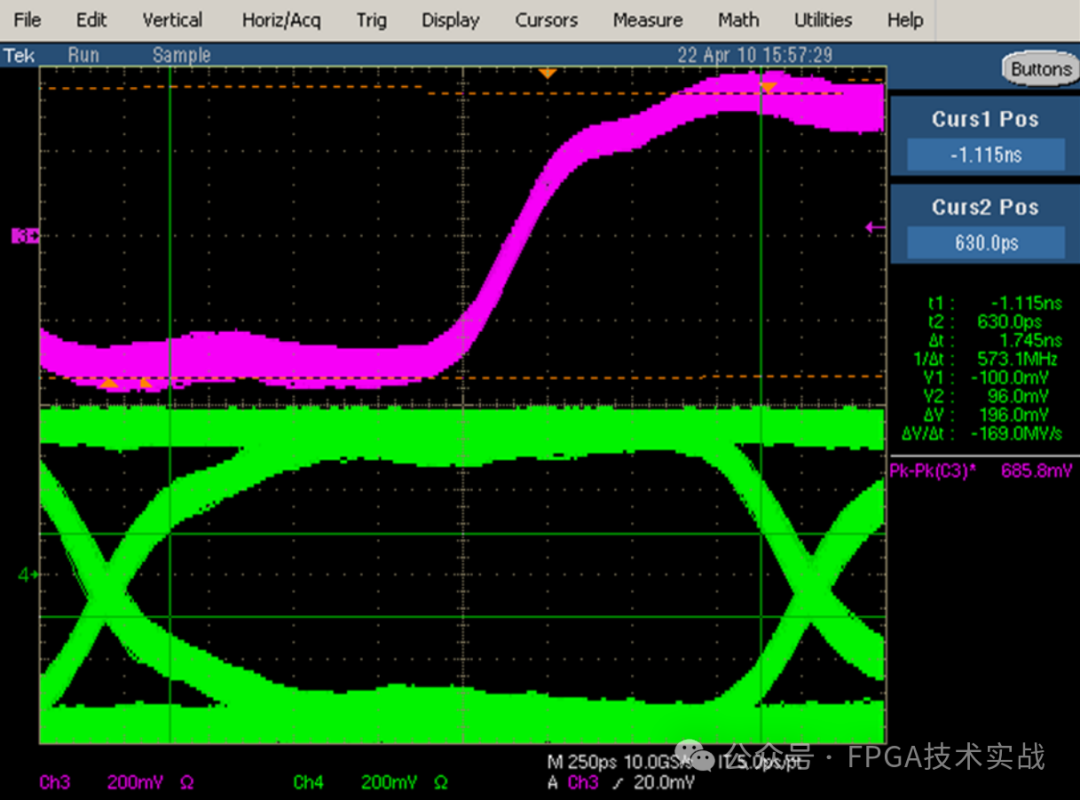

该测试确定了ADC和FPGA之间的正确接口。如果测试模式通过,则可以认为ADC LVDS与FPGA的数据接口是正确的。图7显示了10 MHz NORMAL模拟输入信号的数字化数据眼图。

图6:10MHz正常输入模拟信号的数字化数据眼图

5. ADC与FPGA之间LVDS信号布线设计考虑

(1)如果ADC输出和FPGA输入引脚之间的布线距离较大,则必须注意将差分阻抗保持在100Ω附近。差分对的总长度并不重要,但在指定内差分对之间的匹配很重要。此匹配规范取决于ADC采样率以及设置和保持时间裕度。

(2)在ADC LVDS输出和FPGA输入之间的任何跨分割处,差分特性阻抗应在90Ω至110Ω之间,由于LVDS信号的边缘速率很快,阻抗匹配非常重要。

(3)最好在PCB中使用至少4层。高速设计需要接地、电源和单端信号(如CMOS)以及LVDS信号的单独层。

图7:典型4层PCB层叠

(4)LVDS线路的最小PCB通孔数量。最好使用45度转弯,避免90度转弯。

(5)LVDS信号在没有终端电阻器的情况下无法工作。最好的选择是使用FPGA的内部100Ω终端电阻器(如果可用)。对于内部FPGA终端电阻器,输入LVDS终端寄存器需要在FPGA粘合逻辑中设置为“TRUE”。

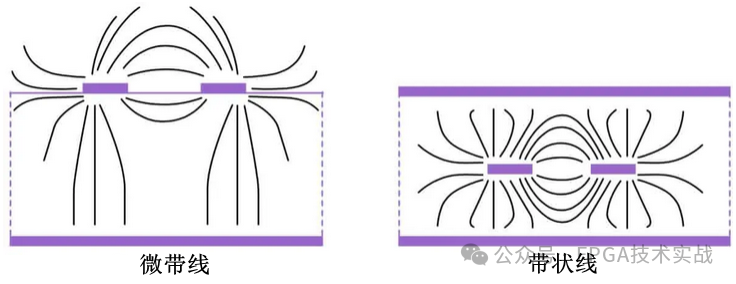

(6)在顶层上布线高速走线可以避免通孔以及通孔引起的电感。然而,在中间层上布线高速走线有助于更好地抑制噪声。在带状线(中间层)而不是微带线(顶部/底部)上路由噪声信号有助于减少EMI。

图8:微带线与带状线

-

FPGA

+关注

关注

1646文章

22069浏览量

619708 -

接收器

+关注

关注

15文章

2577浏览量

74172 -

接口

+关注

关注

33文章

9032浏览量

153953 -

adc

+关注

关注

99文章

6729浏览量

549609 -

lvds

+关注

关注

2文章

1128浏览量

67646

原文标题:FPGA与高速ADC LVDS数据接口设计考虑

文章出处:【微信号:FPGA研究院,微信公众号:FPGA研究院】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Altera FPGA与高速ADS4249和DAC3482的LVDS接口设计

如何避免FPGA内部操作和ADC数据之间的同步问题?

基于FPGA的LVDS接口应用

LVDS高速ADC接口_Xilinx FPGA实现

具有LVDS输出的LTM9011 ADC的AN147-Altera Stratix IV FPGA接口

wp02-将凌力尔特公司的DDR LVDS ADC与Altera Stratix IV FPGA接口

在配置外部接口的过程当中,需要考虑的因素?

高速ADC与FPGA的LVDS数据接口中避免时序误差的设计考虑

ADC和FPGA之间LVDS接口设计需要考虑的因素

ADC和FPGA之间LVDS接口设计需要考虑的因素

评论