文章来源:学习那些事

原文作者:小陈婆婆

本文介绍了集成电路封装中倒装芯片、BGA、MCM和晶圆级封装范式。

在智能终端轻薄化浪潮中,集成电路封装正面临"尺寸缩减"与"管脚扩容"的双重挤压——处理器芯片为处理海量并行数据需新增数百I/O接口,而存储器却保持相对稳定。这场技术矛盾推动JEDEC、EIAJ等标准组织重构封装规范,催生出倒装芯片、BGA、WLP等创新封装范式。

本文分述如下:

倒装芯片

从BGA到MCM:封装技术的演进与实践

晶圆级封装

倒装芯片

倒装芯片的概念最早能追溯到20世纪60年代,当时IBM为了把芯片粘贴到陶瓷基座上,开发出了一种被称为可控塌陷芯片载体(Controlled Collapse Chip Carrier,通常取首字母简称C4)焊料凸点的工艺,这也是倒装芯片封装技术的源头。

所谓倒装芯片封装,就是把含有键合压点的那一面倒过来,依靠芯片上的凸点(Bump)和管座上对应的电极连接起来。这种贴装技术优势明显,它让器件与基座之间的电连接路径变得最短。

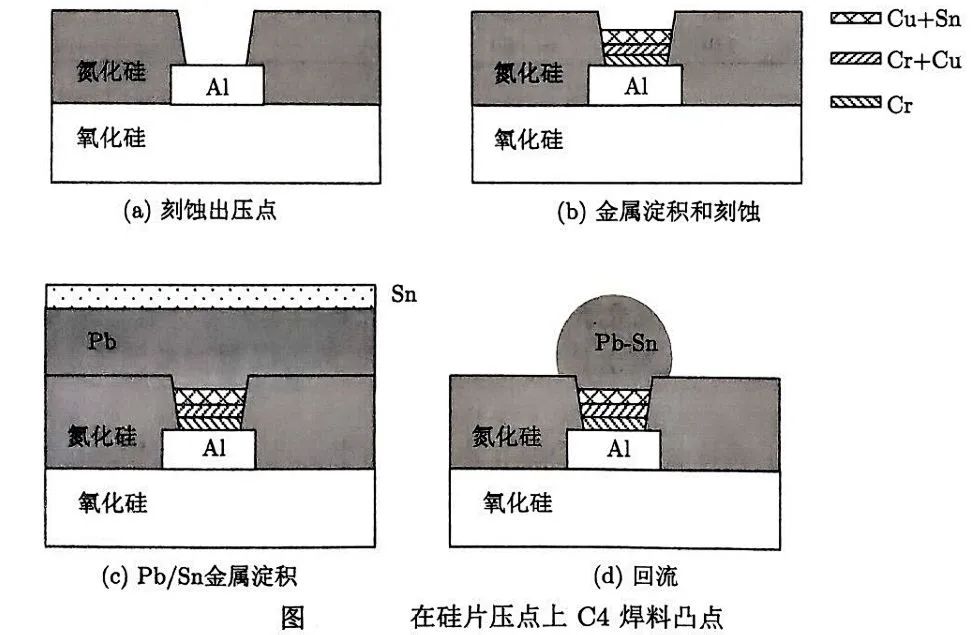

典型的C4焊料凸点制作过程是这样的:先通过蒸发或物理气相淀积(溅射)法,把C4焊料凸点淀积在硅的芯片压点上。这里有个关键点,压点上的C4焊料需要有特殊冶金阻挡层(BLM)。具体操作分几步,先是完成压点刻蚀;接着淀积Cr、Cr + Cu和Cu + Sn复合金属,BLM的作用是让压点和C4焊点有良好的黏附性,还能阻止金属间扩散;然后淀积金属Pb和Sn;最后进行回流,在回流过程中形成焊球。

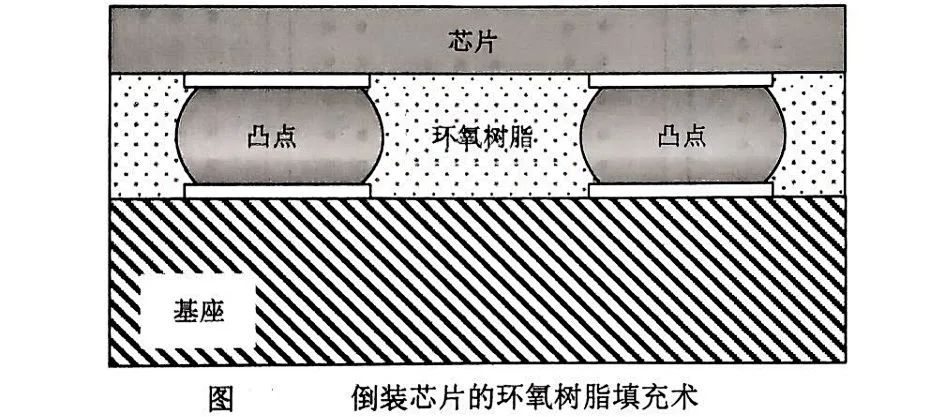

封装基座的材料演变同样精彩:从早期陶瓷基板的高可靠性,到有机基板(如FR-4)的成本优势,再到柔性聚合物电路的弯折特性,基座选择始终围绕“CTE匹配”这一核心命题。硅芯片与基板的热膨胀系数差异(低至2.5ppm/°C vs 高达16ppm/°C)曾是可靠性噩梦,环氧树脂填充术的诞生堪称里程碑——通过毛细作用将低CTE环氧填入芯片与基板间隙,应力可降低至1/10。

不过,倒装芯片封装也存在一些问题。由于硅芯片和基座之间热膨胀系数不一致,严重时导致C4焊点裂缝,使器件早期失效。

针对这个问题,常用的解决措施是用流动的环氧树脂填充在芯片和基座之间,这就是环氧树脂填充术。环氧树脂的CTE能和C4焊点匹配,能有效减小作用于C4结点的应力,使用填充术后应力能减少到原来的1/10。

为了避免倒装芯片不能取下,通常会在电学测试后再施用环氧树脂,也可在芯片与基座之间添加具有互连结构适应的聚合物介质材料,消除两者之间的应力。

从BGA到MCM:封装技术的演进与实践

球栅阵列(BGA)封装

BGA的基座材料选择很多,陶瓷或者塑料都行。制作的时候,会把共晶Sn/Pb焊料球植在基座的电极上,这样就能和PCB上对应的电极连接起来。

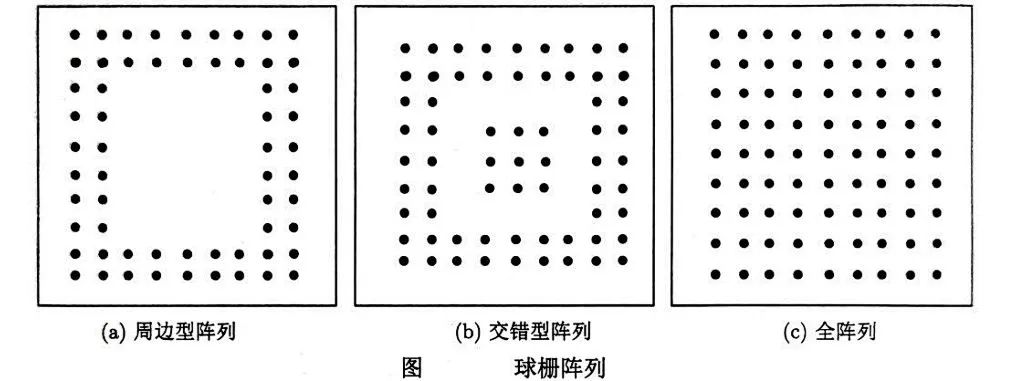

下图为BGA的排列方式。

在小外型的表面贴装上采用BGA,能获得更多的管脚。高密度的BGA封装管脚数多达2400个。BGA焊球间距常见的是1.016 mm、1.270mm或者1.524mm,对应PGA100密耳的管脚间距。现在最新引入的BGA管壳焊料球间距能达到0.508mm,这可是20世纪90年代后期使用的最小BGA间距。

BGA在第二级装配的时候,BGA组件能与其他表面贴组件一起放在印制电路板上,进行焊料回流,形成互连。不仅能把BGA和现存的表面贴装组件工艺集成在一起完成,还能降低装配成本。

从行业最新动态来看,随着5G、人工智能等新兴技术的发展,对高速、高频信号传输的要求越来越高,BGA封装凭借其良好的高频性能,在这些领域的应用前景十分广阔,相关企业也在不断研发新的材料和工艺,以进一步提升BGA封装的性能。

板上芯片(COB)工艺

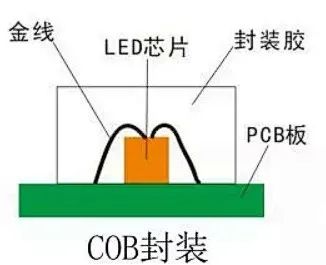

80年代末诞生的板上芯片(COB)技术则在成本敏感领域开辟了新战场。这项将裸芯片直接粘贴到PCB并引线键合的工艺,省去了传统封装的外壳成本,环氧树脂覆盖层更将芯片保护等级提升至IP67。

COB的基座通常就是印制电路板。COB法的工艺步骤其实不难理解,先用传统的贴片工艺把芯片粘贴到基座上,再用前面讲过的引线键合技术,把芯片上的压点和基座上对应的电极进行电连接,最后直接用环氧树脂覆盖在芯片上。

COB法有个很大的优势,它用最少的工艺和设备变化,就能减少传统的SMT和PIH封装尺寸。在那些对尺寸和成本要求很高的领域,像图像游戏卡和智能卡,COB法就越来越流行了。如今,随着物联网设备的普及,对小型化、低成本电子产品的需求不断增加,COB工艺也在不断优化,以提高生产效率和产品可靠性,满足市场的需求。

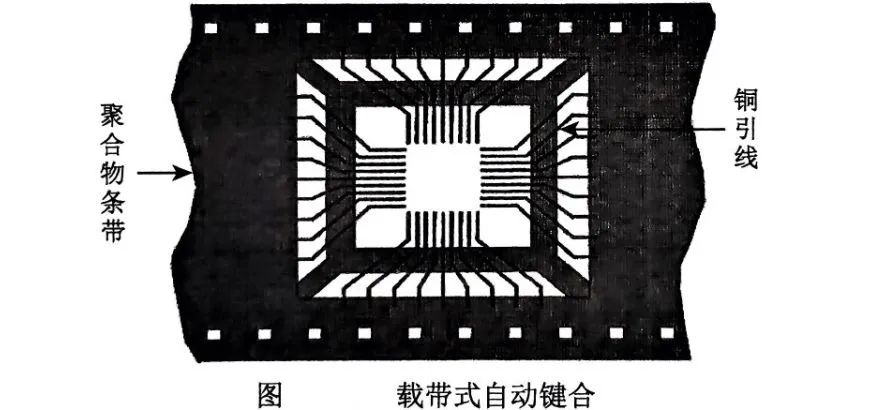

载带式自动键合(TAB)

在封装自动化进程中,载带式自动键合(TAB)曾被视为“引线键合的终结者”。这项采用铜箔载带、通过内引脚(ILB)和外引脚(OLB)实现芯片级互联的技术,在80年代末的DRAM市场中占据过30%份额。

TAB采用的是塑料带作为芯片载体,带子夹着两层聚合物介质膜,中间是薄铜箔。把薄铜箔刻蚀成和芯片压点匹配的电极,这电极又分为含有黏附芯片凸点的内电极键合区(ILB)和用于焊料黏附到电路板的外电极键合区(OLB)。

把芯片粘贴在ILB上后,用环氧树脂把芯片覆盖起来,再把带子卷成卷,这样在印制电路板进行第二级装配的时候就能用了。然而,设备成本高昂(单条载带生产线投资超500万美元)和良率瓶颈(早期ILB键合良率仅85%)使其逐渐退出主流。但TAB并未消失——日本东芝在2022年推出的汽车用LIDAR芯片中,采用预镀铜载带与激光焊接技术,将引脚间距压缩至40μm,成功应对自动驾驶对毫米波雷达信号完整性的挑战。

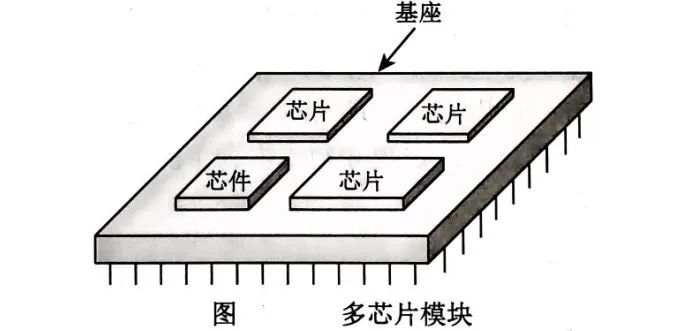

多芯片模块(MCM)

从早期混合电路技术中脱胎而来的MCM,通过将CPU、存储器、模拟芯片集成于陶瓷或有机基板,将模块级密度提升至“单平方厘米百万晶体管”量级。摩托罗拉在90年代末的PowerPC模块中,采用MCM-C(陶瓷基板)方案,将三个芯片的互联延迟降低至传统PCB的1/10。而现代MCM已演变为3D封装的基石——英特尔的Foveros技术通过硅中介层实现逻辑芯片与HBM内存的垂直堆叠,2024年发布的Meteor Lake处理器更将MCM与EMIB(嵌入式多芯片互联桥接)结合,使跨芯片通信带宽达到1.6TB/s。

MCM封装既能减小总封装尺寸和重量,又能减小电路电阻和寄生电容,进而增强集成电路的电性能。

在当下,随着人工智能、大数据等领域的快速发展,对高性能计算的需求日益增长,MCM技术能够将多个高性能芯片集成在一起,提高系统的整体性能,因此受到了越来越多的关注。许多科研机构和企业都在加大研发投入,致力于开发更先进的MCM封装技术,以满足未来高性能计算的需求。

晶圆级封装

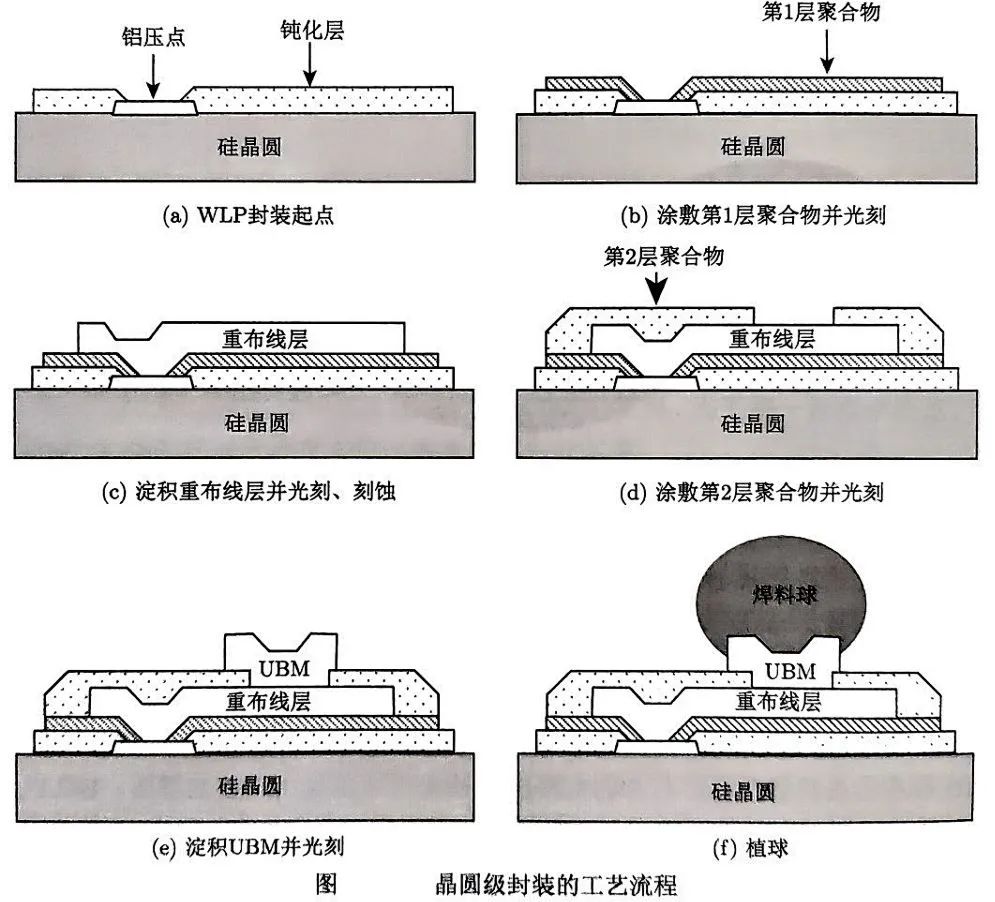

20世纪90年代末,晶圆级封装(WLP)技术的诞生彻底改写了芯片封装的底层逻辑。这项将封装工序前移至晶圆阶段的创新,打破了"先切割芯片再封装"的传统范式——在硅晶圆尚未划片前,便通过薄膜再分布(RDL)工艺将芯片压点重新排布,直接在晶圆表面构建出BGA焊球阵列。这种"先封装后切割"的模式,不仅将封装尺寸压缩至芯片本体的1:1比例,更将测试、老化等后道工序整合至晶圆阶段,使单颗芯片的制造成本降低40%以上。

晶圆级封装得用到倒装芯片的材料和工艺技术,它本质上是以BGA技术为基础改进的cSP,也叫晶圆级 - 芯片尺寸封装(WLP - CSP)。晶圆级封装有个关键难题,就是在芯片压点细节距尺寸和第二级电路板装配需要的粗节距尺寸之间的界面处,得开发出可靠的互连系统。一种常用的办法是用薄膜涂层工艺,在芯片压点和要黏附芯片的电路板上的较大尺寸压点之间搭建起桥梁。BGA焊料球阵列就派上用场了,它能直接把芯片粘贴在第二级装配电路板上。

说到这,就不得不提薄膜再分布工艺制成芯片和界面之间的互连流程了。

流程比较复杂,首先是WLP的起点,这时候已经完成了前道工艺的所有步骤。接着涂敷第1层聚合物薄膜,还得进行光刻。这聚合物薄膜可不简单,它能加强芯片的钝化层,还能起到应力缓冲的作用。最常用的就是光敏性聚酰亚胺,它是一种负性胶。然后是重布线层(RDL),这一步是为了对芯片的铝压点位置重新布局,让新焊点区满足焊料球最小间距的要求,还得让新焊点区按照阵列排布。常见的RDL材料是电镀铜,还得辅助以底层的钛、铜溅射层。

接下来涂敷第2层聚合物薄膜,让晶圆表面变得平坦,同时保护好RDL层。这第2层聚合物薄膜也得经过光刻,开出新焊点区。之后就是淀积金属层凸点下金属层(UBM),制作工艺和RDL差不多。再然后就是植球环节,早期的焊料球是铅锡合金,现在为了环保,都改用锡银铜合金作为WLP的焊料球材料。

通过掩模版的开孔把焊料球放置在UBM上,最后把植球后的晶圆推进回流炉进行回流,让焊料球融化后和UBM形成良好的浸润结合。

凸点制作技术可是WLP工艺过程的关键工序,它得在晶圆的焊点区铝电极上形成凸点。WLP制作凸点的方法有很多种,各有优劣。在用之前,得好好琢磨琢磨,认真选择。在晶圆凸点制作里,金属淀积的成本能占总成本的50%以上呢。而最常见的金属淀积步骤就是UBM的淀积和凸点本身的淀积,一般采用电镀工艺。

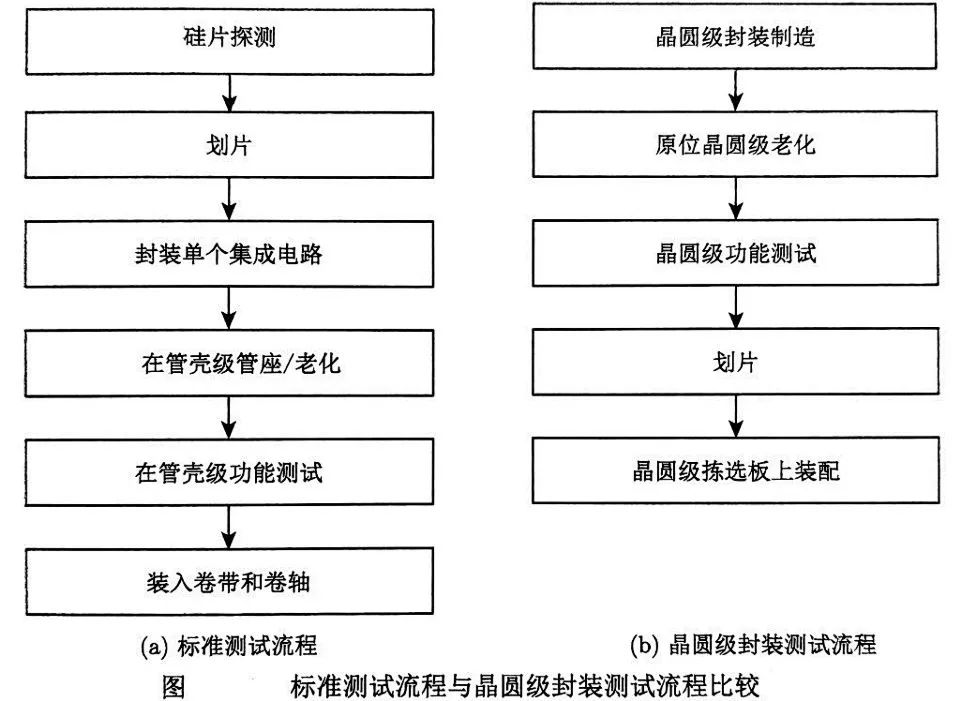

下图列出了常规封装的标准测试流程和圆片级封装测试流程。

从这图里能看出来,装配和封装工艺用晶圆级封装就能实现,测试和老化也能在硅晶圆上进行。因为晶圆级封装后芯片焊料凸点间距比硅片上压点的间距大多了,所以测试用的探针卡就能变得更简单。而且晶圆级封装的老炼筛选不用专门定制测试管座,还能减少一次中测。这样一来,晶圆级封装既提高了测试效率,又降低了测试成本。

晶圆级封装的优势相当明显。在x和y维度上,它的管壳大小和芯片面积一样,是最小最轻的集成电路封装形式。在高度方向上,它能做到极薄型,第二级装配后从电路板表面算起总高度小于1.0mm。

而且芯片面朝下的晶圆级封装结构,电路路径短,寄生电感和电容小,能让电学性能达到最优。它还能和现有的表面贴装技术兼容,使用标准的焊料球及球间距,减少了重复测试和集成电路块的装卸,从而降低了系统总成本。

现在,随着电子产品向小型化、高性能、低成本方向发展,晶圆级封装技术在5G通信、人工智能、物联网等领域的应用越来越广泛,各大厂商都在不断加大研发投入,提升晶圆级封装的技术水平和生产效率,以满足市场的需求。

-

集成电路

+关注

关注

5430文章

12139浏览量

368937 -

封装

+关注

关注

128文章

8741浏览量

145732 -

倒装芯片

+关注

关注

1文章

108浏览量

16630

原文标题:现代装配与封装

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

集成电路封装类型介绍

集成电路封装类型介绍

评论