在当今科技飞速发展的时代,人工智能、大数据分析、云计算以及高端图形处理等领域对高速、高带宽存储的需求呈现出爆炸式增长。这种背景下,高带宽内存(High Bandwidth Memory,HBM)技术成为了全球存储芯片巨头们角逐的焦点。三星电子作为行业的领军企业,一直致力于推动 HBM 技术的革新。近日有消息传出,三星电子准备从 16 层 HBM 开始引入混合键合技术,这一举措无疑将在存储芯片领域掀起新的波澜。

编辑

?

编辑

?

技术背景:HBM 发展的必然趋势

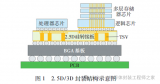

随着数据量的指数级增长和数据处理速度要求的不断提高,传统的内存技术逐渐难以满足日益严苛的需求。HBM 技术通过垂直堆叠多颗 DRAM 芯片,并利用硅通孔(TSV)进行连接,极大地提升了数据处理性能。从 HBM2e 到 HBM3e,再到即将到来的 HBM4,各大厂商不断在提升内存带宽和容量方面发力。

在过去的 HBM 制造过程中,通常采用在每层 DRAM 之间放置微小凸点(Bump),并通过热压接(Thermal Compression,TC)的方式进行连接。然而,当 HBM 堆叠层数朝着 16 层、20 层甚至更高发展时,传统的热压接方式暴露出了诸多问题。其中一个关键限制因素是 HBM 封装的整体厚度必须控制在最大 775 微米(μm)以内。虽然可以尝试通过进一步削薄 DRAM 芯片或者缩小层间距来应对,但这些方法都存在着物理极限。例如,将核心芯片厚度做得比 30 微米更薄在实际操作中就面临极大挑战,而且由于凸点本身具有一定体积,通过凸点连接芯片在增加堆叠层数和降低整体高度方面的局限性愈发明显。这就促使业界必须寻找一种新的技术来突破这些瓶颈,混合键合技术应运而生。

混合键合技术解析:创新的连接方式

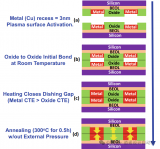

混合键合技术是一种全新的内存键合方式,与传统的键合工艺相比,具有革命性的变化。其核心在于摒弃了在 DRAM 内存层之间添加凸点这一传统做法,而是直接利用铜将上下层进行连接,实现了铜对铜的直接连接。

这种创新的连接方式带来了多方面的优势。首先,信号传输速率得到了大幅提升。在传统的键合方式中,凸点的存在会在一定程度上影响信号的传输速度,而混合键合直接的铜连接减少了信号传输的阻碍,使得数据能够以更快的速度在不同层之间传递,这对于 AI 计算等高带宽需求的应用场景来说至关重要。以人工智能领域为例,在处理大规模的数据运算和复杂的模型训练时,高带宽的内存能够极大地提高运算效率,减少计算时间,让 AI 模型能够更快地收敛和优化。

其次,混合键合技术能够显著降低 DRAM 层之间的距离,进而降低 HBM 模块的整体高度。通过缩小芯片间的间隙,在有限的 775 微米高度限制内,可以实现更多芯片的堆叠,例如能够在该高度内封装 17 个芯片(一个基底芯片和 16 个核心芯片)。这不仅提高了内存的集成度,也有助于在有限的空间内实现更高的存储容量和性能。

三星的战略布局:双轨策略并行

三星电子在 HBM4 内存键合技术方面采取了稳健且具有前瞻性的双轨策略。一方面积极推进混合键合技术的研发与应用,另一方面也没有放弃对传统的 TC - NCF(热压缩氮化硅填充)工艺的优化。

三星电子计划最快从 HBM4E(第七代高带宽存储器)开始导入混合键合技术。为了实现这一目标,目前三星正在向客户提供基于混合键合的 16 层 HBM 样品,并进行全面的评估测试。这一举措显示了三星对混合键合技术的信心以及对市场需求的敏锐把握。通过提前向客户提供样品,能够及时收集客户的反馈,对技术进行进一步的优化和改进,确保在正式量产时能够满足市场的高要求。

与此同时,三星也在不断探索和优化 TC - NCF 工艺。虽然外界对于 TC - NCF 技术在应对 16 层及以上堆叠时存在一定的质疑,但三星认为其解决方案相较于竞争对手 SK 海力士的 MR - RUF(某种先进封装技术),更适合用于 12 层甚至 16 层的高堆叠模块。三星正努力将 TC - NCF 工艺中的晶圆间隙缩小,目标是在 HBM4 中将其高度降至 7.0 微米以内。通过对传统工艺的持续改进,三星旨在充分发挥 TC - NCF 工艺的优势,同时弥补其在面对高堆叠层数时的不足,为不同客户的需求提供多样化的选择。

面临的挑战与机遇:技术与市场的双重考验

尽管混合键合技术展现出了巨大的潜力,但在实际应用和推广过程中,仍然面临着一些挑战。

从技术层面来看,混合键合技术的成熟度相对不足。作为一种新兴的技术,其在工艺稳定性、良品率等方面还需要进一步提升。例如,在芯片直接连接的过程中,如何确保每一层之间的连接质量一致,避免出现连接不良导致的性能问题,是需要攻克的技术难题。而且,由于技术难度高,对设备和操作人员的要求也更为严格,这在一定程度上增加了技术实施的复杂性。

从成本角度考虑,混合键合技术的应用成本较高。一方面,从传统的 TC 键合切换到混合键合需要大量的设备投资,企业需要购置新的混合键合设备,对现有的生产线进行改造,这无疑会增加企业的前期投入成本。另一方面,由于技术尚未大规模普及,生产规模相对较小,导致单位产品的成本居高不下。这对于追求性价比的市场来说,可能会在一定程度上影响混合键合技术的推广速度。

然而,挑战与机遇总是并存。随着人工智能、大数据等新兴技术的持续发展,对高带宽内存的需求将持续增长,这为混合键合技术提供了广阔的市场空间。一旦三星能够成功克服技术和成本方面的障碍,实现混合键合技术在 16 层 HBM 上的大规模应用,将在市场竞争中占据极为有利的地位。而且,随着技术的成熟和生产规模的扩大,成本也有望逐渐降低,从而进一步推动市场的需求增长。

此外,三星在筹备定制化 HBM(Custom HBM)业务方面也看到了新的机遇。目前,包括谷歌、英伟达、AMD 等在内的多家全球大型科技公司,都在寻求适用于其 AI 芯片的专属定制 HBM 产品。三星凭借其在 HBM 技术领域的深厚积累和对混合键合技术的积极探索,有望在定制化 HBM 市场中分得一杯羹。通过开发将运算功能集成至基底晶片(Base Die)等具有三星特色的定制 HBM 产品,满足不同客户的个性化需求,进一步提升三星在存储芯片市场的竞争力。

三星电子准备从 16 层 HBM 开始引入混合键合技术,是其在存储芯片领域持续创新和战略布局的重要体现。这一举措不仅有望推动 HBM 技术迈向新的高度,满足不断增长的市场需求,也将对整个存储芯片行业的竞争格局产生深远影响。在未来,我们期待看到三星在混合键合技术方面取得更多突破,为全球科技发展注入新的动力。

来源:半导体芯科技

审核编辑 黄宇

-

半导体

+关注

关注

335文章

29027浏览量

239958 -

三星电子

+关注

关注

34文章

15889浏览量

182453

发布评论请先 登录

从微米到纳米,铜-铜混合键合重塑3D封装技术格局

混合键合市场空间巨大,这些设备有机会迎来爆发

三星在4nm逻辑芯片上实现40%以上的测试良率

闪存冲击400层+,混合键合技术传来消息

突破堆叠瓶颈:三星电子拟于16层HBM导入混合键合技术

突破堆叠瓶颈:三星电子拟于16层HBM导入混合键合技术

评论