DisplayPort LTTPRs 重定时时钟频率变化

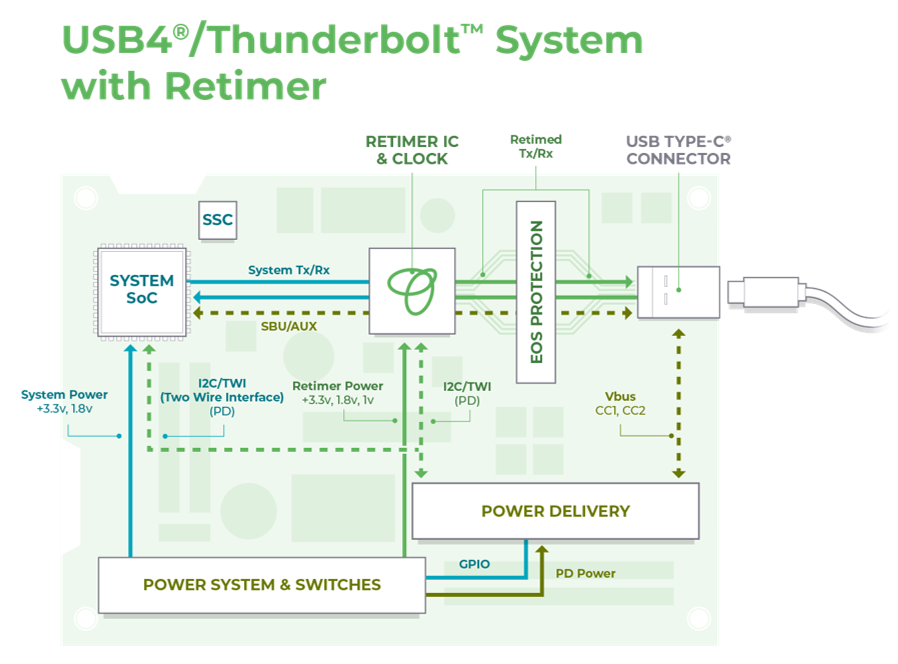

在DisplayPort中,所有链路建立通信都是通过DP-AUX通道实现的。DP-AUX是一个1Mbps的曼彻斯特编码总线,与高速信号是异步的。图1展示了USB-C下行端口通过重定时器到SoC的SBU/AUX路径。

图1

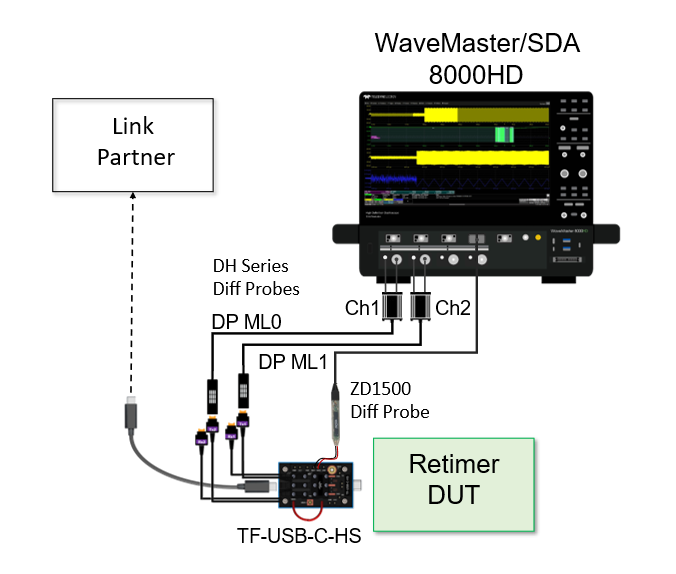

为了验证重定时器性能正常,频率变化符合规范要求,设置WaveMaster/SDA8000HD同时探测和捕获SBU/AUX信号和ML0/ML1高速信号。

在图2中,Retimer DUT连接到已知性能好的LinkPartner。

图2

重定时器频率变化测试是通过确保频率变化参数在规范容许范围内来进行的,这就要求以尽可能高的采样率采集重定时器信号,以便进行精确测量。然而,要在重定时器开始用重定时时钟传输数据时触发示波器比较困难。由于需要很高的采样率,设置触发器的微小延迟都会导致占用大量的示波器存储深度,并可能导致无法在感兴趣的时间内采集信号。

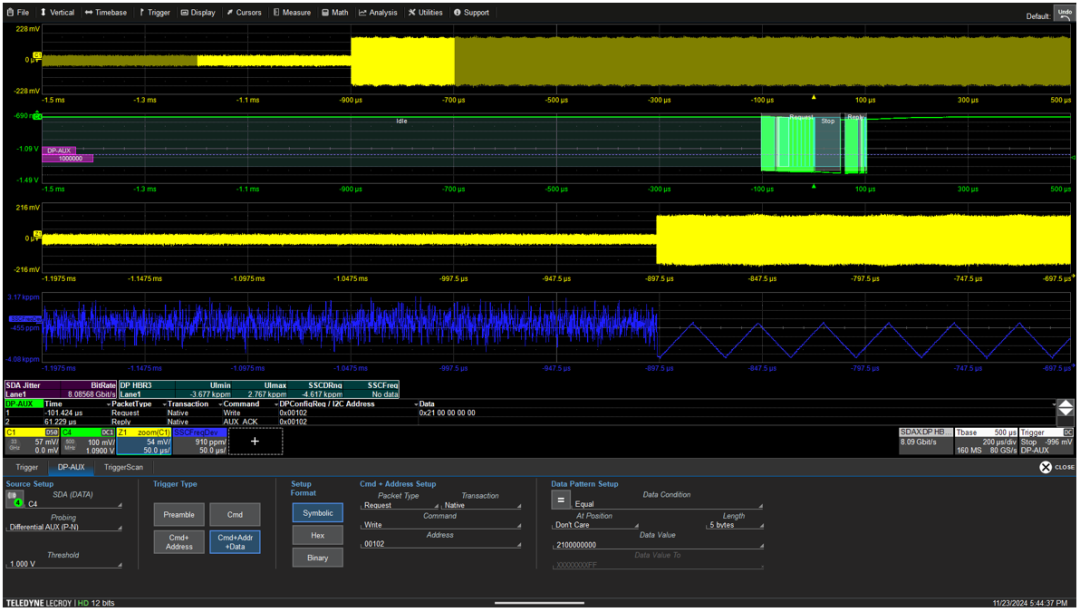

图3显示的是使用示波器的DP-AUX解码捕捉整个链路事务序列,以发现重定时器何时开始传输重定时数据。从图中可以看出,在光标C1所显示的关注点之前发生了许多AUX事务。在解码数据中搜索启动重定时信号的AUX命令,发现TRAINING_PATTERN_SET(地址0x00102)的5字节数据值设置为(0x21000000)。然而,现在示波器采样率设置得很低(10MS/s),可以捕捉很长时间,因此只能看到Lane0信号的轮廓(右上角黄色Z1曲线)。要准确捕捉Lane0信号,必须提高示波器的采样率,但这会减少示波器的采集时间。因此,必须使用DP-AUX触发器在感兴趣的时刻捕捉较短的时间段。

图3

图4显示了以全采样率(80GS/s)捕获重定时器启动的DP-AUX触发器设置,以便使用TeledyneLeCroy SDA Expert示波器软件选件测量扩频时钟(SSC)变化。频率变化测试通常是在PHY合规性测试期间进行的,但这种设置允许在可能出现互操作性问题的实时链路中进行。

图中清楚地显示了示波器对DP-AUX事件的触发(绿色C4波形),以及Lane0数据信号的相关变化(Z1是放大的通道1波形)与扩频时钟信号的频率变化(计算出的蓝色SSCFreqDev曲线)。

图4

您可通过下载《掌握链路训练,确保USB4和DisplayPort设计成功》白皮书查看更多 DisplayPort LTTPRs 的常见问题以及其他案例。

Type-C接口凭借强大的功能和便利性,在各类设备中的得到广泛应用。越来越多用户反馈接口未按规范工作或存在间歇性链路失效的问题。你的设计可能能够通过合规性测试,但还是在互操作性中出现故障,那么你需要深入掌握链路训练(Link Training)相关的调试方法。

近年来,重定时器(Retimer)被大量引入 USB4 和 DisplayPort2.1 系统设计中,以提升信号完整性和链路性能。然而,这也显著增加了链路初始化和稳定性方面的问题,给产品集成带来了更高的复杂度。理解重定时器在链路训练过程中的行为,以及如何有效捕捉和分析训练失败的根因,已成为确保系统可靠性的关键

本白皮书详细介绍了 USB4 和 DisplayPort 设计面临的挑战,重定时器的使用带来的可能问题,以及如何快速定位这些系统互操作性问题。

关于我们

特励达力科(Teledyne Lecroy)是高端示波器、协议分析仪和其他测试仪器的专业制造商,可快速全面地验证电子系统的性能和合规性,并进行复杂的调试分析。

1964 年成立以来,公司一直专注于将强大的工具整合到创新产品中,以提高“洞察时间”。更快的洞察时间使用户能够快速查找和修复复杂电子系统中的缺陷,从而显著缩短产品的上市时间。

-

示波器

+关注

关注

113文章

6731浏览量

189756 -

频率

+关注

关注

4文章

1565浏览量

60472 -

时钟

+关注

关注

11文章

1903浏览量

133365 -

USB-C

+关注

关注

2文章

384浏览量

35043

原文标题:调试案例 | DisplayPort LTTPRs 重定时时钟频率变化

文章出处:【微信号:美国力科TeledyneLeCroy,微信公众号:美国力科TeledyneLeCroy】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于Labview的闹铃定时时钟

f28335定时器频率为150, 定时器周期值为1000. 时钟频率150MHz 。定时时间是1ms ,这是周期寄存器的值应该附多少。怎么算

实时时钟是什么

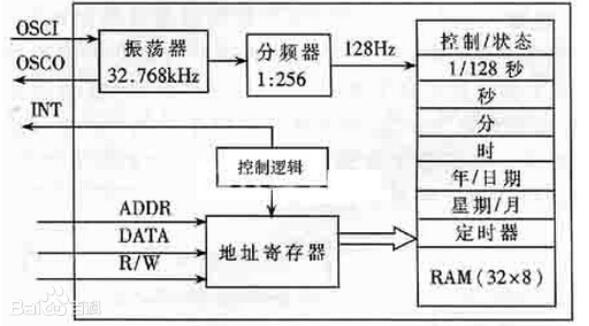

实时时钟芯片应用

TPS65950实时时钟定时补偿分析

浅谈RTC实时时钟特征与原理

慕课嵌入式开发及应用(第三章.周期中断定时器,低功耗定时器,实时时钟)

【实时时钟RTC】MSP430系统实时时钟RTC学习日志(完善中)

DisplayPort LTTPRs重定时时钟频率变化

DisplayPort LTTPRs重定时时钟频率变化

评论