À´Ô´£ºĐ¾Æ¬·â×°×ÛÊö

FOPLP ¼¼ÊơÄ¿Ç°ÈÔĂæÁÙÖî¶à̀ôƠ½£¬°üÀ¨£ºĐ¾Æ¬Æ«̉Æ¡¢Ăæ°åÇ̀Çú¡¢RDL¹¤̉ƠÄÜÁ¦¡¢Åä̀×É豸ºÍ²ÄÁÏ¡¢ÊĐ³¡Ó¦ÓĂµÈ·½Ăæ¡£

£¨1£©Die Æ«̉Æ

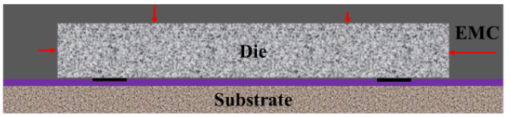

Ôڳߴç¹æ¸ñ·½Ă棬·½ĐÎĂæ°åµÄ³ß´ç̉»Ö±ÔÚÔö¼Ó¡£Ä¿Ç°£¬·½ĐΰåµÄ³ß´ç°üÀ¨300x300mm¡¢510mmx415mm¡¢515mmx510mm¡¢600mmx600mm¡¢615x625mm¡¢620mmx750mm¡¢700mmx700mm¡¢800x600mm¡¢800x800mm¡£ËäÈ»´ó³ß´ç·½ĐÎĂæ°åµÄ³É±¾½ÏµÍ£¬µ«¸ü´óµÄ³ß´ç̉²¸üÈỬ×µ¼ÖÂĂæ°åÇ̀Çú£¬´Ó¶øÓ°Ḯ¾«¶ÈºÍĐ¾Æ¬Æ«̉Æ£¬µ¼ÖÂÁ¼ÂʽµµÍ¡£ÔÚmolding¹ư³̀ÖĐ²úÉúµÄĐ¾Æ¬Æ«̉ƸøRDL·Ö²¼´øÀ´Á˷dz£ÑÏÖصÄÎỀâ¡£molding¹ư³̀ÖĐĐ¾Æ¬Î»̉ÆĐγɵĽṹÈçÏÂͼËùʾ¡£

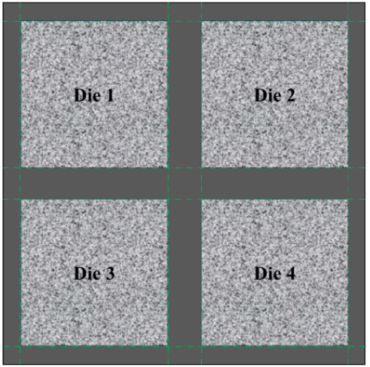

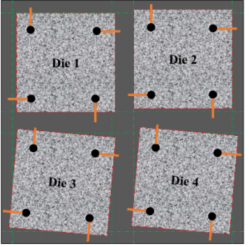

´¦ÓÚÁ÷¶¯×´̀¬µÄEMC»á´Ó¸÷¸ö·½Ị̈¶ÔƠ³̀ùÔÚĂæ°åÉϵÄĐ¾Æ¬²úÉú³å»÷Á¦¡£ƠâĐ©¼¯ÖĐÔÚĐ¾Æ¬Éϵijå»÷Á¦´óĐ¡²»ÏàµÈ£¬´Ó¶ø̉ư·¢Đ¾Æ¬Æ«̉Æ£¬½ø¶øµ¼ÖÂĐè̉ª¶Ô¸²¸ÇÔÚEMC²ă±íĂæµÄRDL²ă½øĐĐÖØĐ²¼¾Ö¡£Í¬Ê±£¬ÔÚmolding¹ư³̀ÖĐ£¬Ă¿¸öĐ¾Æ¬¶¼»á²úÉú²»Í¬µÄλ̉Æ£¬ƠâÓÖʹµĂĂ¿¸öĐ¾Æ¬¶¼Đè̉ª̀ض¨µÄ³ơʼRDL²ă·Ö²¼£¬̉ÔÂú×ăÆäµçÆø̉ªÇó¡£ÔÚÄ£Đ͹¹½¨¹ư³̀ÖĐ£¬ÀíÏëµÄĐ¾Æ¬·Ö²¼Çé¿öÈçÏÂͼËùʾ£¬Ă¿¸öĐ¾Æ¬¶¼ÈÔ¸½×ÅÔÚĂæ°åÉÏ£¬²¢ÓÉEMC̉Էdz£ÓĐĐ̣µÄ·½Ê½·â×°£¬Ç̉Đ¾Æ¬1ÖÁĐ¾Æ¬4¾ùδ³öÏÖĐ¾Æ¬Î»̉Æ¡£

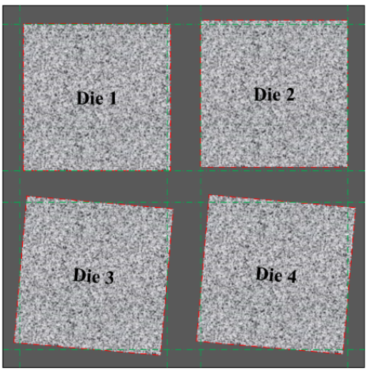

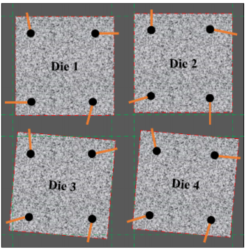

Đ¾Æ¬Æ«̉ƵÄÄ£ĐÍÈçÏÂͼËùʾ£¬Đ¾Æ¬1ÖÁĐ¾Æ¬4¾ụ̀̉molding¹ư³̀ÖĐEMCÁ÷¶¯µÄ³å»÷Á¦¶ø²úÉúÁ˲»Í¬³̀¶ÈµÄλ̉Æ¡£Đ¾Æ¬1ÔÚˮƽ·½Ị̈ÉÏ·¢ÉúÁËÓ̉תλ̉Æ£¬Đ¾Æ¬2ÔÚ´¹Ö±·½Ị̈ÉÏ·¢ÉúÁËÉÏ̉Æλ̉Æ£¬Đ¾Æ¬3Ộ·¢ÉúÁË˳ʱƠëĐưתλ̉Æ¡£Ïà±È֮ϣ¬Đ¾Æ¬4¾ßÓĐÓÉˮƽ·½Ị̈λ̉Æ¡¢´¹Ö±·½Ị̈λ̉ƺÍĐưת×é³ÉµÄÄ£¿é»¯Đ¾Æ¬Æ«̉Æ¡£»»ÑÔÖ®£¬Ç¶ÈëEMC²ăÖеÄĐ¾Æ¬ÔÚ½¨Ä£¹ư³̀ÖĐ¾ßÓĐ²»Í¬µÄĐ¾Æ¬Æ«̉Æ¡£

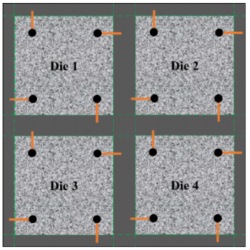

ÔÚmolding¹ư³̀ÖĐÓÉÓÚ¸÷ÖÖĐ¾Æ¬Æ«̉ƶøµ¼ÖµÄRDL²ă¸²¸ÇÔÚEMC²ăÉÏʱ£¬·Ö²¼Çé¿ö̉́³£¸´ÔÓ¡£ÎªÁ˽â¾öƠẩ»¼¬ÊÖÎỀ⣬̉ưÈëÁË×Ô¶¯¹âѧ¼́²é(AOI)Á÷³̀£¬̉ÔÅжÏÔÚ¸÷ÖÖĐ¾Æ¬Æ«̉ƵÄÇé¿öÏÂĂ¿¸öº¸Å̀µÄÈ·ÇĐλÖĂ£¬È»ºó¸ù¾ƯAOI½á¹û´´½¨ĐµÄRDL lay-out¡£Ëæºó£¬¸ù¾ƯеĵÚ̉»RDL²ălay-outĐγÉÍêƠûµÄRDL²ă¡£ÈçÏÂͼËùʾ£¬ÔÚĂ»ÓĐÈκÎĐ¾Æ¬Æ«̉ƵÄÇé¿öÏ£¬Ă¿¸öº¸Å̀ÖÜΧµÄµÚ̉»RDL²ă·Ö²¼ÍêÈ«Ïàͬ£¬Ç̉Ă¿¸öº¸Å̀µÄµÚ̉»RDL²ă·Ö²¼µÄ¶ËµăλÖĂÊǹ̀¶¨µÄ¡£

ËäÈ»»ùÓÚ½¨Ä£¹ư³̀ÖĐ²úÉúµÄ¸÷ÖÖĐ¾Æ¬Æ«̉Æ£¬µ«̉ưÈëAOIÁ÷³̀ºÍеĵÚ̉»RDL²ălay-outºó£¬¿É̉Ô¸²¸ÇǶÈëEMC²ăÖи÷ÖÖĐ¾Æ¬Æ«̉ÆÇé¿öµÄĂ¿¸öpad¡£ÈçÏÂͼËùʾ£¬Èô²»½øĐĐpadλ̉ÆĐ£Ơư£¬Ă¿¸öpadÖÜΧµÄµÚ̉»RDL²ă·Ö²¼½«ÊDz»Í¬µÄ£¬Ç̉Ă¿¸öpadµÄµÚ̉»RDL²ă·Ö²¼µÄ¶Ëµă½«ÊÇËæ»úµÄ¡£

ÈçÏÂͼËùʾ£¬¾¹ưpadλ̉ÆĐ£Ơưºó£¬Ă¿¸öpadÖÜΧµÄµÚ̉»RDL²ă·Ö²¼ËäÈ»¸÷²»Ïàͬ£¬µ«Ă¿¸öpadÓëµÚ̉»RDL²ă·ÖÅäµÄ¶Ëµẳ²Êǹ̀¶¨µÄ¡£

ÓëÀíÏëÄ£ĐÍÏà±È£¬ÉÏͼËùʾµÄĂ¿¸öpadµÄÊ׸öRDL²ă·Ö²¼µÄ¶Ëµă²¢Î´¸Ä±ä£¬´Ó¶øÄܹ»È·±£ºóĐøµÄ¶Û»¯²ăͼ°¸»¯̉Ô¼°RDL²ă·Ö²¼¿É°´ƠƠ×î³ơÉè¼Æ±£³Ö²»±ä¡£

£¨2£©Ăæ°åÇ̀Çú

ÔÚFOWLP·â×°¹ư³̀ÖĐ£¬ÓÉÓÚÈÈÓ¦Á¦ºÍ»úеӦÁ¦µÄÀÛ»ư£¬»áµ¼ÖÂÖع¹¾§Ô²Ç̀Çú£¬Ơâ»áÓ°ḮºóĐøÑÚÄ£°å¹â¿̀¹¤̉ƠµÄ¼Ó¹¤¾«¶È£¬²¢Ï̃ÖƲ¼Ïß²ăĂܶȵÄ̀áÉư¡£¶ø¶ÔÓÚFOPLP¼¼Êơ£¬Ëæ×ÅĂæ°å³ß´çµÄÔö´ó£¬Ăæ°åÇ̀ÇúÎỀâ±äµĂ¸üΪÏÔÖø£¬̣̉´ËÔÚĐè̉ª¼«¸ßƽƠû¶ÈµÄ¹¤̉Ơ½×¶Î£¬ÈçÎïÀíÆøÏà³Á»ư(PVD)ºÍ¹â¿̀½×¶Î£¬¿ÉÄܻᱻÆÈÖĐ¶Ï·â×°Á÷³̀¡£Ç̀Çú²úÉúµÄÓ¦Á¦ºÜÈỬ×¼¯ÖĐÔÚÖĐ¼ä²ă»̣º¸µă´¦£¬µ¼Öº¸Ç̣¿ªÁÑÍÑÂä¡¢ÖĐ¼ä²ă·Ö²ăµÈÎỀâ¡£ÔÚFOPLP¼¼ÊơÖĐ£¬Ăæ°åÇ̀ÇúµÄÖ÷̉ªỘ̉±»¹ă·ºÈÏΪÊÇEMC¹̀»¯¹ư³̀ÖĐÓɲ»Í¬²ÄÁϵÄÈÈẠ̊ƠÍϵÊư(CTE)²»Æ¥Åäµ¼Ö¡£´ËÍ⣬»¹·¢ÏÖÁËĐí¶àÆäËụ̂̉ËØ̉²¿ÉÄÜÓ°ḮĂæ°åÇ̀Çú£¬ƠâĐ©̣̉ËØ°üÀ¨¹èµÄ¸÷Ị̈̉́ĐÔ¡¢EMCµÄƠ³µ¯ĐÔºÍËɳÚЧӦ¡¢ÖØÁ¦¡¢¹̀»¯ºóµÄ¹¤̉Ơ»·¾³£¬̀رđÊÇÔÚζȼ±¾ç±ä»¯µÄ¹¤̉Ơ»·¾³ÖĐ£¬ÈçÖ²Ç̣µÈ¡£ Ăæ°å³ß´çÔ½´ó£¬²úÉúµÄÇ̀Çú±äĐξÍÔ½ÏÔÖø¡£ÔÚFOPLP·â×°ÖĐ£¬Ăæ°åÇ̀Çú̉ѳÉΪÏ̃ÖÆÆä·¢Ơ¹µÄÖØ̉ªÎỀ⡣ΪÁ˾¡¿ÉÄܼơĐ¡Ăæ°åÇ̀Çú´øÀ´µÄÓ°Ḯ£¬ÔÚĂ¿̉»¸ö¼ÓÈȹ¤Đ̣ºó¶¼̉ưÈëÁ˸öƽƠû»¯´¦Àí²½Ö裨̉²³ÆÇ̀Çú½ĂƠư¡¢Ç̀ÇúƠûƽ£©¡£

£¨3£©RDL¹¤̉ƠÄÜÁ¦

¾ÍFOPLP¼¼ÊơµÄRDL¹¤̉Ơ¶øÑÔ£¬Ïß¿íºÍÏß¾àÄ¿Ç°̉Ñ´ïµ½10¦̀m/10¦̀m£¬̉²ÓĐÖÆỐÉ̀²ÉÓĂ5¦̀mµ½2¦̀m²»µÈµÄ¹¤̉Ơ¡£Î´À´Ç÷ÊÆÊdz¯×ÅÓ뾧Բ¼¶·â×°ÏàͬµÄ¹¤̉ƠÄÜÁ¦·¢Ơ¹£¬ÉơÖÁ¿ÉÄÜÍ»ÆÆĂæ°å¼¶·â×°µÄÎïÀíÏ̃ÖÆ£¬´ïµ½1¦̀m¡£Èç¹ûÎ̉ĂÇƠæµÄÄܹ»ÊµÏÖ5¦̀m/5¦̀mÏß¿í/Ïß¾àµÄÁ¿²ú£¬¸Ă¼¼Êơ½«×ẳÔÀ©Ơ¹µ½¸ü¶àĐè̉ª¸ßĐÔÄÜ¡¢É¢ÈȺÍЧÂʵĸ߶ËÓ¦ÓĂÖĐ£¬ÓÈÆäÊÇÉæ¼°ÓĐÔ´ºÍÎ̃Ô´Æ÷¼₫µÄ¶àĐ¾Æ¬ºÍ̉́¹¹̉́Öʼ¯³É¡£ÎªÁËÔÚFOPLPÖĐ»ñµĂ¸ü¸ßµÄ·Ö±æÂÊ£¬¸ßĂܶÈRDL(Ïß¿í/Ïß¾àĐ¡ÓÚ5¦̀m)ÈÔĐè̉ª¿Ë·₫δÀ´µÄ¼¼ÊờôƠ½¡£ÀưÈçÔÚFOPLP¼¼Êơ¹ư³̀ÖĐ£¬ÈçºÎÔÚ´óĂæ»ưĂæ°åÉÏʵÏÖ¾ùÔȵÄÊ´¿̀ËÙÂʺʹóĂæ»ưµÄµç¶Æ¾ùÔÈĐÔ£¬Ê¹Ïß¿í/Ïß¾à´Ó20¦̀m/20¦̀mÖđ²½½µÖÁ15¦̀m/15¦̀m£¬½ø¶ø´ïµ½10¦̀m/10¦̀m£¬ÈÔÊÇ̉»¸ö¾̃´óµÄ̀ôƠ½¡£

-

Đ¾Æ¬

+¹Ø×¢

¹Ø×¢

460ÎÄƠÂ

52568ä¯ÀÀÁ¿

441885 -

·â×°

+¹Ø×¢

¹Ø×¢

128ÎÄƠÂ

8717ä¯ÀÀÁ¿

145633 -

¹¤̉Ơ

+¹Ø×¢

¹Ø×¢

4ÎÄƠÂ

687ä¯ÀÀÁ¿

29488 -

emc

+¹Ø×¢

¹Ø×¢

172ÎÄƠÂ

4181ä¯ÀÀÁ¿

187181

ÔÎıề⣺FOPLP¹¤̉ƠĂæÁÙµÄ̀ôƠ½

ÎÄƠ³ö´¦£º¡¾Î¢ĐźţºÉîÛÚÊĐÈüÄ·Ï©½đ¿Æ¼¼ÓĐÏ̃¹«Ë¾£¬Î¢ĐŹ«ÖںţºÉîÛÚÊĐÈüÄ·Ï©½đ¿Æ¼¼ÓĐÏ̃¹«Ë¾¡¿»¶Ó̀í¼Ó¹Ø×¢£¡ÎÄƠÂתÔØÇë×¢Ă÷³ö´¦¡£

·¢²¼ÆÀÂÛÇëÏÈ µÇ¼

FOPLP¹¤̉ƠĂæÁÙµÄ̀ôƠ½

FOPLP¹¤̉ƠĂæÁÙµÄ̀ôƠ½

ÆÀÂÛ