文章来源:学习那些事

原文作者:前路漫漫

本文介绍了CSP封装(Chip Scale Package)的类型和工艺。

有引脚类型LF-CSP

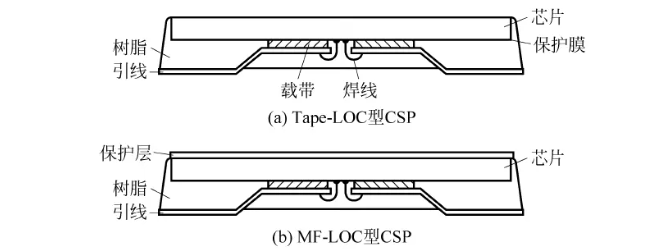

1997年,富士通公司研发出一种名为芯片上引线(Lead On Chip,LOC)的封装形式,称作LOC型CSP。为契合CSP的设计需求,LOC封装相较于传统引线框架CSP做出了一系列革新设计:将芯片焊盘移至中部,把整个引线框架粘贴在芯片上方,焊线后进行塑封;之后将整个封装翻转,使芯片电路面朝下,此时芯片下方引线框架的外引脚与外部线路板的焊接面,与芯片电路面处于同一平面。

通常,引线框架CSP包含Tape-LOC型与MF-LOC型(Multi-frame-LOC,即多框架LOC型)两种。其中,MF-LOC的设计目的是改善Tape-LOC因缺少固晶区而存在的可靠性隐患,它将导线架拆分为上架与固晶架两部分:先把晶粒贴装到固晶架上,再将固晶架与上架组合,从而形成完整的导线架。

无引脚类型LF-CSP

无引脚类型LF-CSP的结构主要为QFN或SON封装形式。为满足CSP的要求,其内部互连需采用倒装方式,或采用CSP线弧焊线工艺。

焊球引脚型LF-CSP

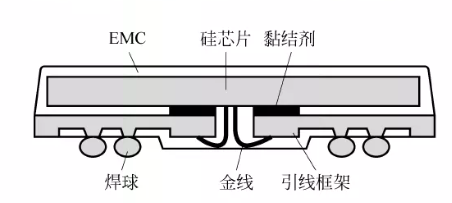

1999年,Jong Tae Moon等人提出了了一种铜引线框架CSP,其工艺流程为:晶圆→芯片磨切→芯片键合→引线键合→模塑→模后固化→去溢料→UBM→焊料球及回流→切边(分割)→电性测试→打标→包装。

刚性基板式CSP

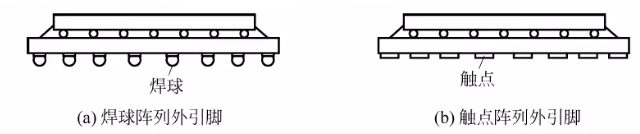

刚性基板式CSP又称刚性内插板CSP,以多层布线陶瓷基板或多层布线层压树脂基板作为芯片载体。根据芯片焊盘与基板焊盘的连接方式,可分为倒装芯片键合型与引线键合型;其外引脚以底部阵列型为主,又可分为焊球型和触点型,可看作缩小版的BGA或LGA封装。

1. 倒装芯片键合类型

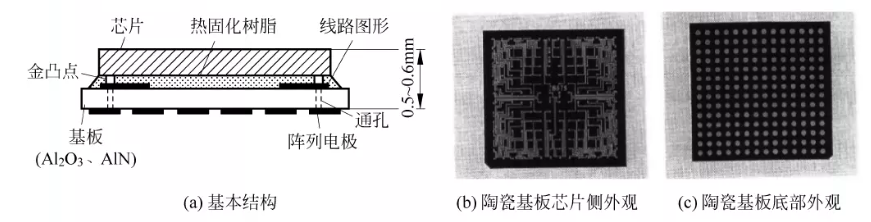

倒装片键合陶瓷基片CSP产品的结构示意图如图所示,其封装工艺流程与倒装BGA/倒装LGA封装一致。

1995年,IBM公司的Raj N.Master团队研发出一种基于陶瓷基板的倒装芯片级封装(CSP),将其命名为MiniBGA。这款封装采用C4焊料倒装技术,基板选用氧化铝陶瓷材质,外形为边长21毫米的方形结构,共包含1521个输入/输出接口(呈39×39阵列分布)。其外引脚采用铅锡共晶焊球,单个焊球尺寸为0.250毫米,焊球间距设定为0.5毫米。

1995年,日本东芝公司推出了一款陶瓷基板薄型封装(Ceramic Substrate Thin Package,简称CSTP)。该封装归为LGA(触点阵列封装)类型,主要组成部分包括LSI芯片、氧化铝(或氮化铝)基板、金凸点以及树脂等。封装过程采用倒装焊接与底部填充工艺,完成后通过印刷焊料的方式贴装到印刷线路板(PWB)上。CSTP的整体厚度仅为0.5~0.6毫米,其中LSI芯片厚度0.3毫米,基板厚度0.2毫米,仅为传统薄型小外形封装(TSOP)厚度的一半。值得注意的是,15毫米规格的CSTP封装效率(芯片与基板的面积比)超过75%,而同等尺寸的薄型四方扁平封装(TQFP)封装效率则不到30%。

1999年,Minehiro Itagaki等人开发出一种基于塑料基板的触点阵列(LGA)型芯片级封装(CSP)。该封装的芯片配备再布线层,能够将输入/输出电极引导至倒装焊盘,且倒装焊盘上设有金钉头凸点(SBB);基板采用名为ALIVH的多层有机基板,芯片焊区的金钉头凸点通过引线钉头凸点法制作而成。在倒装键合(FCB)过程中,先在印刷电路板(PCB)或其他基板的焊区印制导电胶,再将芯片凸点对准并适当加压,待导电胶固化后完成芯片与基板的互连,随后采用环氧树脂进行底部填充。这种封装设计中,导电胶可缓解芯片与塑料基板因热膨胀系数差异较大产生的应力,且塑料基板与印刷线路板(PWB)的热膨胀系数更为匹配,因此具备较好的可靠性。

2. 引线键合类型

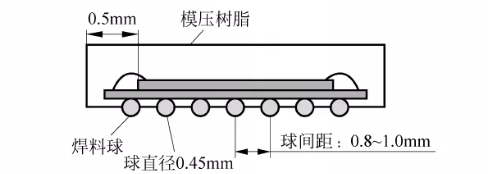

引线键合类型的刚性基板式CSP多采用塑料封装阵列引脚形式,如塑料基板BGA型、LGA型等。其工艺与传统BGA或LGA类似,主要差异在于:焊线采用CSP线弧焊线,且尽可能缩小焊线节距;芯片边缘与封装边缘的距离较小,甚至小于0.5mm;外引脚焊球尺寸相对较小,焊球或触点节距通常小于0.8mm;封装厚度较薄。

采用引线键合的树脂基片CSP产品典型结构如图,其中模压树脂边缘与芯片边缘距离为0.5mm,焊料球直径0.45mm,球间距0.8~1.0mm。

挠性基板式CSP

挠性基板式CSP的封装结构采用弹性材料与聚酰亚胺薄膜组合,可吸收不同材料因热膨胀系数不一致产生的应力及弯曲形变。根据芯片焊盘与基板的互连方式,可分为引线键合、凸点倒装、通孔金属化连接、载带键合等类型。

1. 引线键合类型

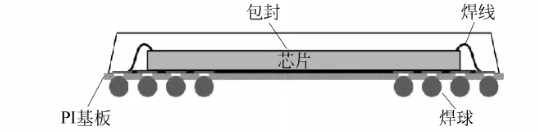

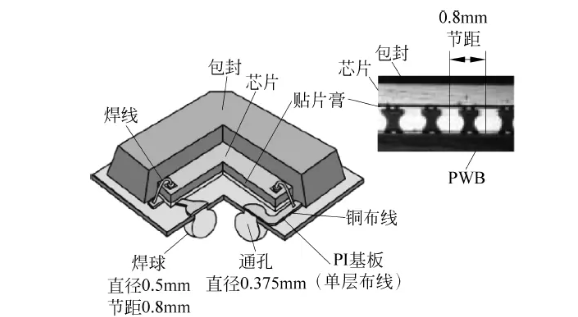

富士通公司的FBGA封装、德州仪器(TI)公司的MicroStar CSP封装均属于引线键合类型的挠性基板CSP。

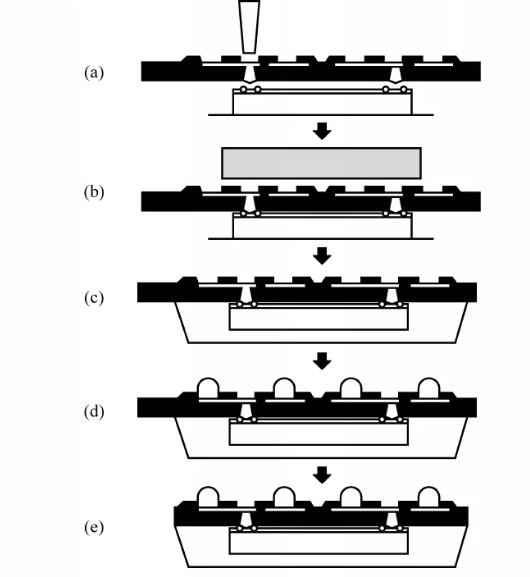

以MicroStar BGA为例,其封装流程如下:①准备挠性基板(通常以PI为主体),上表面设有铜布线图形及焊线区,下表面开孔露出铜布线层;②将芯片电路面朝上进行贴装;③完成引线键合;④进行塑封;⑤涂覆助焊剂后植球并回流;⑥切割分单;⑦开展测试、打标、包装等环节。

2. 凸点倒装类型

日本电气(NEC)公司的小节距BGA(FPBGA)和日东电工(NITTO DENKO)公司的MCSP均属于凸点倒装类型的CSP。其中,FPBGA采用通孔凸点与专用倒装焊接头,MCSP采用金凸点热压焊接。

FPBGA由NEC公司开发,主要由LSI芯片、载带、黏结层及金属凸点组成,凸点节距为0.5~1mm。其工艺特点是采用通孔键合,无焊线线弧及TAB引线弯曲,减少了焊盘间布线,因此能缩小封装尺寸与焊盘节距,更易实现芯片级尺寸。

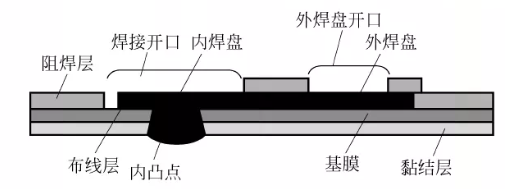

FPBGA的载带结构包括树脂基膜、芯片下方用于黏结芯片的黏结层、穿过基膜与黏结层连接芯片焊盘的内凸点、基膜另一侧用于转移焊盘的布线层、阻焊层(阻焊层在内焊盘处开有通孔焊接用的焊接开口,及外引脚连接用的外焊盘开口)。

FPBGA的工艺流程与TAB(载带自动键合)一样采用卷对卷方式,具体步骤为:①内引脚焊点焊接;②层压——在热压作用下,黏结层黏结并覆盖芯片有源区域,增强互连强度;③模塑;④在外引脚焊盘涂覆助焊剂、植球并回流,完成外引脚凸点制备;⑤边缘切割。

3. 通孔金属化连接类型

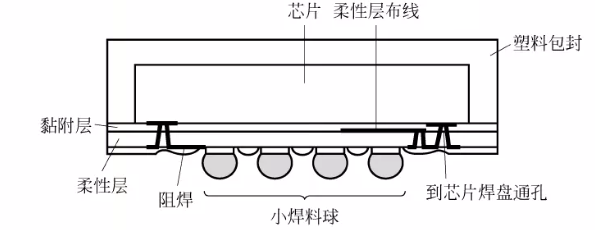

通孔金属化连接的典型代表是COF CSP(Chip-on-Flex CSP),由GE公司开发,是一种基于柔性薄膜的CSP技术。其结构主要包括柔性层及上面的布线、用于黏结芯片的黏附层、芯片、塑料包封、阻焊层、小焊料球及金属焊盘。其工艺特点是柔性层内部有通孔,且柔性层焊球一侧的布线与芯片焊盘通过通孔连接,封装边缘到芯片边缘的最小距离为0.25mm。

COF CSP的工艺与TAB不同,不采用卷对卷方式,而是用边框或载体固定柔性薄膜后再进行后续流程。柔性薄膜为25μm厚的聚酰亚胺,其一面或双面设有4~8μm厚的金属图案,形成布线与焊盘。具体工艺流程为:①在柔性薄膜表面喷涂或旋涂10~15μm厚的热塑性黏附层,将芯片有源面朝向柔性薄膜贴装,通过热压实现键合;②模塑;③用激光在芯片、金属1、金属2处刻出通孔,通过溅射与电镀实现孔金属化;④在表面施加阻焊并开口,定义输入/输出端口;⑤用0.15~0.2mm厚的钢网印刷焊膏,回流后形成焊球(焊球直径0.25~0.3mm,高度0.15~0.18mm);⑥切割形成单个封装。

4. 载带键合类型

载带键合类型CSP的典型是Tessera公司开发的Micro BGA(μBGA),一种柔性载带CSP,应用广泛。

这种CSP采用类似TAB工艺中的聚酰亚胺-铜挠性基板制作,载带的图形化与铜布线预先完成,后续整体工艺主要包括以下步骤:

(1)载带预处理——将载带(多采用聚酰亚胺材质)的一面朝上,利用钢网印刷工艺在芯片贴合区域制作出低模量弹性小块;其中,聚酰亚胺载带、弹性小块以及后续的低模量封装材料,能有效缓冲芯片与印刷线路板(PWB)因热膨胀系数差异引发的应力。

(2)芯片贴装——在弹性小块表面喷涂液态胶粘剂,将芯片贴合到位后,于150摄氏度环境下烘烤3分钟以完成胶粘剂固化。

(3)内引脚键合——借助专门设计的键合装置,在预设位置通过热压焊接方式将内引脚与芯片的铝焊盘(PAD)连接固定。

(4)包封——使用上下两层临时保护膜覆盖已完成芯片与引脚连接的载带,通过压力辅助注射工艺将液态树脂注入覆盖区域,待树脂完全裹覆后,通过分段升温的方式使其固化,形成弹性封装保护层。

(5)焊球植装——采用丝网印刷工艺在外引脚焊盘上涂抹20微米厚的助焊剂,随后放置直径约300微米的焊球,经回流焊接后使焊球与焊盘形成稳固连接。

(6)电学性能测试与激光打标。

(7)切单、检验与封装——测试完成后,将条带上的所有封装单元切割分离为单体,经再次检验合格后进行最终封装。

晶圆级CSP

晶圆级CSP(Wafer-Level Chip Scale Package,WLCSP)是在晶圆前道工序完成后,直接利用半导体工艺对晶圆进行后道封装,再切割分离为单个器件。其芯片面积与封装面积之比达100%。

按照芯片焊盘与封装外引脚的连接方式,WLCSP可初步分为四类:(1)芯片焊区上凸点(Bump On Pad,BOP)WLP;(2)电极再分布(Redistribution Layer,RDL)WLP;(3)包封式WLP;(4)柔性载带WLP。

基于EMC包封的CSP

除上述四类外,还有一些不同结构的CSP,此处介绍两种基于EMC(环氧模塑料)包封的类型——芯片焊盘与外部引脚的凸点通过包封或穿过包封实现连接。

1. 薄树脂包封的CSP

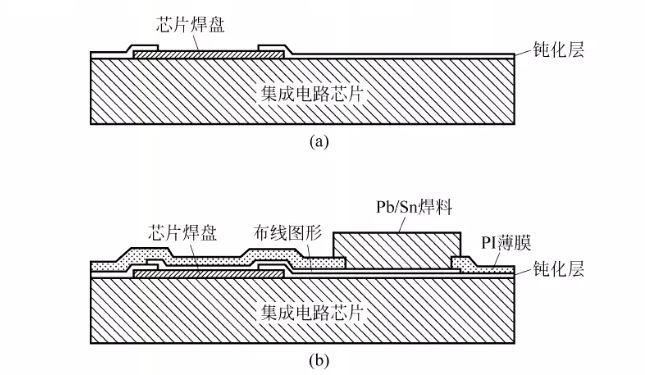

1995年,三菱电机公司的Masatoshi Yasunaga等人报道了一种薄树脂包封的CSP,主要由IC芯片、薄树脂包封层及外电极焊料凸点组成。

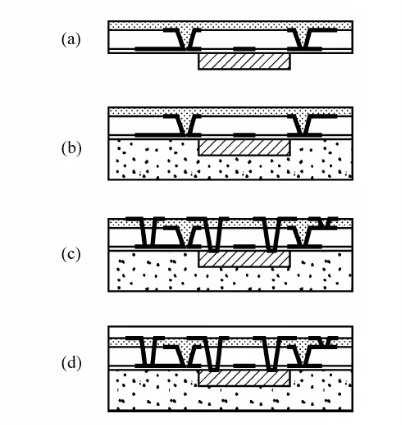

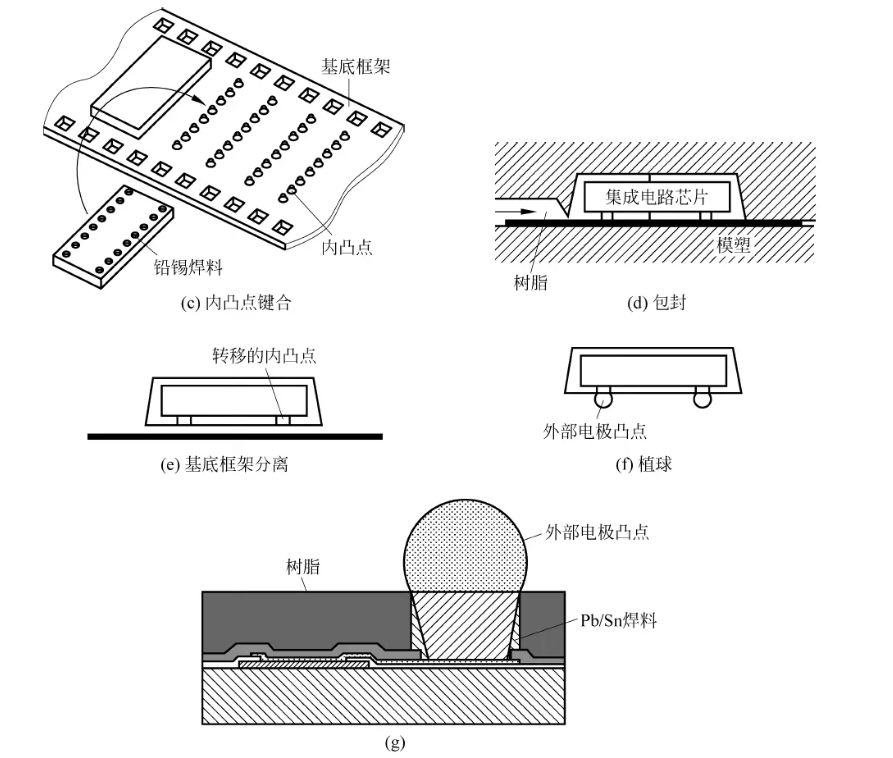

具体工艺过程为:①芯片工艺完成后,晶圆表面为焊盘与钝化层;②在芯片上制作金属再布线层,通过7μm厚的P钝化及蒸发剥离形成共40μm厚的Pb/Sn焊料金属层,减薄并切割芯片;③将芯片转移到带有内凸点的不锈钢基底框架上(内凸点主体为100μm厚的Cu,表面闪镀NiAu);④不锈钢基底框架带着芯片一起模塑成型;⑤模塑完成后,基底框架与芯片分离,内凸点转移到封装上;⑥在内凸点上涂覆助焊剂、植球并回流,完成焊料球外引脚安装,形成完整封装,最后进行测试、打标与包装;⑦形成的凸点截面如图g所示。

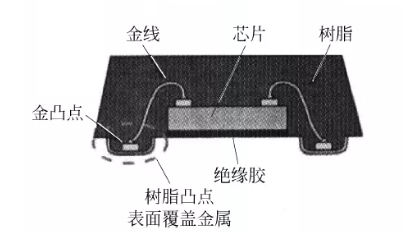

2. BCC CSP

1996年,富士通公司的J.Kasai等人报道了一种凸点式片式载体(Bump Chip Carrier,BCC)CSP封装,主要包含金线、芯片、树脂、金凸点、绝缘胶及表面覆盖金属的树脂凸点。

BCC CSP的具体工艺流程为:①通过半蚀刻处理在铜合金引线框架材料上形成凹坑,并在凹坑上镀PdNiPdAu金属膜;②将芯片键合到引线框架上,通过引线键合连接芯片焊盘与引线框架凹坑上的镀层;③腐蚀去除铜合金引线框架,形成单个封装。

-

芯片

+关注

关注

460文章

52568浏览量

441888 -

封装

+关注

关注

128文章

8717浏览量

145634 -

CSP

+关注

关注

0文章

128浏览量

28802 -

倒装芯片

+关注

关注

1文章

108浏览量

16622

原文标题:CSP基本类型与工艺

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

BGA和CSP封装技术详解

芯片封装测试流程详解ppt

可以解决众多封装难题的CSP-ASIP

TVS新型封装CSP

倒装芯片CSP封装

电子元器件的常见封装 各种封装类型的特点介绍

先进的CSP封装工艺的主要流程是什么

详解芯片尺寸封装(CSP)类型

瑞沃微:一文详解CSP(Chip Scale Package)芯片级封装工艺

详解CSP封装的类型与工艺

详解CSP封装的类型与工艺

评论