TJ375已经支持PLL的动态配置。打开PLL在Advance Settings中的Dynamic Reconfiguration中勾选Enable就可以了。最大可以支持85组配置参数。动态配置框图如下:

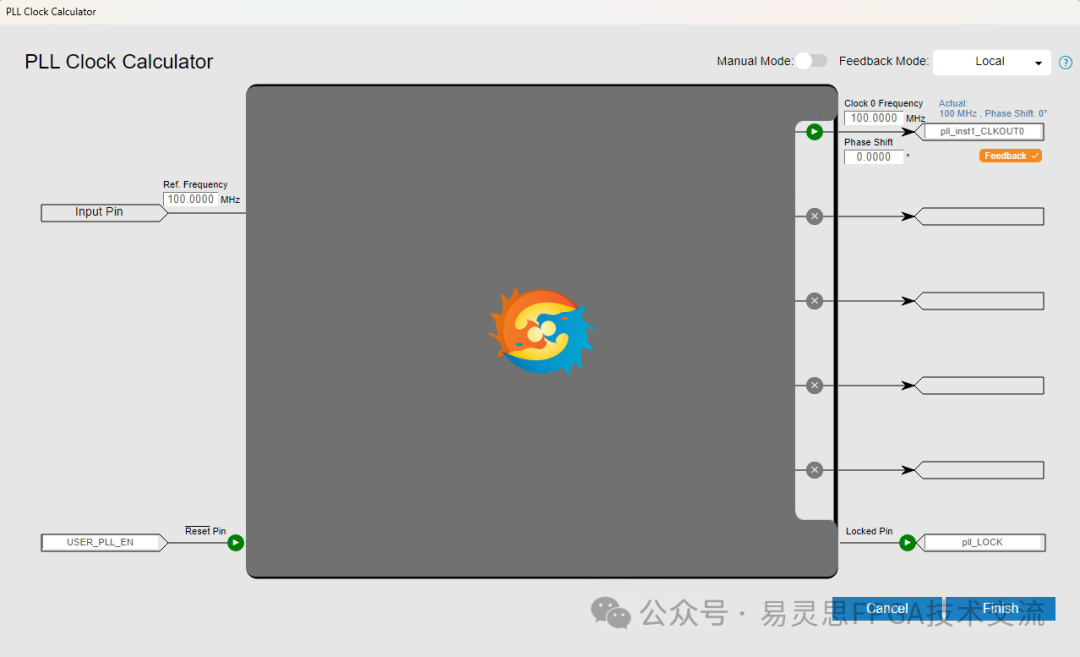

(1)在interface中打开动态配置功能

使用PLL动态配置功能需要打开PLL的reset和lock信号,

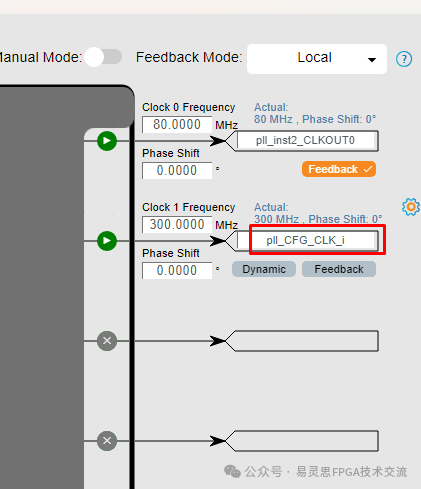

需要两个时钟,pll_cfg_clk_i 和 pll_cfg_clk, pll_cfg_clk_i是一个输入时钟,pll_cfg_clk是动态配置的输出时钟,

通过另一个PLL产生一个pll_CFG_CLK_i

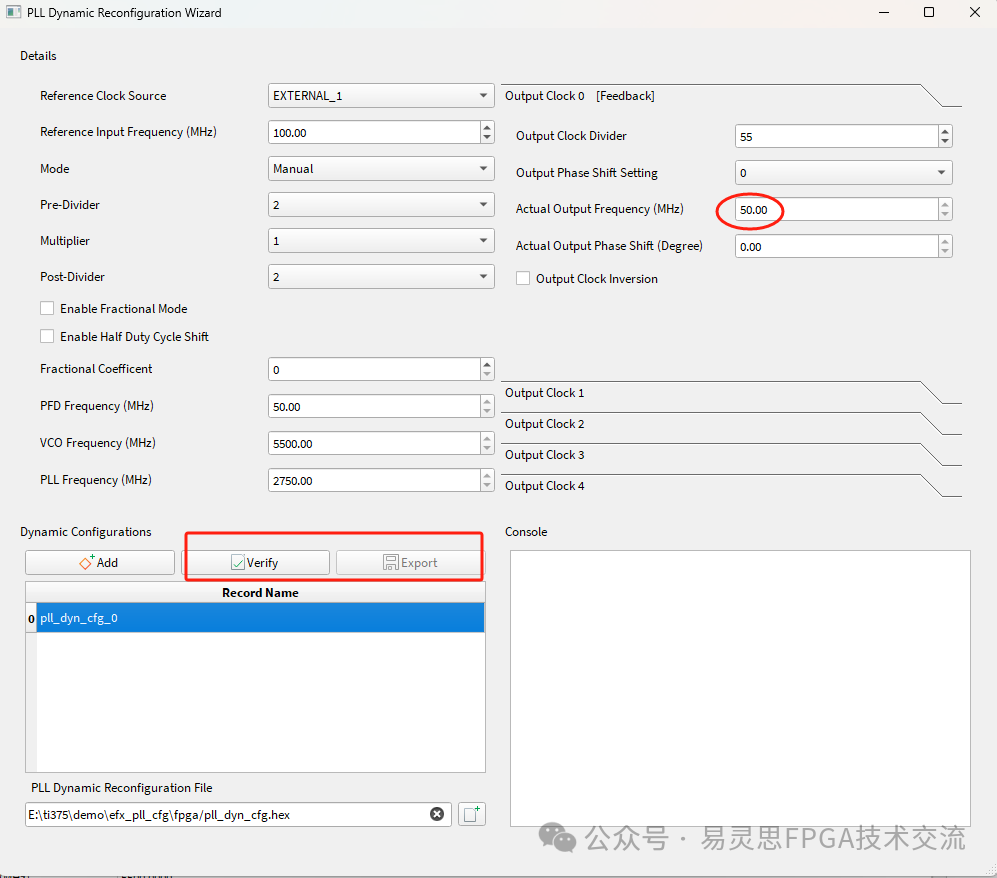

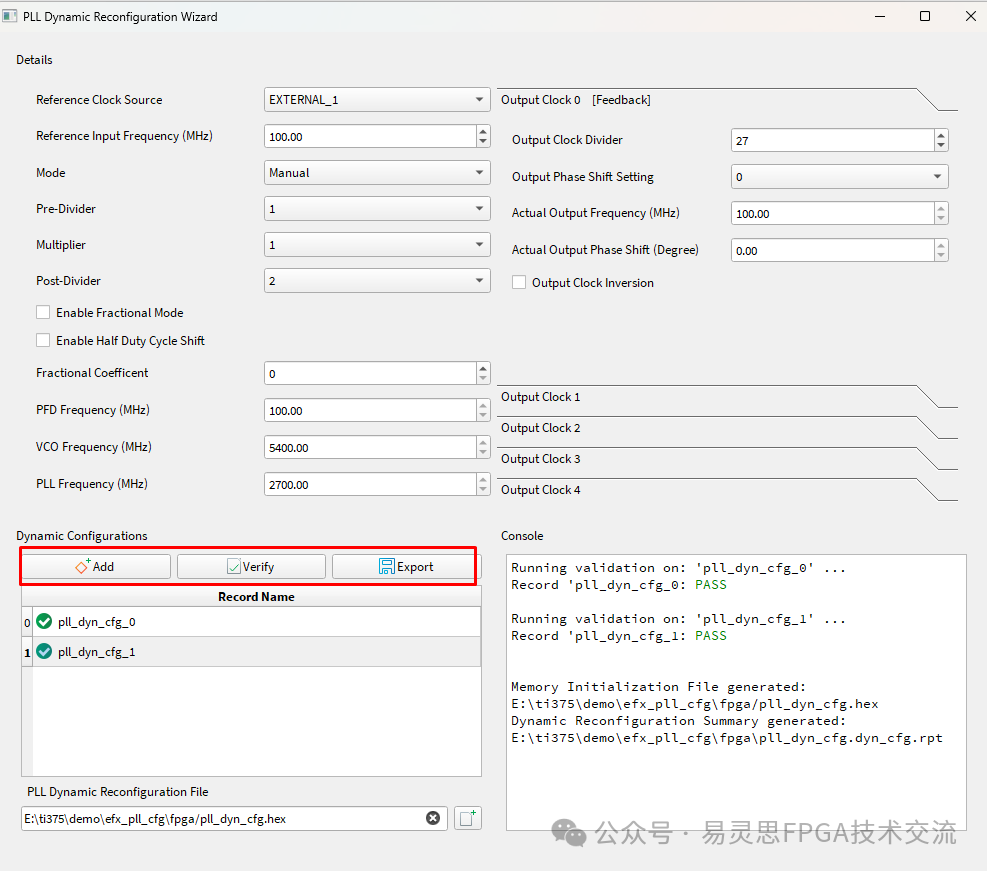

在生成动态配置IP之前要先配置PLL的hex

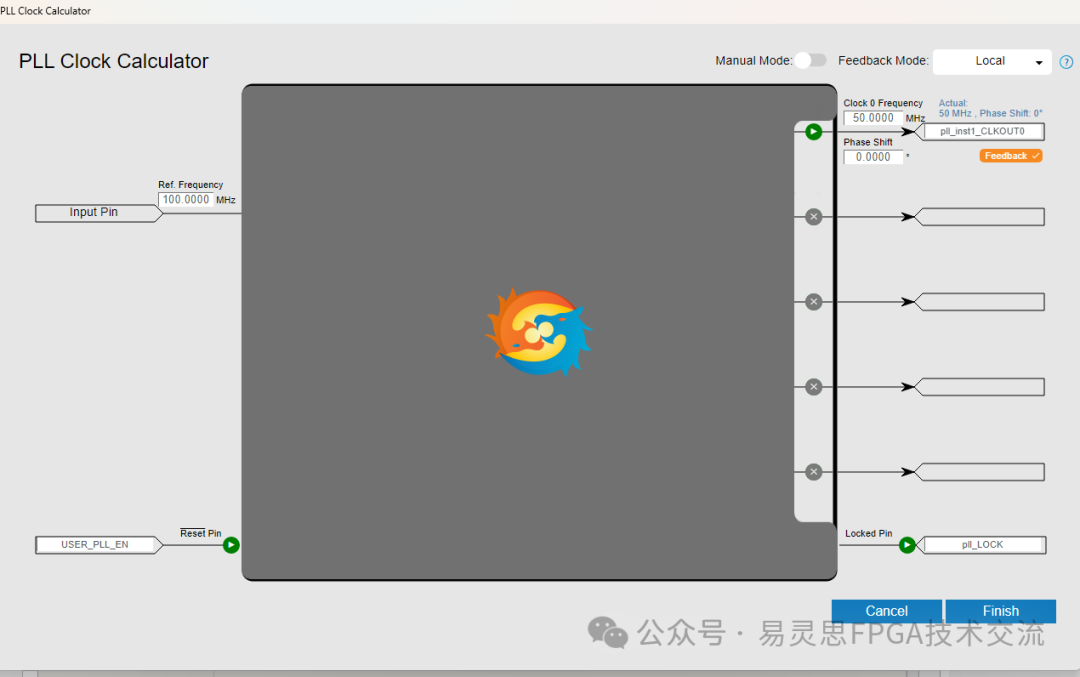

step1:把PLL配置成50M

(2)添加配置参数。点击 Reconfiguration Wizard就可以看到该组参数的配置,点击verify确认参数是否正常;再点击Export生成相应的参数到hex文件;

把PLL的输出修改成100M输出。

再次点击 Reconfiguration Wizard就可以看到该组参数的配置,点击verify确认参数是否正常;再点击Export生成相应的参数到hex文件;

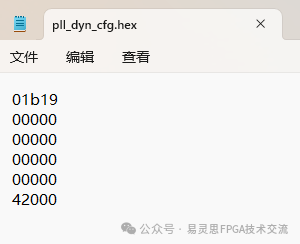

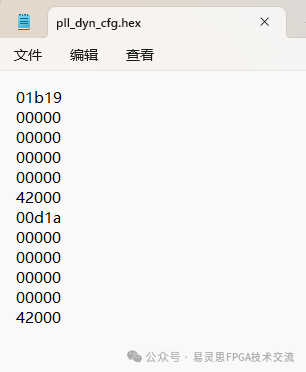

从生成的hex文件可以看到数据有所增加,说明有两个组配置参数。

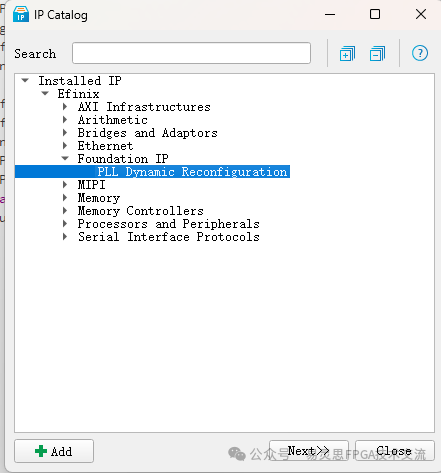

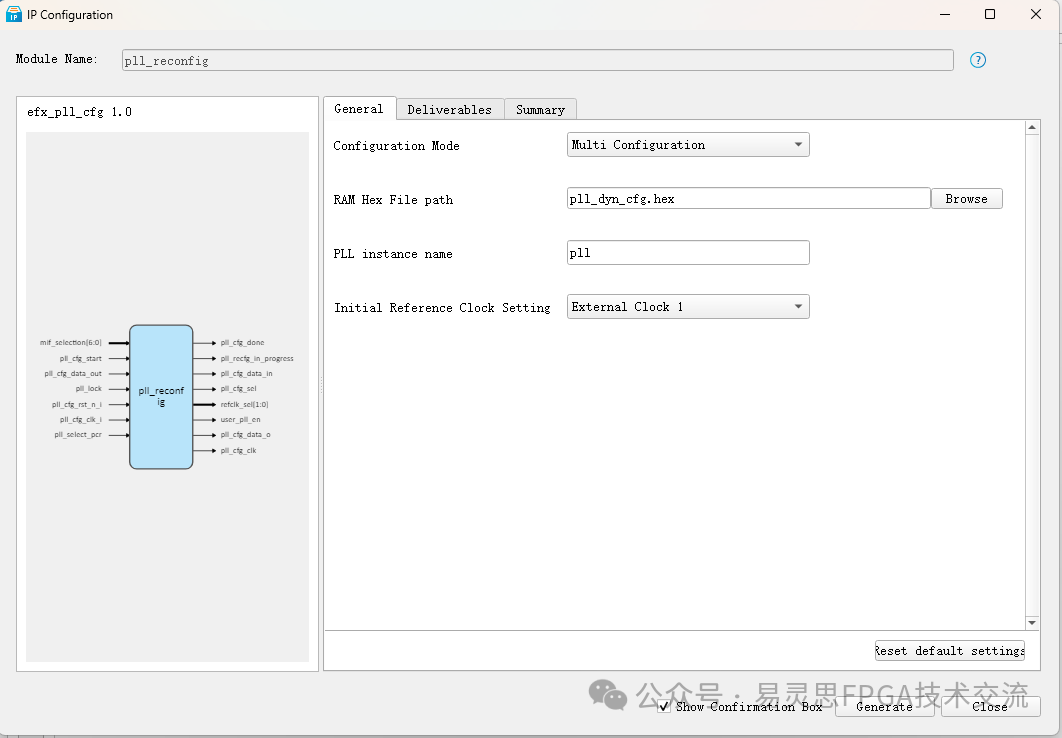

(3)添加IP.在interface里面设置完成之后就可以添加IP了

RAM Hex file path就是之前生成的hex文件的路径;

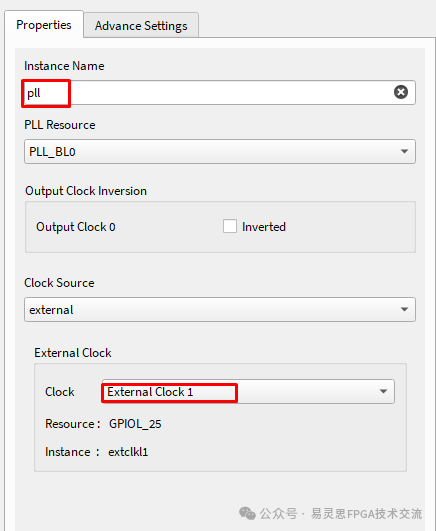

PLL instance name就是我们在interface中例化的PLL的名字;

Initial Reference clock Setting :PLL的参考时钟的源,要对于interface中例化的PLL的参考源。再来看下PLL的配置就更清楚了。

IP 端口说明

| port | I/O | clock Domain | |

| user_pll_en | O | 连接PLL的复位信号 | |

| pll_cfg_clk | O | 动态配置时钟,要与interface内部输入的时钟名一致,25 - 150MHz,应该是pll_cfg_clk_i的二分频生成时钟 | |

| pll_cfg_clk_i | I | 50 - 300MHz | |

| pll_cfg_rst_n_i | 复位PLL动态配置。只有pll_recfg_in_progress为低时才允许断言。 | ||

| pll_select_pcr | I | pll_cfg_clk_i | 把PLL切回PCR设置。 |

| pll_cfg_start | I | pll_cfg_clk_i | 拉高该信号启动PLL动态配置。实测一个时钟周期即可。 |

PCR: Peripheral Configuration Register PLL在interface中设置的初始值 。可以通过把pll_select_pcr拉高来恢复到初始值

-

FPGA

+关注

关注

1646文章

22059浏览量

619193 -

易灵思

+关注

关注

5文章

57浏览量

5232

发布评论请先 登录

易灵思与南京大学集成电路学院暑期课程圆满结课

PLL技术在FPGA中的动态调频与展频功能应用

易灵思邀您相约2025上海国际汽车工业展览会

易灵思2025 FPGA技术研讨会北京站圆满结束

国产EDA亿灵思?接入DeepSeek

赛灵思低温失效的原因,有没有别的方法或者一些见解?

易灵思FPGA PS配置模式--v7

config37中根据DACCLK配置jesd clock,请问下jesd clock大小是跟之前配的serdes pll配置的line rate成40倍关系的吗?

易灵思FPGA产品的主要特点

紫光同创——PLL IP 的使用(Logos2)

MOSFET器件参数:TJ、TA、TC到底讲啥

易灵思 FPGA TJ375的PLL的动态配置

易灵思 FPGA TJ375的PLL的动态配置

评论