一、SiP 封装的诞生:技术瓶颈与市场需求的双重驱动?

SiP(系统级封装)的诞生并非偶然,而是半导体行业在技术极限与市场需求碰撞下的必然选择,其背后是“性能突围”与“场景适配”的双重逻辑。?

从技术背景看,以 SoC(片上系统)为代表的“单片集成”路径遭遇瓶颈:一方面,摩尔定律放缓,7nm以下制程成本呈指数级增长(3nm制程研发费用超50亿美元),单纯通过缩小晶体管提升性能的边际效益递减;另一方面,异构集成需求凸显 ——消费电子、汽车电子等场景需要将 CPU、射频、传感器等不同工艺(如 CMOS、GaN)、不同代际的芯片集成,而SoC受限于单一晶圆工艺,无法兼容异构元件。?

从市场背景看,终端产品对“小型化、低功耗、快响应”的需求倒逼封装技术革新:2010年后,智能手机进入“全面屏”竞赛,要求芯片体积缩减30%以上;新能源汽车的智能驾驶系统需要集成77GHz射频与信号处理,传统分立封装的信号延迟与空间占用难以满足;工业物联网设备则要求在方寸之间实现“感知-计算-通信”一体化,这些场景都指向“多芯片协同工作”的系统级解决方案。?

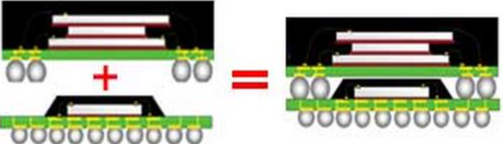

在这样的背景下,SiP通过“封装层面的系统集成 突破限制:无需将所有功能集成在单一芯片上,而是通过先进封装工艺将多个芯片、无源元件(电阻、电容)甚至光学、射频器件集成在同一封装体内,实现“系统级功能”。这种“空间换性能” 的思路,让SiP成为SoC的重要补充。?

二、SiP 封装的发展阶段:从“简单堆叠”到“异构融合”?

SiP 的发展可分为四个阶段,每个阶段的技术特征与焊料需求高度绑定:?

1. 雏形期(2000-2010 年):多芯片模块(MCM)的升级?

核心特征:以“2D 平面集成”为主,将同类型芯片(如CPU + 内存)通过引线键合或基板互连,封装体积仍较大(通常>100mm?)。典型应用是早期智能手机的基带芯片(如高通 MSM 系列)。?

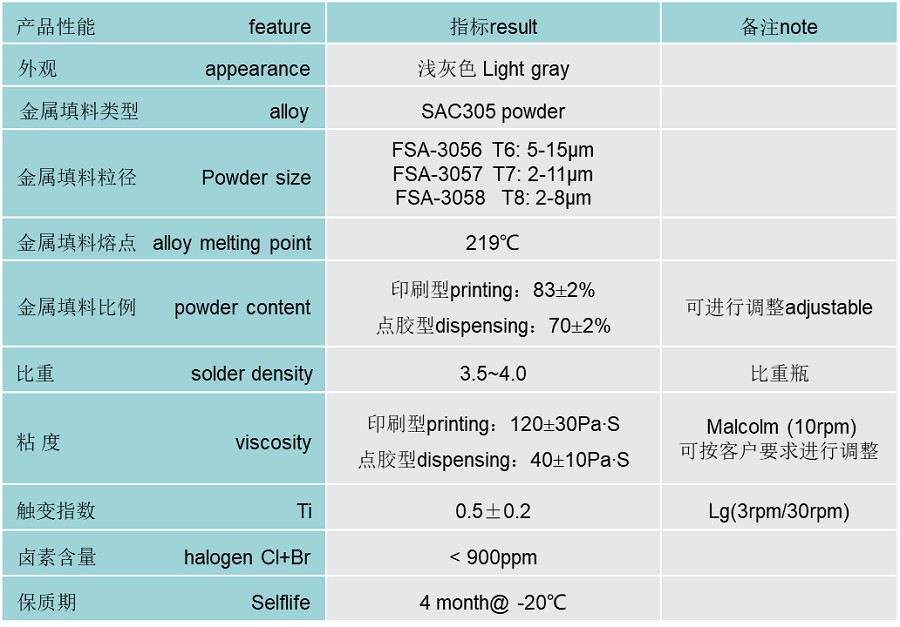

技术局限:互连密度低(I/O 数量<1000),信号延迟高,依赖传统 PCB 基板。? 焊料需求:2006年前以有铅锡膏(Sn63Pb37)为主,熔点183℃,印刷精度≥100μm;2006年欧盟RoHS指令实施后,无铅焊料(如SAC系列)快速普及,逐步替代有铅产品,侧重“能焊牢 的基础需求。?

2. 成长期(2010-2015 年):扇入/扇出型WLP与倒装芯片结合?

核心特征:引入晶圆级封装(WLP)技术,通过扇入/扇出型工艺扩展I/O 数量(1000-5000),实现芯片与基板的“面阵互连”,苹果A8芯片是典型代表(集成 A8 应用处理器和M8运动协处理器)。?

技术突破:铜柱凸点、重布线层(RDL)开始应用,封装厚度降至1mm以下。?

焊料需求:无铅化成为主流,SAC305(Sn3Ag0.5Cu)锡膏普及,要求“细间距适配”(50-100μm)、低空洞率(≤10%);助焊剂需提升活性,应对铜基焊盘的氧化问题。?

3. 爆发期(2015-2020 年):3D堆叠与异构集成落地?

核心特征:3D堆叠技术成熟,通过TSV(硅通孔)实现芯片垂直互连,I/O数量突破10000,可集成异构元件(如CPU+5G 基带 + 射频前端),华为麒麟990 5G是标杆产品(主流集成 5G 基带的手机芯片之一)。?

技术突破:混合键合(Hybrid Bonding)、嵌入式封装(Embedded Die)出现,支持光子、MEMS等跨领域元件集成。?

焊料需求:超细粉末锡膏(T6/T7 级,粒径5-20μm)成为刚需,适配20-50μm 间距;低熔点锡膏(如 Sn58Bi,熔点 138℃)用于多层堆叠的“阶梯焊接”,避免高温损伤下层芯片;助焊剂需具备“耐多次回流”能力,在200℃以上保持活性。?

4. 成熟期(2020 年至今):Chiplet与超异构集成?

核心特征:以Chiplet为核心的“模块化集成”成为主流,通过标准化接口(如 UCIe)将不同功能的Chiplet(计算、存储、互连)像“乐高积木”一样集成,AMD MI300X、英伟达H100均采用该架构。?

技术突破:间距缩至10μm以下,信号传输速率突破100Gbps,热管理引入液冷、微通道技术。?

焊料需求:微米级锡膏(T8级,粒径 2-8μm)实现10μm以下间距印刷;高频场景下关注焊料的导电性能和焊点信号完整性,减少信号损耗;银胶等导热焊材(热导率≥80W/m?K)解决高密度集成的散热问题。?

三、SiP封装的未来态势:向“全域集成”与“智能感知”进化?

未来 5-10 年,SiP将沿着三个方向突破:?

超异构集成:从“电子元件”扩展到“跨物理域集成”,如将光子芯片(光通信)、量子比特(量子计算)、生物传感器(医疗设备)纳入SiP,要求焊料适配不同材料(硅、玻璃、陶瓷)的表面特性,例如针对光子芯片的玻璃基板,需开发能提升焊料与基板界面反应(如形成金属间化合物)的助焊剂,增强附着力,同时保证焊料对基板的润湿性(接触角≤30°)。?

动态可重构:通过“可重构互连”技术,让SiP内的芯片可按需切换连接方式(如算力分配、功耗调节),这需要焊料具备“低接触电阻”(≤5mΩ)和“高抗疲劳性”(10000 次温度循环无失效),支持动态信号路径切换。?

极致小型化与能效:终端设备(如可穿戴、植入式医疗)要求SiP体积缩至1cm? 以下,功耗降至1mW,推动焊料向“无铅低温合金”(如 Sn-Zn-Bi,熔点 180-190℃)、“纳米复合焊材”(添加石墨烯片等提升导热)发展。

?

四、焊料的“进化史”:从“连接工具”到“性能赋能者”?

SiP 的发展直接推动焊料从“简单连接材料”升级为“系统级性能支撑者”,其进化路径与SiP需求高度耦合:?

粒径微缩:从早期的T3 级(25-45μm)到现在的 T8 级(2-8μm),下一步将突破亚微米级(1-3μm),适配5μm以下间距的Chiplet互连,需解决“粉末氧化”(通过惰性气体保护制造)和“印刷堵网”(优化球形度至≥98%)问题。?

合金体系迭代:从铅基到无铅(SAC系列),再到低熔点(SnBi)、高温稳定(Sn-Ag-Cu-Ni),未来将探索通过优化合金成分比例及添加合适微量元素,让焊点在温度变化时更好地缓解应力,减少开裂风险。?

功能复合化:从单一“焊接功能”到“多功能集成”,例如:?

高频焊料:通过优化合金成分,提升导电性能,减少趋肤效应影响,适配 100Gbps以上信号传输。?

自修复焊料:嵌入微胶囊型助焊剂,当焊点出现微裂纹时,胶囊破裂释放助焊剂,修复氧化层。?

焊点状态监测:通过在封装结构中布置外部传感器(如热电偶、应变片),实时监测焊点温度、应力,为SiP的健康管理提供数据。?

工艺适配性优化:针对SiP的多样化工艺(激光焊、混合键合、热压焊),开发 “工艺定制化焊料”—— 例如激光焊专用锡膏(高耐热助焊剂,在250℃以上不碳化)、混合键合配套助焊剂(支持Cu-Cu直接键合的表面活化)。?

SiP的本质是“用封装创新突破芯片物理极限”,而焊料则是这场创新的“隐形基石”。从智能手机到量子计算机,从可穿戴设备到深空探测器,SiP的每一次突破都伴随着焊料的技术跃升。未来,随着SiP进入“全域集成”时代,焊料将不仅是“连接者”,更会成为“性能定义者”——通过材料创新,为系统级封装的可靠性、能效与功能拓展提供无限可能。

-

SoC芯片

+关注

关注

1文章

647浏览量

35883 -

锡膏

+关注

关注

1文章

950浏览量

17521 -

助焊剂

+关注

关注

3文章

138浏览量

11646 -

晶圆级封装

+关注

关注

5文章

42浏览量

11679 -

sip封装

+关注

关注

4文章

68浏览量

15743

发布评论请先 登录

SiP 封装与锡膏等焊料协同进化之路?

SiP 封装与锡膏等焊料协同进化之路?

评论