结合目前应用需求,以及前面基础分析,确定IP应具有如下特色:

(1) 通用性

前端数据采集系统基于 FPGA 开发。 一方面, 设备类型多, 使用的 FPGA型号各不相同, 需要实现的设计能够在多种类型 FPGA 上的工作; 另一方面, 为了降部署低成本, 需要实现脱离 CPU 的存储控制。 综合考虑以上两方面因素,设计应采用纯逻辑电路的方式实现。

(2) 高性能

前端采集的数据存在连续数据、 零散数据等多种数据量形式。 面临大量零散数据存储请求时, 需要增加 NVMe I/O 队列的数量和深度来保证数据传输性能; 而面临大量连续数据存储请求时, 单队列足以发挥性能。 在这种情况下, 需要尽可能降低功耗,减少运行中的 I/O 队列数量。 因此, 需要实现动态的队列管理功能, 在满足高性能的同时适应不同的应用环境。 具体要求为使用 PCIe3.0 以上接口的高性能固态硬盘的顺序读写数据吞吐量不低于2GB/s, 随机写IOPS不低于500000, 随机写延迟不高于1ms。

(3) 易集成、 易操作

实现的 NVMe 主机控制逻辑和 NVMe 固态硬盘作为存储子系统, 应能够方便的集成到应用环境中, 并提供简易的操作方式实现数据的传输与存储。 因此, 设计需要采用标准化接口, 实现尽可能低的资源占用率, 并具备 DMA 数据传输功能。

基于以上需求, 本IP拟基于 FPGA 的 NVMe over PCIe(NoP) 逻辑进行设计,它具有以下特点:

(1) 支持 NVMe 1.3d 协议、 支持 PCIe 3.0 协议。

(2) 基于 Xilinx PCIe Integration Block 硬核开发。 一方面, 该 PCIE 集成块具有多种版本, 并且适用平台多, 因此 NoP 逻辑加速引擎能够部署在支持 PCIE 集成块的FPGA 开发板上。 另一方面, 直接对接 PCIE 集成块的结构设计具有更高的数据传输性能。

(3) 纯逻辑电路开发。 设计基于纯逻辑电路, 不需要 CPU 的介入, 独立运行,可以节省 CPU 资源, 兼容 SoC 与纯逻辑环境。

(4) 使用 AXI 总线接口。 设计使用标准化的 AXI 总线接口提供系统控制和数据传输功能, 在保证了传输性能的同时, 更容易集成到应用环境中。

(5) 多队列并行管理与动态配置。 支持的最大 I/O 提交队列数量为 16, 支持的最大单 I/O 提交队列深度为 1024, 最大 I/O 提交队列总深度为 1024, 支持运行过程中动态的创建或删除队列。

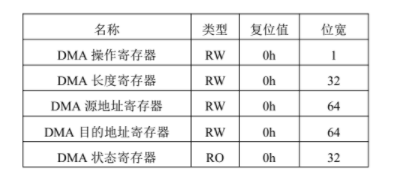

(6) DMA 功能。 通过配置 DMA 寄存器直接请求数据传输, 数据传输通过 AXI4总线接口对接用户逻辑, 使用突发传输提高数据传输性能。

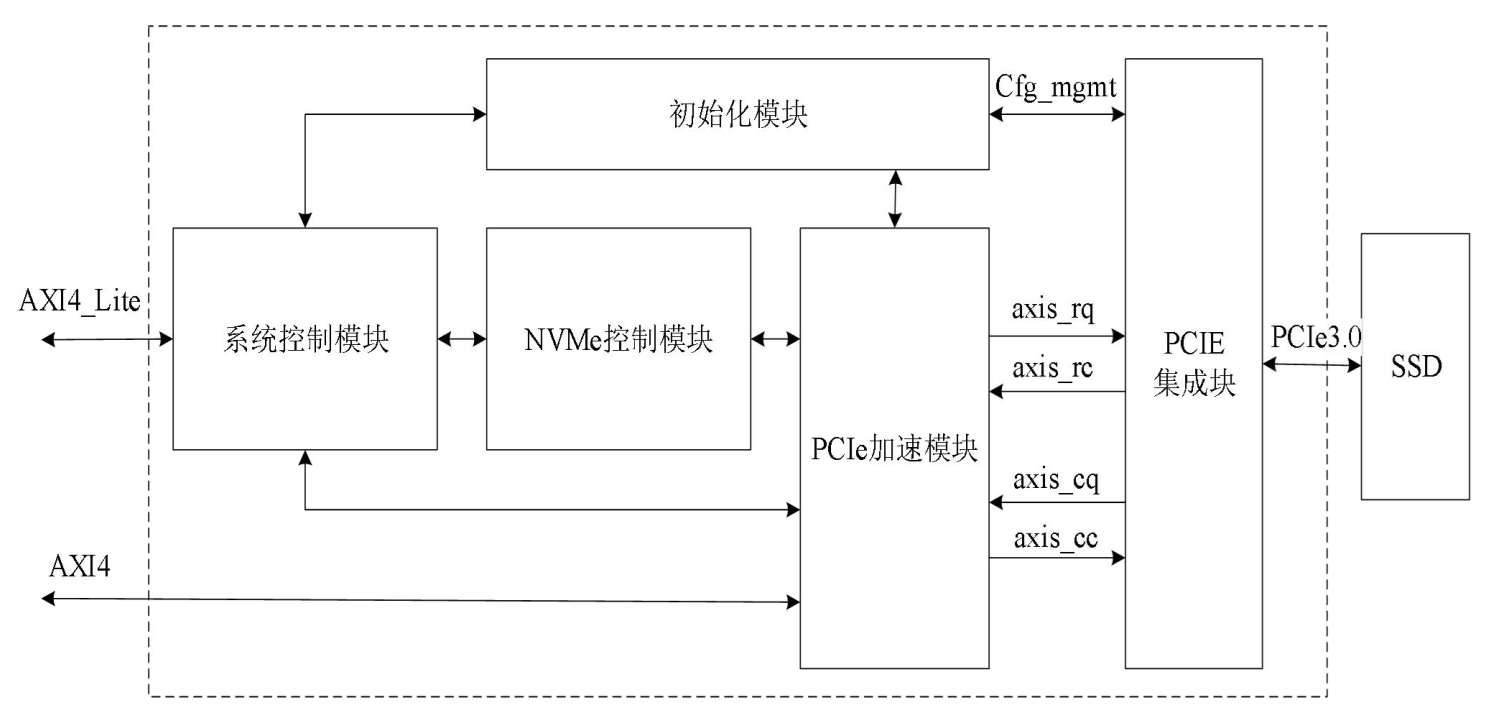

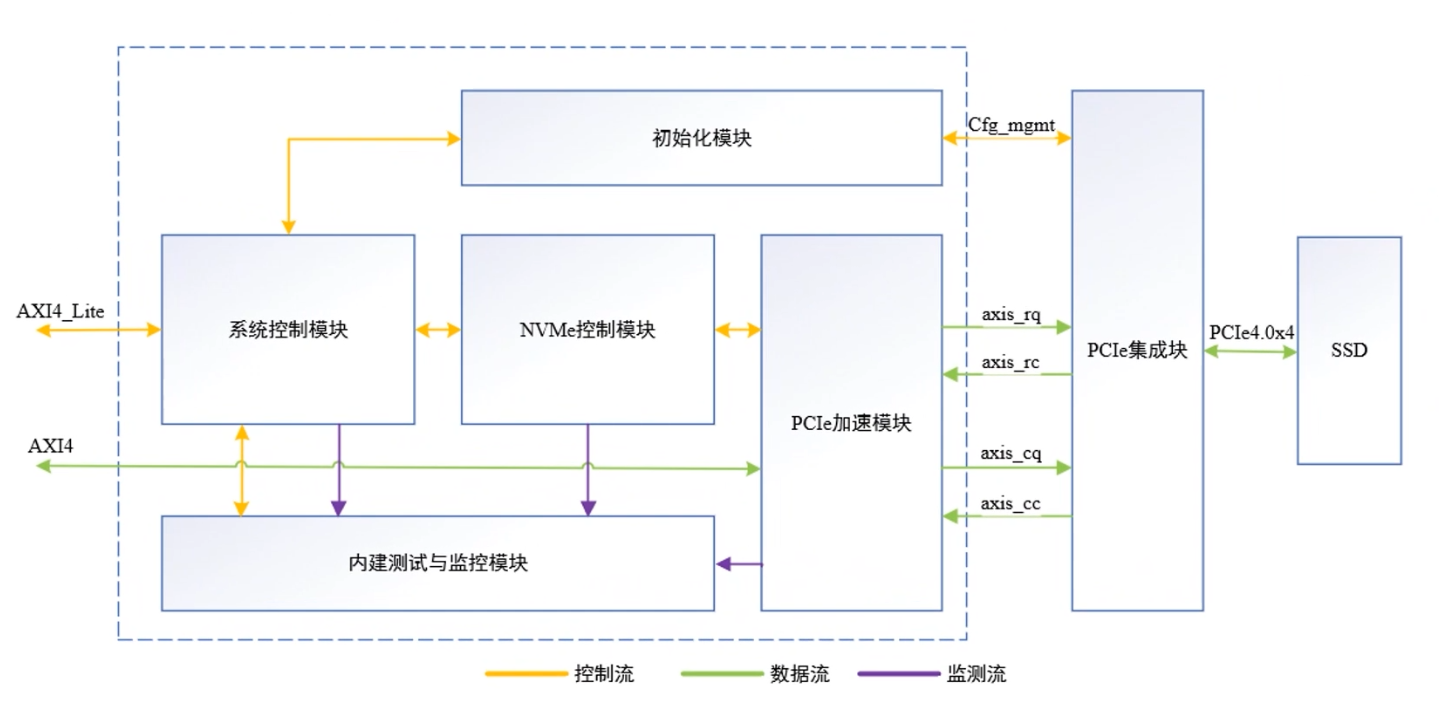

图1 Nvme逻 辑加速IP系统架构图

新系统中,Nvme逻辑加速IP通过 PCIe 3.0x4 接口连接 NVMe

固态硬盘, 并提供 AXI4-Lite 接口用于系统控制, 以及 AXI4 接口用于数据传输。 在该IP内部, 根据功能划分为系统控制模块、 初始化模块、 NVMe 控制模块、 PCIe 加速模块、 PCIE 集成块。 以下为各功能模块的定义:

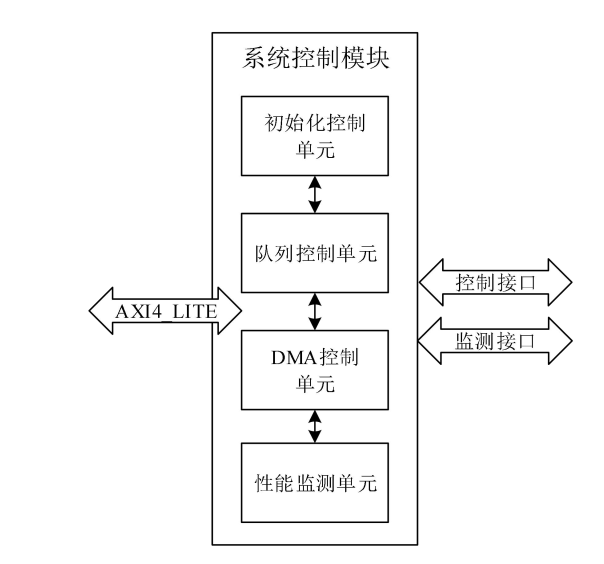

系统控制模块是实现NVMe over PCIe关键组件。 NoP 逻辑加速引擎内部集成了各种功能, 包括初始化、 NVMe 队列管理以及 DMA 等多种功能, 统由系统控制模块进行管理。 为了有效管理这些功能, 系统控制模块设计了对应的功能控制单元, 并提供了 AXI4-Lite 从机接口, 使得 NoP 逻辑加速引擎能够轻松地与用户环境集成。 通过 AXI4-Lite 接口, 用户可以方便地访问各个功能控制单元, 实现对系统功能的控制。 这种设计使得用户能够直接与 NoP 逻辑加速引擎进行交互, 灵活地配置和管理系统的各项功能, 从而更好地满足特定的应用需求。

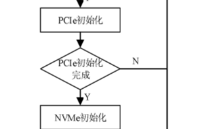

初始化模块负责控制系统的初始化流程, 其中包括 PCIe 初始化和 NVMe 初始化两个主要步骤。 在系统上电复位后, 首先由 PCIE 集成块执行物理层的链路训练和速度协商, 建立有效的 PCIe 通信链路。 随后, 由初始化模块进行 PCIe 设备的枚举与配置, 并执行 NVMe 的初始化流程。 初始化过程是确保系统能够在正确状态下运行的前提条件, 也为后续操作提供了必要的支持。

NVMe 控制模块是实现 NVMe 的命令提交和完成机制的核心模块。 首先, 该模块负责将来自系统控制模块的功能请求转换为 NVMe 命令请求, 并执行 NVMe 指令提交与完成机制。 其次, 该模块实现 NVMe 队列管理功能, 除了基本的队列存储、门铃控制、 请求仲裁、 条目解析等, 还包括了动态创建和删除队列功能。 最后, 该模块还负责实现 PRP 寻址机制, 根据指令管理和计算 PRP 偏移, 实现数据的寻址并降低 PRP 读取延迟。

PCIe 加速模块负责处理 PCIe TLP, 将 PCIe 事务与 NVMe 紧密结合。 一方面,该模块将来自初始化模块或 NVMe 控制模块的事务请求转换为 PCIe TLP 请求, 然后发送到 PCIE 集成块, 同时接收 PCIE 集成块的 TLP 响应包, 将其转换为内部事务响应发送到对应内部模块。 另一方面, 该模块负责处理来自 NVMe 存储设备的 TLP 请求, 根据请求内容将请求转发到 NVMe 控制模块或转换为 AXI4 总线事务, 同时将来自 NVMe 控制模块和 AXI4 总的响应组装为 CplD, 经由 PCIE 集成块发送给 NVMe存储设备。

PCIE 集成块实现 PCIe 的数据链路层和物理层。 PCIE 集成块是 Xilinx 提供的用于 PCIe 的高带宽、 可扩展和灵活的通用 I/O 核, 在 NoP 逻辑加速引擎中使用 PCIE集成块的 RC 模式实现 Root Complex 的数据链路层与物理层。 PCIE 集成块提供了四组 AXI stream 接口用于传递 PCIe TLP, 通过这些接口实现 TLP 与 PCIe 链路信号的相互转换, 此外还包含一组配置接口用于访问 PCIE 集成块的配置空间。

想进一步了解相关视频,请搜索B站用户:专注与守望

链接:https://space.bilibili.com/585132944/dynamic?spm_id_from=333.1365.list.card_title.click

更多博文见:https://blog.csdn.net/tiantianuser/article/details/148994728

-

FPGA

+关注

关注

1646文章

22069浏览量

619711 -

可编程逻辑

+关注

关注

7文章

526浏览量

44816 -

高速存储

+关注

关注

0文章

12浏览量

6021 -

nvme

+关注

关注

0文章

256浏览量

23282

发布评论请先 登录

NVMe IP高速传输却不依赖便利的XDMA设计之三:系统架构

NVMe IP高速传输却不依赖XDMA设计之五:DMA 控制单元设计

NVMe高速传输之摆脱XDMA设计18:UVM验证平台

PHP简单实现不依赖于Unix系统Cron的定时任务程序资料说明

以色列成立新研究中心,开发不依赖GPS的导航系统

智行者发布国内首款不依赖高精地图的高级别自动驾驶解决方案

原生鸿蒙系统正式发布,余承东宣布不依赖国外核心技术

NVMe IP over PCIe 4.0:摆脱XDMA,实现超高速!

NVMe IP高速传输却不依赖XDMA设计之二:PCIe读写逻辑

NVMe IP高速传输却不依赖XDMA设计之四:系统控制模块

NVMe IP高速传输却不依赖XDMA设计之五:DMA 控制单元设计

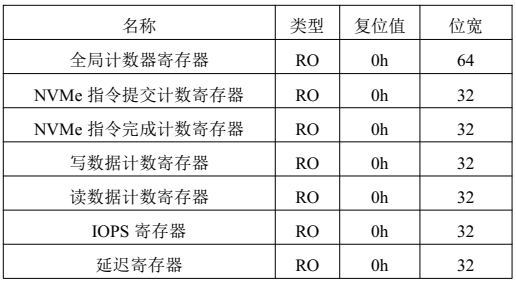

NVMe IP高速传输却不依赖XDMA设计之六:性能监测单元设计

NVMe IP高速传输却不依赖XDMA设计之八:系统初始化

NVMe IP高速传输却不依赖XDMA设计之三:系统架构

NVMe IP高速传输却不依赖XDMA设计之三:系统架构

评论