概述

[ADN4654]/[ADN4655]/ADN4656^1^ 是信号隔离式低电压差分信号 (LVDS) 缓冲器,能够以低抖动在高达 1.1 Gbps 的数据速率下运行。这些器件集成了 ADI 公司的 iCoupler^?^ 技术,已针对高速运行进行增强,可以为符合 TIA/EIA-644-A 标准的 LVDS 驱动器和接收器提供电气隔离。利用该集成,可实现 LVDS 信号链的嵌入式隔离。

ADN4654/ADN4655/ADN4656 包含多种通道配置,ADN4655 和 ADN4656 上的 LVDS 接收器包含一个故障安全机制,可在输入悬空、短路或端接但未驱动时确保相应的 LVDS 驱动器输出为逻辑 1。

对于低抖动条件下的高速运行,LVDS 和隔离器电路依赖于 2.5 V 电源。集成的片内低压差 (LDO) 稳压器可以通过外部 3.3 V 电源提供所需的 2.5 V 电压。这些器件完全适合在广泛的工业温度范围内使用,采用具有 5 kV rms 隔离的 20 引脚宽体 SOIC_W 封装,或采用具有 3.75 kV rms 隔离的 20 引脚 SSOP 封装。

数据表:*附件:ADN4654 ADN4655 ADN4656 5kV RMS 3.75 kV RMS、双通道LVDS千兆位隔离器技术手册.pdf

应用

特性

- 5 kV rms 和 3.75 kV rms LVDS 隔离器

- 符合 TIA/EIA-644-A LVDS 标准

- 多种双通道配置

- 能以高达 1.1 Gbps 的任意数据速率进行切换,具有低抖动

- 传播延迟 4 ns(典型值)

- 随机抖动 2.6 ps rms(典型值)

- 1.1 Gbps 时峰到峰总抖动 90 ps(典型值)

- 2.5 V 或 3.3 V 电源

- ?75 dBc 电源纹波抑制,相位杂散水平

- 抗干扰性

- ±8 kV IEC 61000-4-2 ESD 跨隔离栅保护

- 高共模瞬变抗扰度:>25 kV/μs

- 超越 EN 55022 B 级辐射发射限制,PRBS 为 1.1 Gbps

- 安全和监管审批(20 引脚 SOIC_W 封装)

- UL(申请中):5000 V rms 持续 1 分钟,符合 UL 1577 标准

- CSA 组件验收通知 5A(申请中)

- VDE 符合性证书(申请中)

- DIN V VDE V 0884-10 (VDE V 0884-10):2006-12

- V

IORM= 424 VPEAK

- 在开路、短路和端接输入条件下故障安全输出高电平 (ADN4655/ADN4656)

- 工作温度范围:?40°C 至 +125°C

- 7.8 mm 最小爬电距离和净空

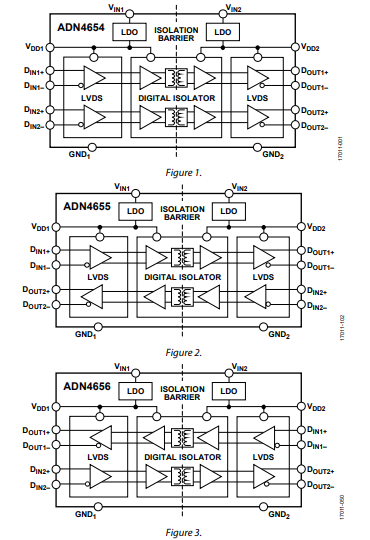

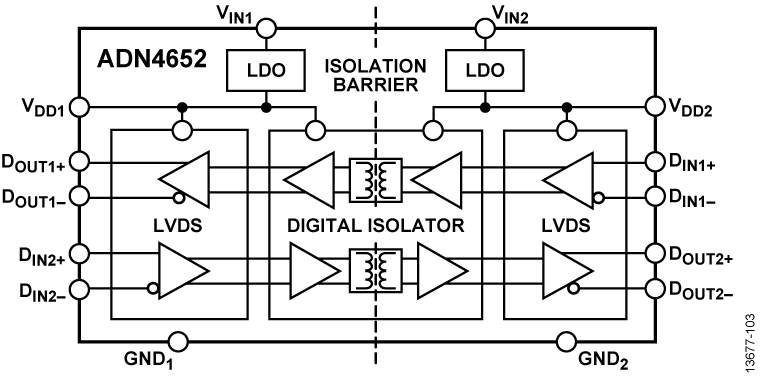

框图

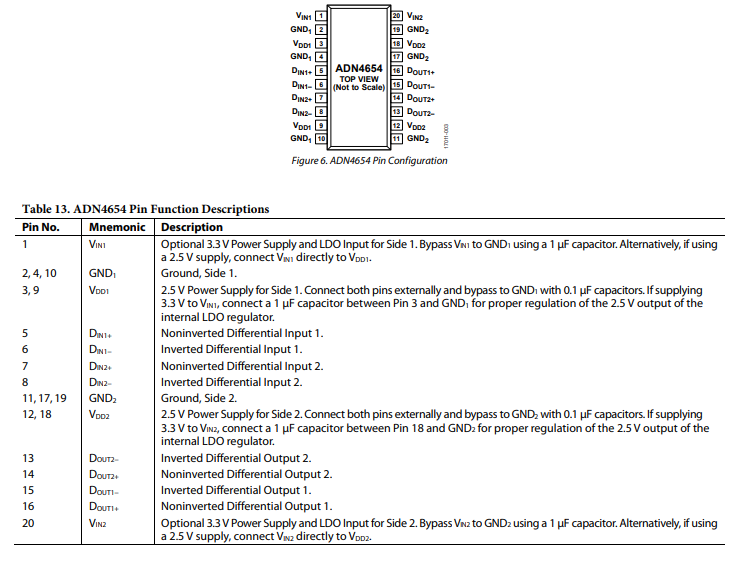

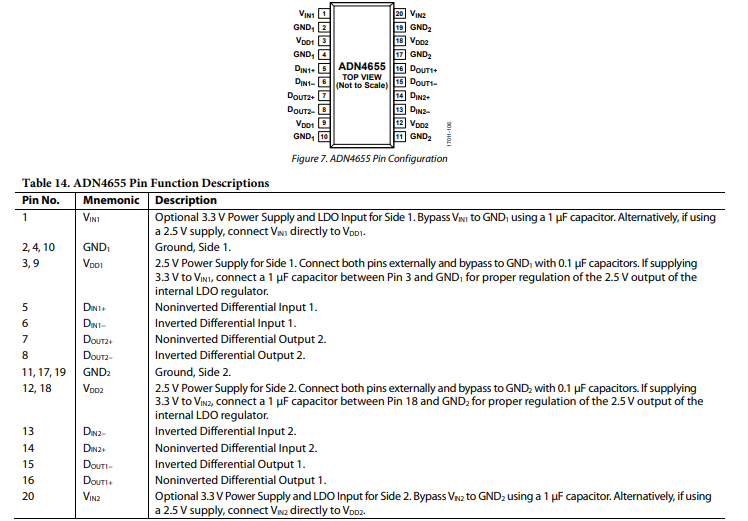

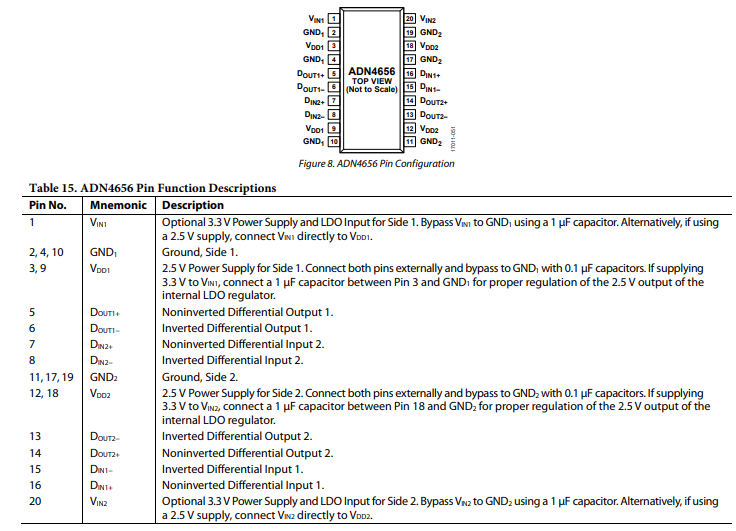

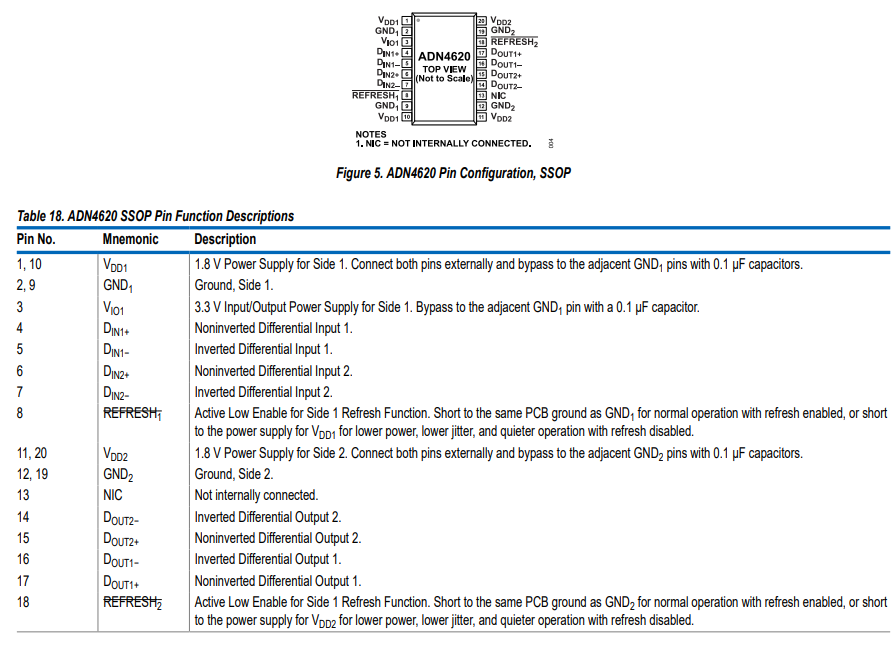

引脚配置描述

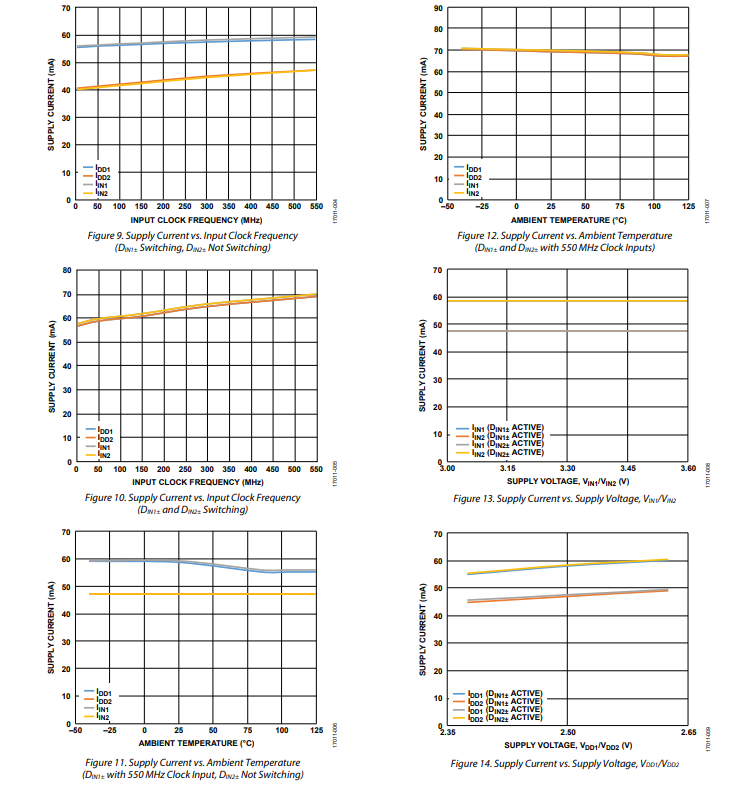

典型性能特征

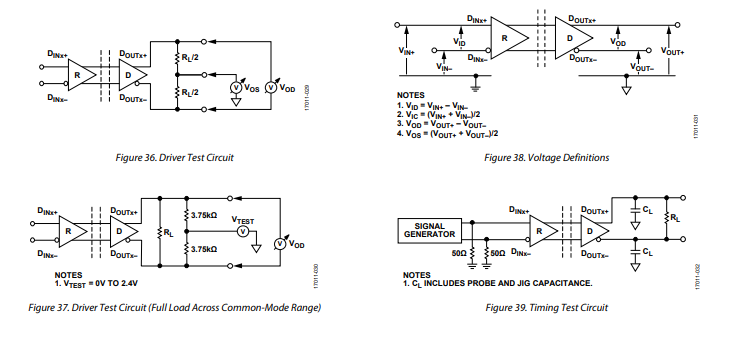

测试电路和开关特性

应用信息

印刷电路板(PCB)布局

ADN4654/ADN4655/ADN4656可以在高达0.55 GHz时钟频率下处理高速低压差分信号(LVDS),并且在零归位(NRZ)数据下可达到1.1 Gbps,可对LVDS走线应用最佳的端接和匹配规范。在尽可能靠近接收器的位置放置100 Ω终端电阻,跨接在(D_{IN+})和(D_{IN-})引脚上。

为确保信号完整性、降低系统抖动并将电磁干扰(EMI)降至最低,LVDS信号线上需要50 Ω的受控阻抗。走线宽度、相邻走线之间的横向距离以及接地层下方的距离都必须适当。通过将PCB接地层之间的过孔对紧密放置,也可以将相邻走线对之间的串扰降至最低。

ADN4654/ADN4655/ADN4656符合EN 55022 B级辐射限制标准,在隔离器以高达1.1 Gbps PRBS数据速率运行时,无需额外考虑。在隔离高速时钟(例如1.05 Gbps)时,可能需要20引脚小外形集成电路(SOIC)_W模型隔离间隙二极管效应,以确保在B级辐射限制标准下有足够的裕量。

在使用ADN4654/ADN4655/ADN4656的应用中,最佳的高速PCB设计可避免PCB产生的其他辐射。配置高速连接时需注意,切换瞬变会出现在高速LVDS信号(尤其是时钟信号)中。可采用共模扼流圈,以减少辐射排放。使用共模磁珠、铁氧体或其他滤波器,或在LVDS连接器处采用合适的屏蔽,以及将电缆屏蔽层或PCB接地连接至地平面。

ADN4654/ADN4655/ADN4656要求(V_{IN})引脚使用100 nF的去耦电容。如果使用集成的LDO稳压器,且电源电压为2.5 V,直接将合适的(V_{IN})引脚连接到电源,并参考图40(以ADN4654为例)。

当使用集成的LDO稳压器时,在(V_{IN})引脚上以及最靠近(V_{OUT})引脚(LDO输出)处需要1 μF的旁路电容,如图41所示。

应用示例

- 模拟前端(AFE)的高速LVDS接口 :处理器间通信,或视频与图像数据可通过ADN4654等隔离器在隔离的电路板之间、板间或电缆接口进行传输。ADN4654提供电气隔离,以及强大的外部端口,其低抖动和高驱动强度允许设备通过短电缆进行通信。高共模抑制能力确保在恶劣环境下的通信完整性,并且隔离功能可防止电磁兼容性(EMC)瞬变,如高达±8 kV的静电放电(ESD)、电快速瞬变(EFT)和浪涌。ADN4654可隔离各种图像协议,包括使用物理层共模抑制(CML)而非LVDS的协议。例如高清多媒体接口(HDMI),其中交流耦合和缓冲以及终端电阻网络用于将CML(用于过渡最小化差分信号,TMDS数据和时钟通道)转换为ADN4654所需的LVDS电平。还可使用其他模拟器件隔离器组件,如ADuM1250/ADuM1251电容隔离器,隔离控制信号和电源(ADuM5020 isoPower集成隔离式直流 - 直流转换器)。这可实现高达720p的分辨率。

- 其他电路 :其他电路可使用ADN4654隔离移动行业处理器接口(MIPI)CSI - 2、DisplayPort和基于LVDS的协议(如FPD - Link)。使用现场可编程门阵列(FPGA)或特定集成电路(ASIC)(如串行器/解串器(SERDES))通过多个ADN4654设备扩展带宽,以支持1080p或4K视频分辨率,为短距离光纤链路提供替代方案。

-

接收器

+关注

关注

15文章

2577浏览量

74185 -

缓冲器

+关注

关注

6文章

2065浏览量

47265 -

lvds

+关注

关注

2文章

1128浏览量

67652

发布评论请先 登录

ADN4654 5 kV RMS 双通道 LVDS 千兆比特隔离器

ADN4652 5 kV/3.75 kV rms、600 Mbps双通道LVDS隔离器

ADN4650/ADN4651/ADN4652: 5 kV RMS、600 Mbps双通道LVDS隔离器

UG-933:评估ADN4650 5 kV rms、600 Mbps LVDS隔离器(SOIC_W)

UG-900:评估ADN4651/ADN4652 5 kV rms、600 Mbps LVDS隔离器(SOIC_W)

ADN4654/ADN4655/ADN4656:5 kV RMS和3.75 kV RMS,双通道LVDS Gigabit Sigabit数据Sheet

UG-第1373:评估ADN4654/ADN4655/ADN4656 5 kV rms双通道LVDS千兆隔离器

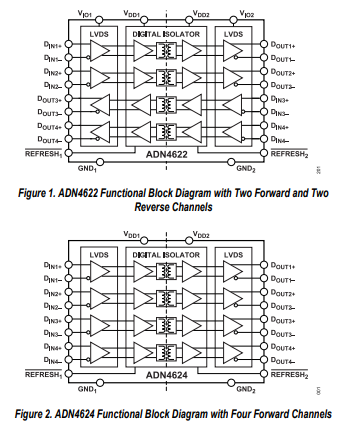

ADN4622/ADN4624 5.7 kV rms/1.5 kV rms、四通道 LVDS 2.5 千兆位隔离器技术手册

ADN4620/ADN4621 7.5 kV RMS/3.75 kV rms双通道LVDS 2.5 Gbps隔离器技术手册

ADN4654/ADN4655/ADN4656 5kV RMS/3.75 kV RMS、双通道LVDS千兆位隔离器技术手册

ADN4654/ADN4655/ADN4656 5kV RMS/3.75 kV RMS、双通道LVDS千兆位隔离器技术手册

评论