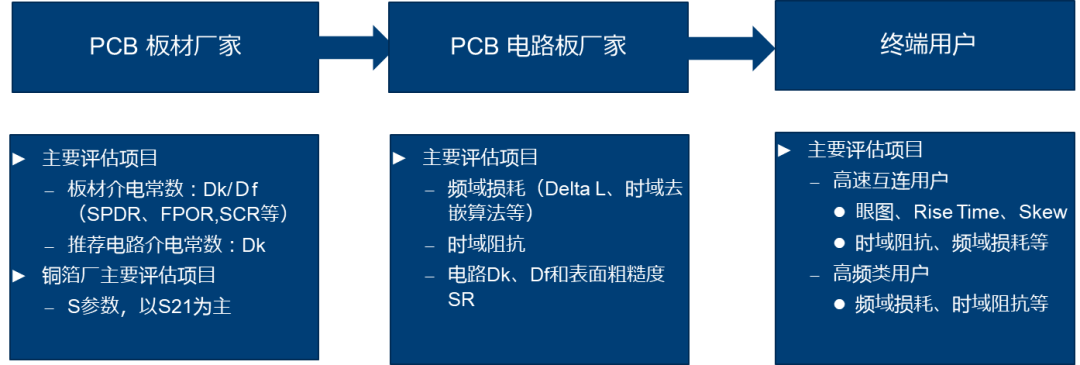

01.测试背景与产业链

高频高速PCB广泛应用于AI、高速通信、数据中心和消费电子等领域。其性能的稳定性和可靠性决定了整个系统的信号完整性和运行效率。高速PCB产业链中的各环节紧密相连,共同确保最终产品的质量。

1上游:材料供应商提供高性能基板材料,这些材料的介电常数(Dk/Df)和铜箔表面粗糙度(SR)等关键参数直接影响了PCB的信号传输性能。

2中游:PCB电路制造商利用上游提供的板材,通过先进的生产工艺制造出多层高频高速电路板,以满足各种复杂的应用需求。

1下游:终端客户将高频高速PCB集成到各种电子设备中,如AI服务器、数据中心、通信设备和智能终端等。

02.高速PCB关键测试指标

PCB测试的主要项目包括频域S参数、时域阻抗、Rise Time、Skew、眼图和材料特性等。这些测试项目可以全面评估PCB的传输性能、阻抗特性、时序特性以及信号完整性等。

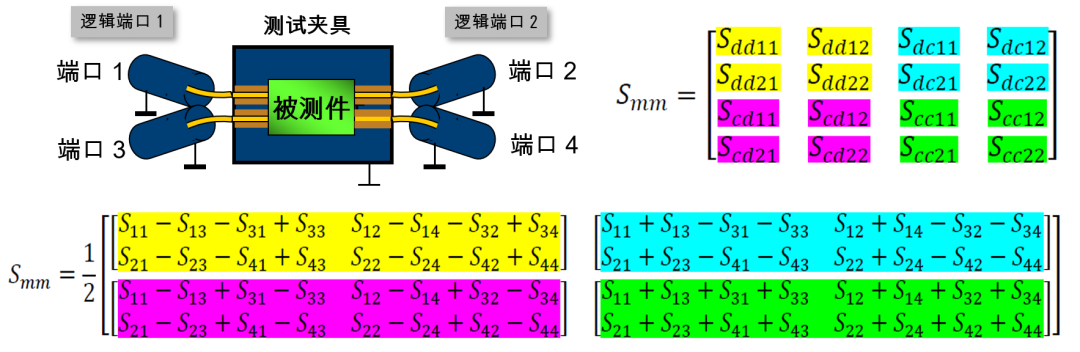

1S参数测试

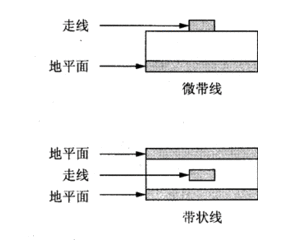

S参数测试是高速PCB的常规测试项目,设计人员可以通过S参数来评估PCB线路的传输和反射性能。高速PCB特别关注插入损耗的性能指标,即Sdd21。Sdd21反映了信号在传输过程中的衰减情况,是评估PCB线路性能的关键指标。

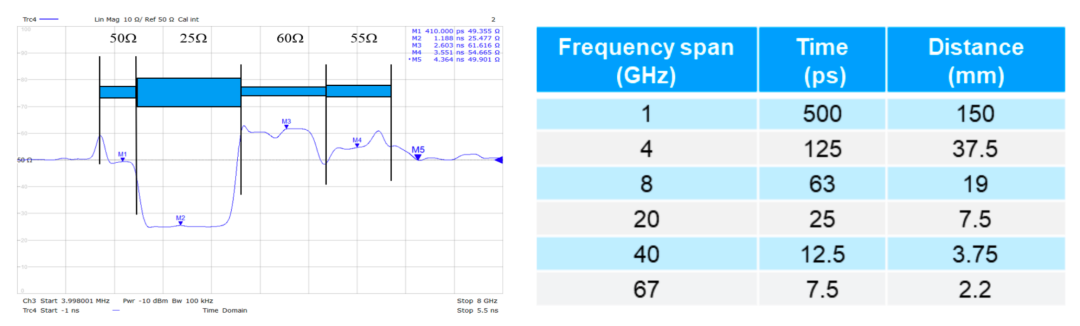

2时域阻抗测试

时域阻抗测试是评估高速PCB阻抗特性的重要手段。通过测量PCB的阻抗值,可以了解PCB的传输线特性阻抗和阻抗匹配情况等。进行时域阻抗测试时,需要选择与DUT相匹配的TDR阻抗探头。探头型号的选取由测量频段和PCB走线间距等因素综合决定。TDR测量的最小时间分辨率近似等于1/(2fmax)。R&S ZNA和R&S ZNB网络分析仪都具有时域分析选件(R&S ZNx-K2),用于时域阻抗的测量。

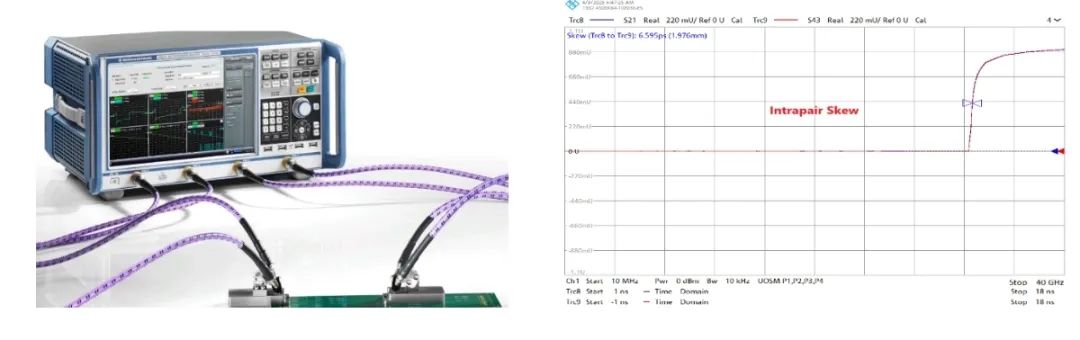

3Rise Time测试和Skew测试

Rise Time测试和Skew测试是评估高速PCB时序特性的重要手段。Rise Time测试可以测量信号的上升时间,从而反映信号的传输速度和响应时间。Skew测试则可以测量不同信号线之间的时间延迟差异,从而评估信号的同步性和时序准确性。

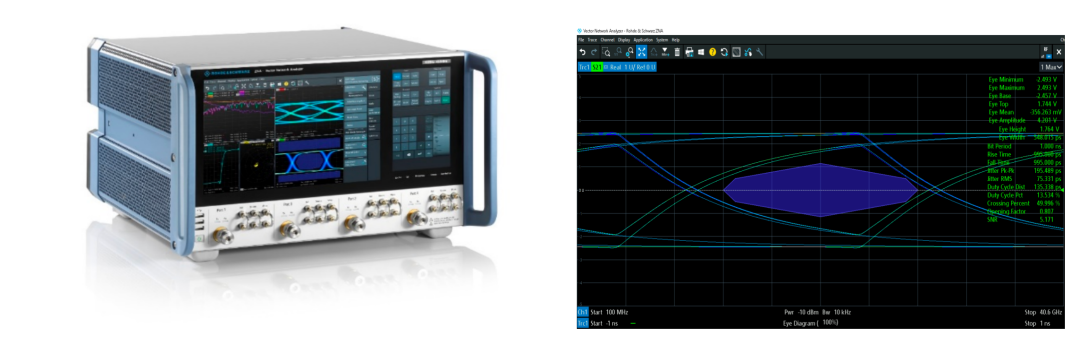

4眼图测试

眼图测试是评估高速PCB信号完整性的重要手段之一。它可以通过观察信号的眼图来评估信号的噪声、抖动和失真等问题。R&S ZNA和R&S ZNB网络分析仪的时域分析扩展选件(R&S ZNx-K20)可以实现PCB的眼图测量,该选件也具有标准的Rise Time测试和Skew测试功能项。

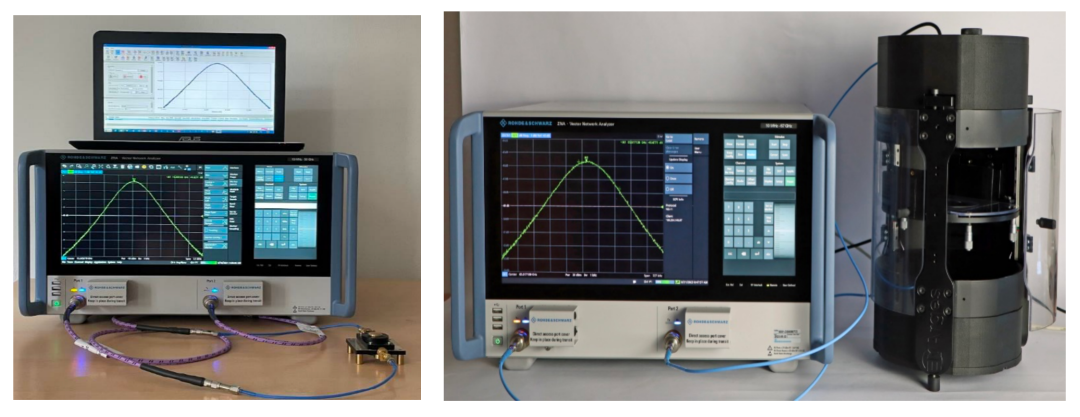

5PCB覆铜板材的Dk/Df测试

PCB覆铜板材的Dk(介电常数)和Df(损耗因子)测试是评估材料介电性能和能量损耗特性的重要手段。测量PCB板材 Dk/Df的常用方法是谐振腔法。根据测量频段的不同,谐振腔法又细分为分离式谐振腔(SPDR)和法布里-珀罗开放式谐振腔 (FPOR)等。SPDR法通常适合于20GHz以下的特性测试,FPOR可以实现20-110GHz的特性测试。

1介电常数(Dk):反映PCB基材的介电性能,是影响信号传输速度和损耗的重要指标。信号的传输速率与材料介电常数的平方根成反比。

2损耗因子(Df):用于评估PCB基材的能量损耗,直接影响高频信号的传输性能。介质损耗越小,传输信号的损耗也越小。

6基于PCB传输线路的Dk/Df/SR测试

PCB的Dk/Df指标,除了通过上述所述的谐振腔法之外,还可以通过测量PCB传输线段的S参数特性,再用算法(例如Djordjevic-Sarkar model)反推层压板材的介电常数(Dk)和介质损耗因子(Df),为覆铜板厂商和PCB制造商提供关键验收指标。

PCB的SR(表面粗糙度)指标测试,可以基于Huray表面粗糙度模型对PCB传输线段的S参数进行算法解析得到。Huray粗糙度模型(Huray Surface Roughness Model)是一种用于描述导体表面粗糙度对高频信号完整性影响的数学模型,它主要用于预测由导体表面粗糙度导致的趋肤效应增强和信号损耗增加的问题。

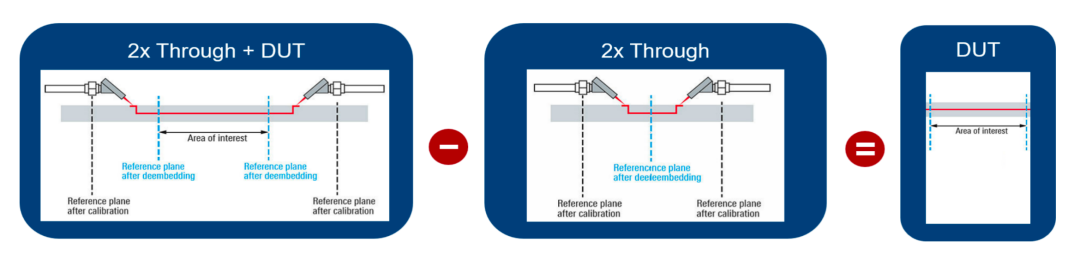

03.去嵌的应用和典型去嵌方法

1去嵌的重要性

对于网络分析仪测试PCB,夹具去嵌至关重要。在进行高速PCB测试时,通常需要借助夹具转接或探头点测才能完成。因此需要通过去嵌技术来消除夹具对DUT测试结果的影响。

2典型去嵌方法

VNA常见的去嵌方法包括基本去嵌方法、高级时域去嵌方法和专用去嵌方法。基本去嵌方法是网络分析仪的基本功能,只适用于较低频率的应用。高级去嵌方法,本质上是基于时域的算法软件。R&S 提供了三种时域去嵌选件:R&SZNx-K210 (EZD)、R&SZNx-K220 (ISD) 和 R&SZNx-K230 (SFD)。通过这些去嵌方法,可对夹具的影响进行精确去除。

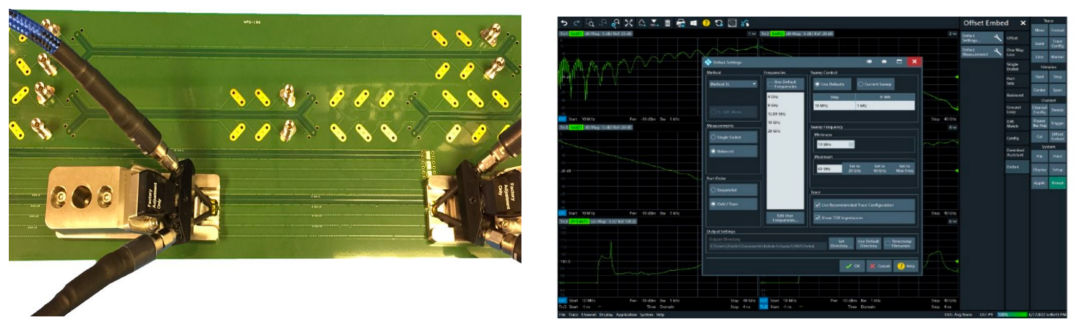

对于PCB产品的测试,还有一些专用的去嵌方法,例如TRL和Delta-L法等。TRL方法相对成熟,在此不再赘述。Delta-L法是由Intel提出的一种基于本征模算法的去嵌方法,当前广泛地用于PCB的插入损耗测试。R&S联合Packet micro推出了Delta-L+测量选件R&S ZNx-K231,全面支持Delta-L 4.0测试。该选件支持高达40GHz的测试,满足Intel的PCB验证标准。使用Delta-L 4.0测量PCB时,通常需要专用的Delta-L 4.0测量探头。目前该类探头的理论上限工作频率为40GHz。

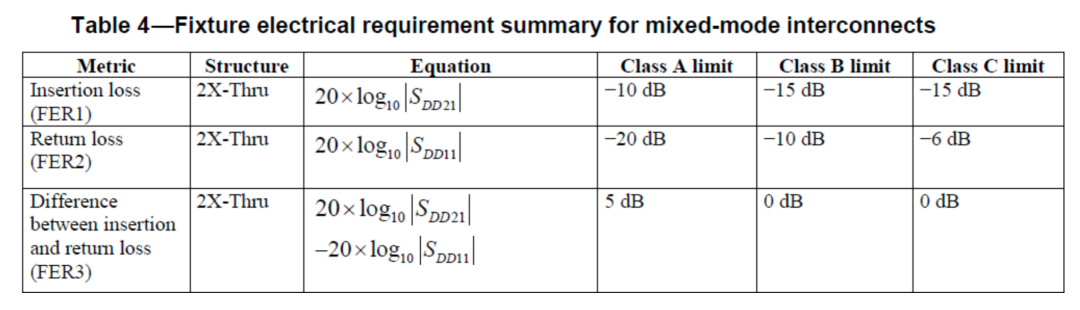

3测试夹具设计

IEEE P370标准规定了夹具设计准则、去嵌验证步骤与S参数验证流程等,以确保去嵌结果的准确性和可靠性。测试夹具的设计对于确保去嵌精度至关重要。为了保证去嵌精度,夹具的插损和回损的差值需要满足一定的条件。下表摘自IEEE Std 370-2020规范。

04.新的挑战与测试需求

随着高速技术的不断发展,高频高速PCB的测试面临新的挑战。

挑战一

PCB的高频谐振问题

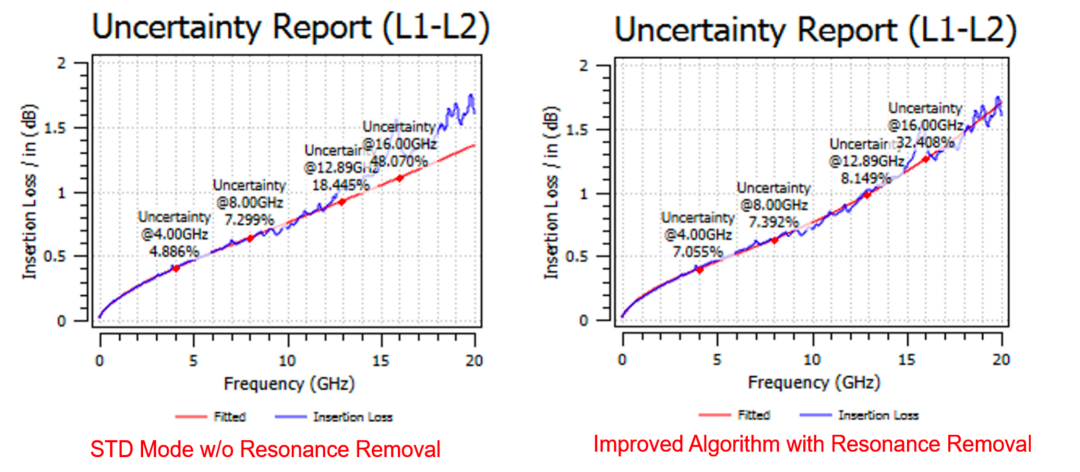

当PCB线路在高频出现谐振时,传统Delta-L 4.0算法的插损拟合结果不确定度大幅增加。R&S ZNA-K231 Delta-L+ 选件将在新的固件版本中更新算法,增加PCB抗谐振测试功能,以解决这一问题。当DUT在高频段出现谐振时,新算法将会对谐振频率以上频段的测量数据重新进行数学加权后再进行拟合,以获得更更高的拟合精度。下图为同一DUT(16GHz左右出现谐振)条件下,标准Delta-L 4.0算法和改进算法的拟合结果对比。

挑战二

224Gbps 高速PCB的去嵌问题

随着224Gbps高速互连系统的推出,高速PCB的最高测量频率将超过67GHz。当前Delta-L 4.0标准方法理论上限频率是40GHz,实际32GHz以上的去嵌精度开始下降。对于40GHz以上的PCB测试,目前较好的去嵌方法还是时域去嵌软件,例如R&S ISD。但鉴于Delta-L法在PCB行业的用户基础极为广泛,现在业界正在致力于67GHz Delta-L测量方案的研究。在更高频率下,夹具和PCB走线的设计对测试结果的影响将更加显著,67GHz Delta-L测量方案推出前需要解决以下问题。

◆现有的Delta-L4.0探头工作频段不够,需要67GHz新型号

◆2*THRU(短线)的长度需要更短以实现损耗更小,从而满足IEEE P370规范

◆2*THRU的EM结构进行仿真优化,尤其是跨层过孔的设计,以获取更好的匹配

◆改进当前算法,以优化高频抗谐振问题

总 结

高频高速PCB测试需综合考虑材料特性、信号完整性和标准合规性三大维度。通过依托高精度仪器(如R&S ZNA)和定制化夹具(如Delta-L 4.0专用针座),结合S参数、TDR、眼图等综合分析方法,以确保PCB的设计满足5G、AI及超算等高速应用的需求。同时,面对不断变化的挑战和趋势,我们还需要不断创新和优化测试方案,以适应未来的技术发展和应用需求。

罗德与施瓦茨业务涵盖测试测量、技术系统、网络与网络安全,致力于打造一个更加安全、互联的世界。成立90 年来,罗德与施瓦茨作为全球科技集团,通过发展尖端技术,不断突破技术界限。公司领先的产品和解决方案赋能众多行业客户,助其获得数字技术领导力。罗德与施瓦茨总部位于德国慕尼黑,作为一家私有企业,公司在全球范围内独立、长期、可持续地开展业务。

-

pcb

+关注

关注

4371文章

23526浏览量

410855 -

测试

+关注

关注

8文章

5737浏览量

129138 -

信号

+关注

关注

11文章

2856浏览量

78439 -

数据中心

+关注

关注

16文章

5256浏览量

73631

原文标题:【仪测高下】高频高速PCB测试

文章出处:【微信号:罗德与施瓦茨中国,微信公众号:罗德与施瓦茨中国】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高频pcb干扰问题及解决方案

高频高速PCB测试解决方案

高频高速PCB测试解决方案

评论