文章来源:学习那些事

原文作者:前路漫漫

本文主要介绍芯片级封装(CSP)。

CSP、倒装芯片、圆片级封装的区别

CSP:封装尺寸与芯片相当,一般超过IC尺寸的20%,是IC级单芯片封装技术,采用标准SMT组装,并进行包封和测试。

倒装芯片:属于圆片级加工技术,在圆片上制作焊料凸点,芯片面朝下进行封装互连,目前通常无法进行圆片级老化和测试。

圆片级封装:在圆片上加工电互连结构,采用SMT技术倒装互连,然后在圆片上完成包封、测试、老化,分割后得到IC成品。

CSP的起源与定义

CSP的概念最早于1993年由Fuiitsu公司的Junichi Kasai和Hitachi Cable公司的Gen Murakami提出。1994年,Mitsubishi Electric公司首次将其实现,它是由BGA经缩小外形和端子间距发展而来。

在CSP技术发展初期,其定义处于模糊与不统一的状态,各厂商对其界定存在显著差异。随着技术演进,行业逐步形成了几种广泛认可的定义标准:日本电子工业协会将芯片面积与封装体面积比例超过80%的封装形式归类为CSP;美国国防部元器件供应中心在J - STK -012标准中明确,若LSI封装产品面积不超过LSI芯片面积的120%,即可认定为CSP;松下电子工业公司则以封装产品边长与芯片边长差值小于1mm作为CSP判定依据。尽管表述有所不同,但这些定义均聚焦于同一核心特质——CSP具备高度紧凑的封装形态,在尺寸上极大程度地趋近于芯片本体。

CSP的性能优势

超小体积与轻薄设计

CSP堪称当前体积最小的LSI芯片封装技术之一。在引脚数量相同的情况下,CSP的面积相较于0.5mm节距QFP,不到其十分之一,仅为普通BGA封装的三分之一至十分之一 。而且,CSP不仅面积小,厚度也极薄,这对于追求轻薄化的电子产品来说,具有极大的吸引力,能够有效提升产品的空间利用率和便携性。

卓越的电性能

CSP内部布线极为精简,相较于QFP或BGA封装,其布线长度大幅缩短 。这一优势直接带来了寄生电容的减小以及信号传输延迟时间的降低。即便面对时钟频率超过100MHz的LSI芯片,CSP也能轻松应对,确保信号的高速、稳定传输。同时,CSP的存取时间相较于QFP或BGA封装改善了15% - 20% ,开关噪声也控制在极低水平,为芯片的高效运行提供了坚实保障。

出色的散热能力

在散热方面,CSP具备独特的优势。大多数CSP采用将芯片面向下安装的方式,使得芯片产生的热量能够通过最短的路径,从芯片背面快速传导至外界 。这种高效的散热方式,配合空气对流或安装散热器等手段,可以对芯片进行充分散热,有效避免芯片因过热而出现性能下降或故障,极大地提高了芯片在长时间、高负载运行时的可靠性。

高I/O密度

随着集成电路技术的发展,芯片的I/O引脚数目不断增加。CSP通过缩小封装面积,在有限的空间内实现了更高的I/O引脚密度 。其封装面积可缩小到BGA的四分之一至十分之一,单位面积容纳的I/O引脚数显著增多,能够很好地满足现代芯片对大量I/O接口的需求,为芯片实现更复杂的功能提供了硬件基础。

CSP的分类

按基片类型分类

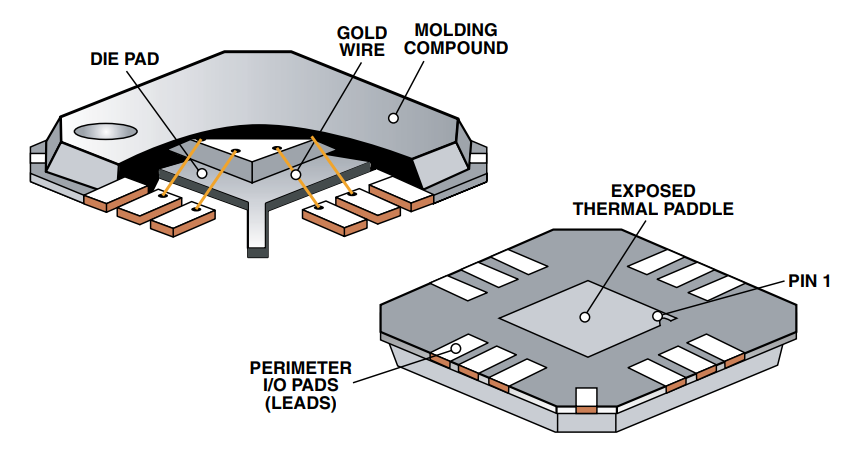

引线框架式CSP:引线框架式CSP的封装载体采用了与传统塑封电路相似的引线框架结构,但在设计上进行了优化,具有更小的外形尺寸和更薄的厚度。其指状焊盘创新性地延伸至芯片内部区域,形成紧密的电气连接布局。在芯片与封装的互连工艺方面,主要采用引线键合技术,其中金丝球焊是较为常用的工艺方法,通过这种方式,能够可靠地实现芯片焊盘与CSP外部焊盘之间的电气导通。得益于与常规塑封电路相近的制造工艺,引线框架式CSP在生产过程中无需进行大规模的设备和工艺调整,显著降低了生产难度和成本,因而具备良好的规模化生产适应性。目前,富士通、日立等行业领先企业已掌握成熟的制造技术,成为该类产品的主要供应商,推动了引线框架式CSP在消费电子、通信等领域的广泛应用。

刚性基片式CSP:IC载体基片由多层布线陶瓷或多层布线层压树脂板制成 。这种基片具有较高的强度和稳定性,能够为芯片提供良好的电气连接和物理支撑。摩托罗拉、索尼、东芝、松下等公司在刚性基片式CSP领域较为领先。

挠性基片CSP:IC载体基片采用塑料薄膜等柔性材料制成,在薄膜上制作有多层金属布线 。该类型CSP具有良好的柔韧性,能够适应一些特殊的应用场景,如可穿戴设备等对封装柔韧性有要求的领域。代表产品包括Tessera公司的microBGA、CTS公司的sim - BGA等。

晶圆级芯片尺寸(WLCSP):主要封装工艺在晶圆上完成,通过介质膜和布线实现从焊盘到焊球外引脚的电性连接以及与其他部分的绝缘 。这种封装方式直接在晶圆阶段进行,避免了后续对单个芯片的复杂封装工序,极大地提高了生产效率,同时进一步减小了封装尺寸。并且,WLCSP可以在晶圆上进行测试和老化筛选,保证了产品的质量和可靠性。

按互连方式分类

倒装片键合CSP;采用芯片有源面反向朝下的独特安装方式,借助芯片表面预设的焊球与基板直接完成电气连接。这种互连架构显著缩短了芯片与基板间的信号传输路径,大幅降低了寄生电感与电容效应,从而显著提升了高频信号传输的稳定性与电气性能。

在工艺实现层面,倒装片键合CSP需依赖多项关键技术协同作业。首先,二次布线技术将芯片周边原始焊盘重新布局为间距优化的阵列结构,为后续连接创造条件;其次,凸点形成技术通过电镀金或焊料沉积工艺,在再分布焊盘上构建可靠的连接凸点;然后,倒装片键合技术利用高精度设备将带有凸点的芯片精准贴合至基板;最后,包封环节采用特殊材料与工艺,着重控制空洞、裂纹产生,增强封装体的水汽阻隔能力,确保长期使用的可靠性。

引线键合CSP:采用短引线键合的方式,将芯片焊盘与封装基片焊盘连接起来 。这种互连方式工艺相对成熟,成本较低。在生产过程中,需要先对晶圆进行减薄、划片处理,然后进行芯片键合和引线键合,最后进行模塑包封、安装焊球等后续工序 。

TAB键合CSP:使用TAB(载带自动键合)技术实现芯片与封装基片的连接 。首先在圆片上制作凸点并进行减薄、划片,接着进行TAB内焊点键合,将引线键合在柔性基片上,然后进行TAB键合线切割成型和外焊点键合,最后进行模塑包封和安装焊球 。TAB键合CSP适用于一些对引脚间距和电气性能有特定要求的应用场景。

-

芯片级封装

+关注

关注

0文章

6浏览量

9425

原文标题:芯片级封装(CSP)简介

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

引线框芯片级封装的建议返修程序

如何选择芯片级测试还是系统级测试?

一文详解提高芯片级封装集成电路热性能的方法

倒装芯片和芯片级封装的由来

瑞沃微:一文详解CSP(Chip Scale Package)芯片级封装工艺

芯片级封装的优势和分类

芯片级封装的优势和分类

评论