半导体芯片易受大电流与高电压现象影响。为实现元件级保护,我们采用片上ESD保护电路来提供安全的静电放电电流泄放路径。静电放电(ESD)是电子设备面临的常见威胁。当ESD事件发生时,一定量的电荷会在两个物体间转移(例如从人体到集成电路)。这种电荷转移可能导致极高电流在极短时间内流经芯片,若器件无法快速耗散能量就会造成损坏。

ESD威胁贯穿产品全生命周期:在制造组装阶段、终端用户使用过程或设备维护期间都可能发生。随着移动设备、汽车电子、工业及医疗应用等新兴技术的快速发展,市场对芯片级ESSD防护提出了独特需求。ESD保护是电子元件的强制性要求,其设计是半导体行业的重点课题。为确保可靠运行,需同时在元件级和器件级考虑ESD防护措施。

ESD元件测试(ESD模型)

行业标准规定了一系列ESD认证测试来保障系统与元件的可靠性。这些标准详细规定了测试流程、设备校准及常规验证程序。本节重点介绍元件级测试,通过这些测试是产品获得认证并上市的前提条件。

模拟日常元件ESD事件的测试模型(各自代表特定物理现象)包括:

? 人体模型(HBM)

? 机器模型(MM)

? 充电器件模型(CDM)

? 传输线脉冲测试(TLP)

【人体模型】

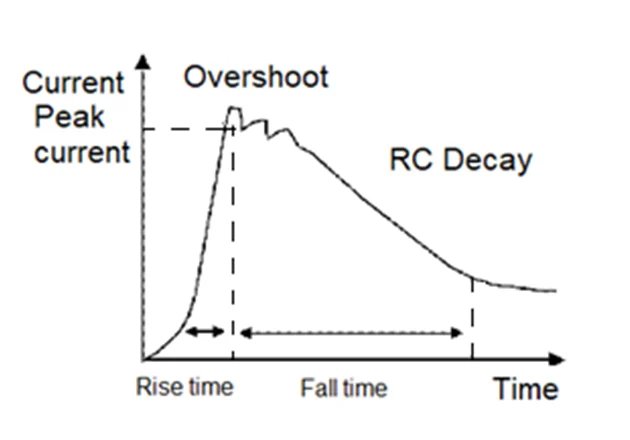

当带电人体用手指接触元件时就会产生人体模型放电。这种最古老的ESD测试最初为采矿行业开发,模拟电荷从手指转移到集成电路引脚(其他引脚接地)的过程。最新数据显示HBM很少能模拟真实ESD事件——现代封装尺寸通常小到无法用手指操作,且大型元件制造多采用自动化设备,人工接触元件的情况极少。图1展示了HBM脉冲波形。

图1

图1【机器模型脉冲】

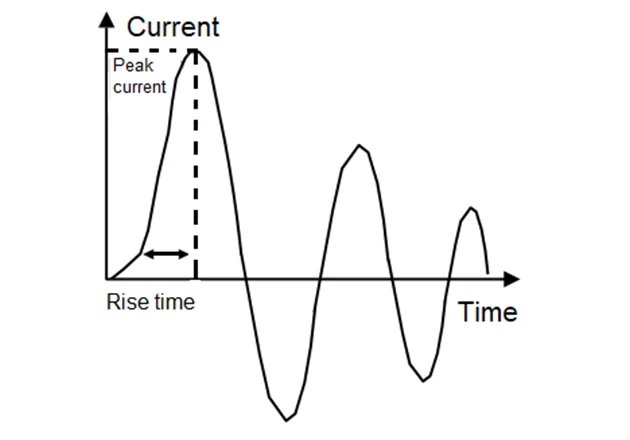

机器模型(MM)用于模拟带电金属物体接触IC引脚的ESD事件。图2显示其脉冲波形。HBM与MM模型的共同点是电荷都转移至受测元件。

图2

图2【充电器件模型】

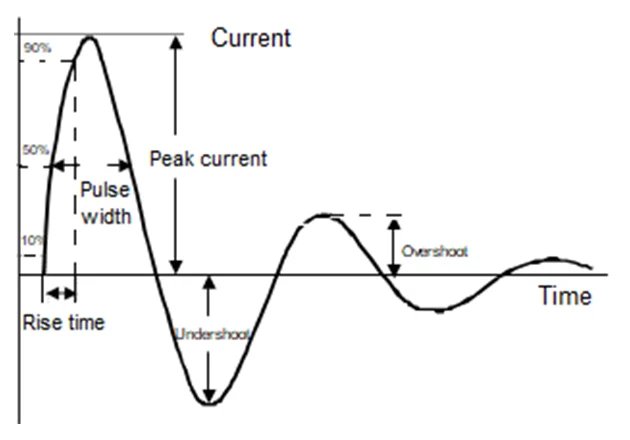

当带电器件接触接地物体时就会产生充电器件模型(CDM)。该测试中元件作为电荷源,通过接物体放电。CDM模型能复现组件在工厂和客户端的失效情况,可检测IC封装带电后通过接地金属物体放电时的脆弱性。这类放电事件是现代电路ESD失效的主因。图3呈现CDM电流波形。

图3

图3【传输线脉冲测试】

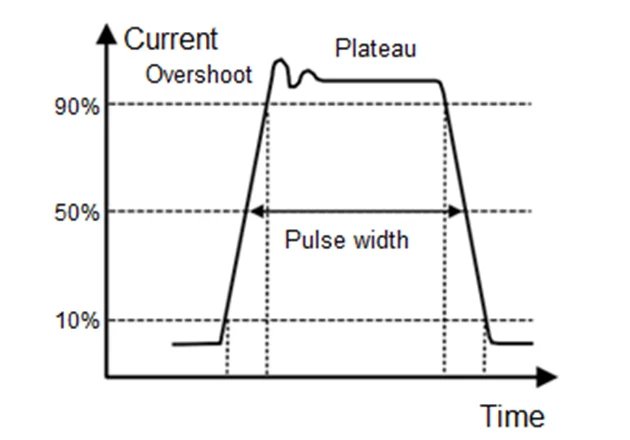

传输线脉冲(TLP)测试中,电压源对同轴电缆充电后,系统会向受测器件释放一系列类ESD脉冲。该方法可评估器件在ESD应力下的工作性能,既能作为HBM方法的等效替代方案,也能测量ESD特性参数。图4显示TLP脉冲波形。

图4

图4常见ESD失效

ESD失效具有破坏性,可导致IC芯片立即功能失常。结区和氧化层尤其易损,主要失效机制包括:

硅结烧毁:最常见的HBM失效机制,ESD瞬态能量注入会导致结击穿

氧化层击穿:当介质层承受高压应力时,介电击穿会引发电流传导,产生的热斑可熔化介质、硅等材料

金属化烧毁:当I?R发热达到材料熔点时互连通路断裂,通常是结/氧化层失效后的次生效应

片上ESD保护器件

片上ESD保护结构通过提供到地总线/电源轨的安全泄放路径,保护核心电路的输入/输出及电源引脚。这些结构在系统正常工作时关闭,ESD事件发生时迅速开启。保护电路会在事件期间将引脚电压钳位在低位,电流泄放后恢复关闭状态,且确保器件不受损。

当工艺限制无法实现片上保护时,可采用线缆、连接器、陶瓷载体或电路板上的片外保护方案。某些情况下,经优化的定制方案能降低成本。优质ESD保护器件需具备四大特性:

? 鲁棒性

? 有效性

? 响应速度

? 电路透明性

保护电路不仅要坚固有效,其开启速度还必须快于被保护主电路,同时不能影响主电路性能。

ESD电路基础构件

保护钳位电路有多种实现技术,选择取决于工艺和设计约束。三种常用ESD保护器件为:

二极管:结构最简单,正向偏置时满足低压ESD应用需求(导通电压低、导通电阻小、电流处理能力强),但反向偏置时性能不佳且漏电流较大

栅极接地NMOS(GGNMOS):通过特殊版图设计优化ESD性能,可工作于主动模式或回滞模式(后者能以低压维持大电流,但鲁棒性较差)

可控硅整流器(SCR):凭借双极导通机制具有最优鲁棒性,但存在闩锁风险(需通过设计控制风险)

注:二极管属无回滞型器件,而SCR和GGNMOS具有回滞特性。

片上ESD保护策略

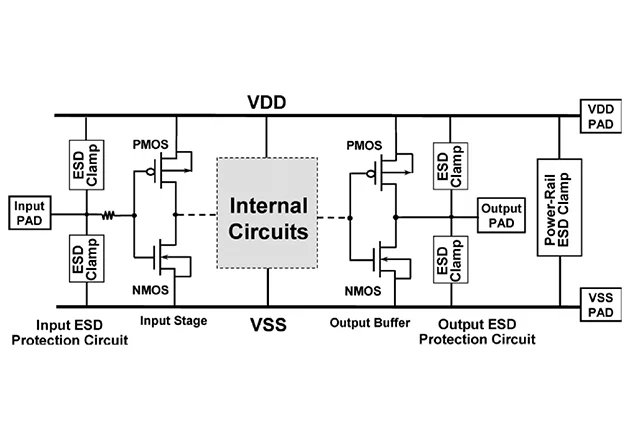

ESD保护策略包括钳制过应力电压,以及利用片上保护结构提供电流泄放路径。输入/输出及电源焊盘均需配置保护电路,这些元件正常工作时保持休眠状态,仅当检测到电压瞬变时才激活泄放通道。图5展示了典型的ESD保护电路布局,包含以下保护组件:

图5

图5? 输入焊盘到地(Vss)

? 输入焊盘到电源轨(Vdd)

? 输出焊盘到地(Vss)

? 输出焊盘到电源轨(Vdd)

? 电源轨(Vdd)到地(Vss)

该技术适用于CMOS、BiCMOS及III-V族化合物等主要工艺。

IC接地技术综述

静电放电本质是不同电势物体间的电荷转移现象,其快速能量释放会损坏IC。ESD防护通过建立安全泄放路径、耗散能量及电压钳位来实现保护。随着半导体尺寸持续缩小,ESD失效已成为更严峻的可靠性挑战。验证电路设计的ESD免疫力和可靠性至关重要,主要元件级标准包括HBM、MM和CDM。典型ESD防护器件包括二极管、GGNMOS和SCR。片上保护器件在常态下关闭,达到阈值电压后导通电流,从而保护内部电路免受损伤。

-

ESD

+关注

关注

50文章

2297浏览量

175998 -

电路设计

+关注

关注

6713文章

2546浏览量

215114 -

半导体芯片

+关注

关注

61文章

934浏览量

71488

发布评论请先 登录

半导体芯片的ESD静电防护:原理、测试方法与保护电路设计

半导体芯片的ESD静电防护:原理、测试方法与保护电路设计

评论