概述

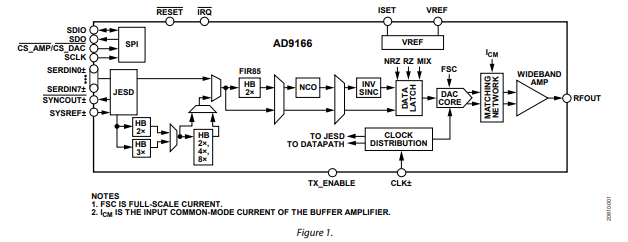

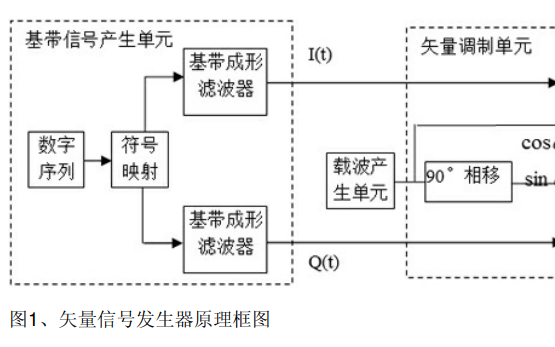

AD9166是高性能、宽带、片内矢量信号发生器,由高速 JESD204B 串行器/解串器(SERDES)接口、灵活的 16 位数字数据路径、正交 (IQ) 数模转换器 (DAC) 内核以及一个集成的差分至单端输出缓冲放大器组成 ,可匹配高达 10 GHz 的 50 Ω 负载。

数据表:*附件:AD9166直流至9GHz,矢量信号发生器 技术手册.pdf

DAC 内核基于四开关架构,可改变配置提高 DAC 内核的有效更新速率,从 6.4 GHz DAC 采样时钟配置为高达 12.8 GSPS,模拟输出带宽通常为直流至 9.0 GHz。数字数据路径包括多个插值滤波器级,具有支持快速跳频 (FFH) 的多个数控振荡器 (NCO) 的直接数字频率合成器 (DDS) 块,以及额外的 FIR85 和反 Sinc 滤波器级,以实现灵活的频谱规划。

与单端缓冲器的差分消除了对宽带巴伦的需求,并支持 DAC 内核的全部模拟输出带宽。直流耦合输出可以基带波形,而无需外部偏置三通或类似电路,这使得 AD9166 特别适合应用在最苛刻的高速超宽带 RF 发射。

各种滤波器级使 AD9166 可以配置为较低的数据速率,同时保持较高的 DAC 时钟速率,以简化滤波要求并减小整体系统尺寸,重量和功耗。

数据接口接收器包含多达 8 个 JESD204B SERDES 通道,每个通道可承载 12.5 Gbps。为了实现较大的灵活性,可以根据数据速率、SERDES 通道数量和 JESD204B 变送器所需的通道映射对接收器进行全面配置。

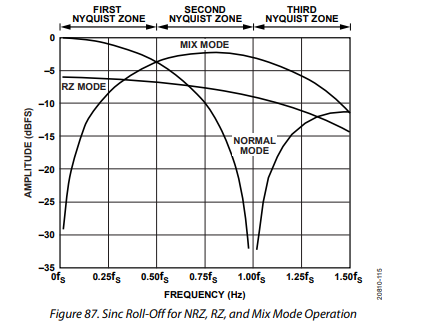

在 2x 非归零 (NRZ) 工作模式(启用 FIR85)下,AD9166 可以将RF载波从真实直流重构到第三个奈奎斯特区的边缘,或者重建高达 9 GHz 的真实直流的模拟带宽。

在混合模式下,AD9166 可以在第二和第三奈奎斯特区域重构 RF 载波,同时消耗较低的功率,并保持与 2×NRZ 模式相当的性能。

在基带模式下,例如归零 (RZ) 和 1x NRZ,AD9166 非常适合将 RF 载波从真实直流重构到第一个奈奎斯特区的边缘,同时与 2x NRZ 模式相比功耗更低。

正交 DDS 块可以配置为数字上变频器,以将 I/Q 数据采样上变频到频谱中所有三个奈奎斯特区域中的所需位置。

DDS 还包括一组 32 个数控振荡器(NCO),每个振荡器都有各自的 32 位相位累加器。当与100 MHz 串行外围接口 (SPI) 结合使用时,DDS 允许相位相干 FFH,相位建立时间低至 300 ns。

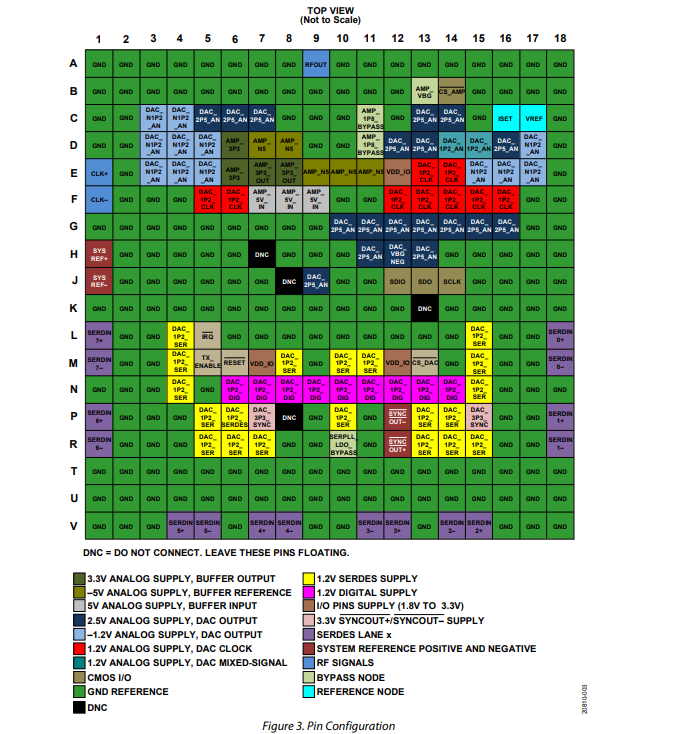

AD9166 使用公共 SPI 接口配置,该接口监测所有寄存器状态。AD9166 采用 324 引脚,15 mm × 15 mm,0.8 mm 间距 BGA_ED 封装。

应用

特性

- 直流耦合、50Ω 匹配输出

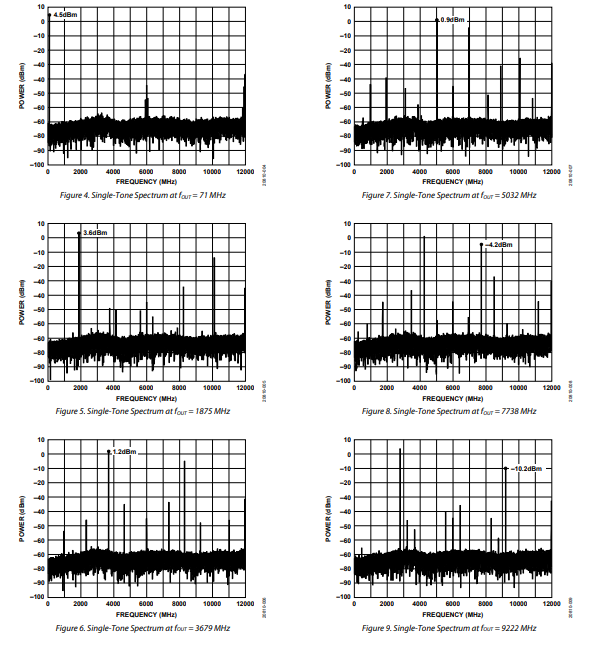

- 高达 4.3 dBm 的输出功率,9 GHz 时为 -9.5 dBm

- DAC 内核更新率:2×NRZ 模式下为 12.0 GSPS(保证的最小值)

- 宽模拟带宽

- 2×NRZ 模式下,直流至 9.0 GHz(12.0 GSPS DAC 更新速率)

- 在混合模式下,1.0 GHz 至 8.0 GHz(6.0 GSPS DAC 更新速率)

- 在 NRZ 模式下,直流至 4.5 GHz(6.0 GSPS DAC 更新速率)

- 2×NRZ 模式下的功耗为 4.88 W(10 GSPS DAC 更新速率)

- 旁路数据路径插值

- 2×, 3×, 4×, 6×, 8×, 12×, 16×, 24×

- 瞬时(复杂)信号带宽

- 设备时钟为 5 GHz 时为 2.25 GHz( 2 倍插值)

- 设备时钟为 6 GHz 时为 1.8 GHz( 3 倍插值)

- 快速跳频

- 集成 biCMOS 缓冲区放大器

功能框图

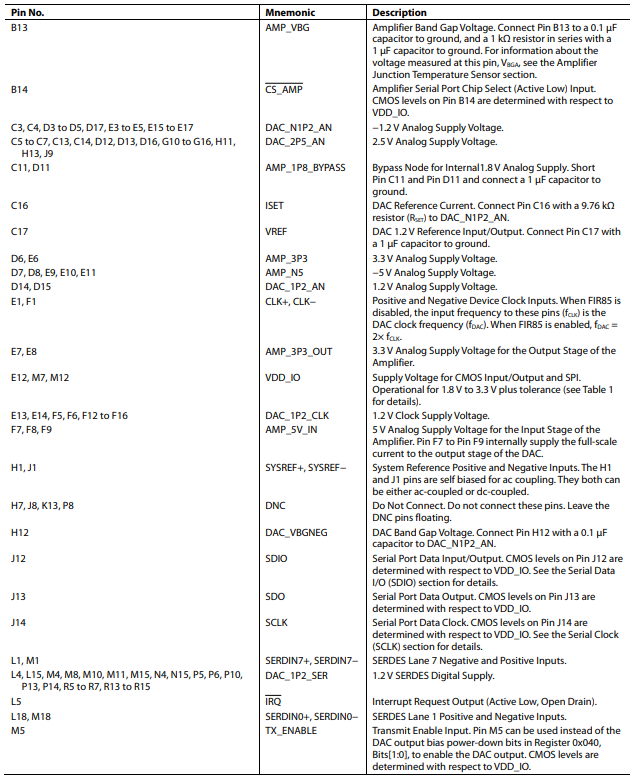

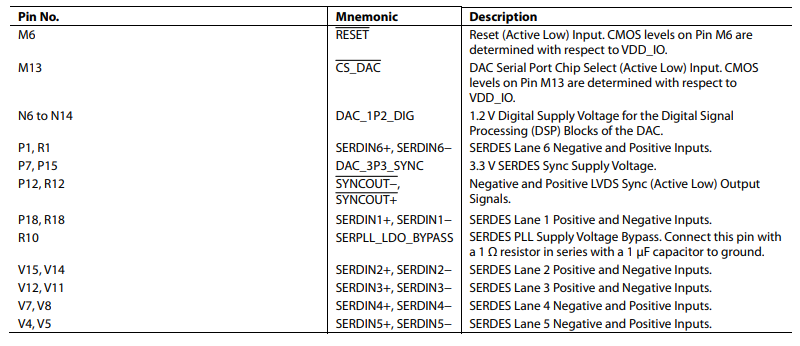

引脚配置描述

典型性能特征

模拟接口注意事项

模拟工作模式

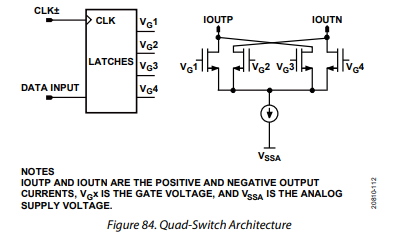

AD9166数模转换器(DAC)内核采用图84所示的四开关架构。每个时钟周期内仅启用一对开关。这要求每对开关在半个时钟周期内进行切换,使得它们在交替的时钟沿上进行采样。因此,在传统双开关架构中出现的与码相关的毛刺现象得以消除。

数据输入

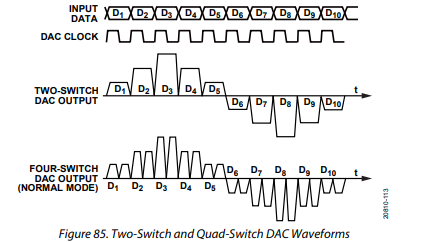

在双开关架构中,当图85中的数据1和数据2(以及D)处于不同状态时,会出现毛刺。然而,如果D和D'在同一时刻发生变化,且不出现毛刺。这是因为与码相关的毛刺会导致额外的时钟沿采样。四开关架构确保在半个时钟周期内传输的两个数据字都不会出现与码相关的毛刺,从而消除了此过程中2×**f_{oc}**处的毛刺。因此,在输出频谱中可以明显看到2×**f_{oc}**处存在显著的时钟杂散。

由于四开关架构允许在每个半时钟周期进行更新,所以可以在2×时钟速率下更新DAC内核。在设备时钟(f_{DAC})的上升沿和下降沿,DAC内核都会锁存新数据样本。

在RZ模式下,DAC内核在时钟上升沿锁存新数据样本,而在时钟下降沿输出为零。在2×NRZ模式下,时钟下降沿的输出样本仅仅是时钟上升沿采样值的反相。在2×NRZ模式中,时钟上升沿和下降沿都会锁存新数据样本。更多细节请参见2×NRZ模式部分。

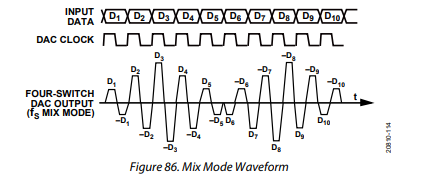

使用混频模式时,输出实际上在DAC采样速率处被斩波。这种斩波的效果是将以DAC采样速率为中心的镜像频率下移,从而提高了这些镜像频率的动态范围。

这种改变混频模式的能力为用户提供了灵活性,可以根据所选的工作模式在前三个奈奎斯特区域内放置载波。在基带模式和混频模式之间切换会切换掉DAC输出固有的反sinc滚降特性。在基带模式下,反sinc零点出现在**f_{s}**处,因为上升沿锁存的样本也会在下降沿再次锁存,从而在相同的负频率位置出现。然而,在混频模式下,上升沿锁存的样本会在下降沿被推到2×**f_{s}**处。图87展示了理想的频率响应,反sinc滚降特性包含在其中。

四开关架构可通过SPI寄存器0x152的位[10]配置为在2×NRZ模式(0b00)、RZ模式(0b10)或混频模式(0b01)下工作。

-

dac

+关注

关注

44文章

2419浏览量

194175 -

数模转换器

+关注

关注

14文章

1075浏览量

84268 -

信号发生器

+关注

关注

28文章

1582浏览量

110857

发布评论请先 登录

Agilent E4438C矢量信号发生器供应Agilent E4438C矢量信号发生器 Agilent E4438C ESG矢量信号发生器

回收闲置 Keysight N5166B 射频矢量信号发生器

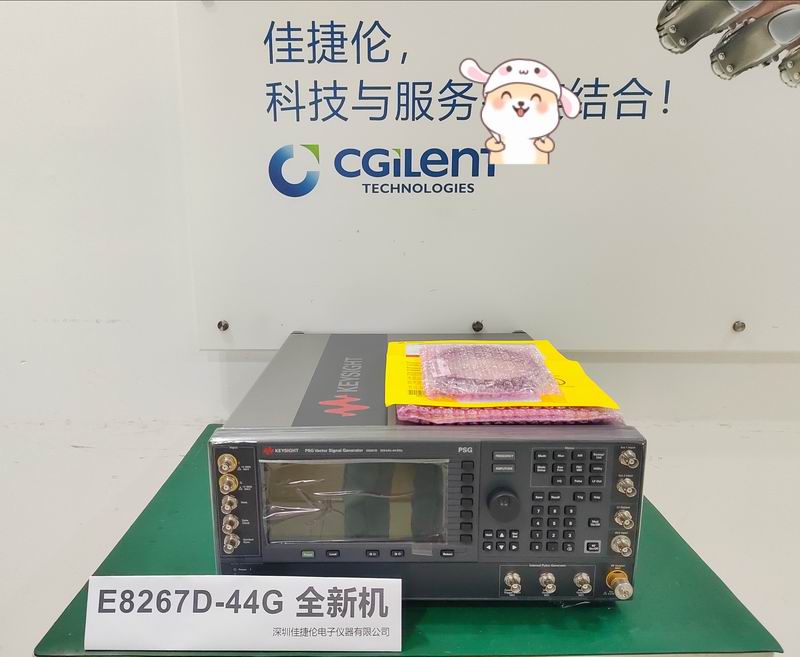

E8267D PSG 矢量信号发生器,100 kHz 至 44 GHz

安捷伦83650L信号发生器,10 MHz至50 GHz技术指标

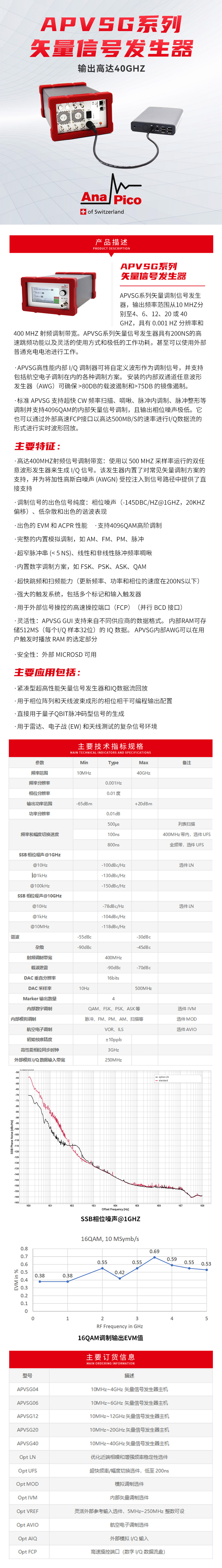

最新信号发生器科技: 2 GHz 带宽的双通道 44 GHz矢量信号发生器

KEYSIGHT E8267D PSG 矢量信号发生器,100 kHz 至 44 GHz

矢量信号发生器SMBV100B介绍

AD9166直流至9GHz,矢量信号发生器 技术手册

AD9166直流至9GHz,矢量信号发生器 技术手册

评论