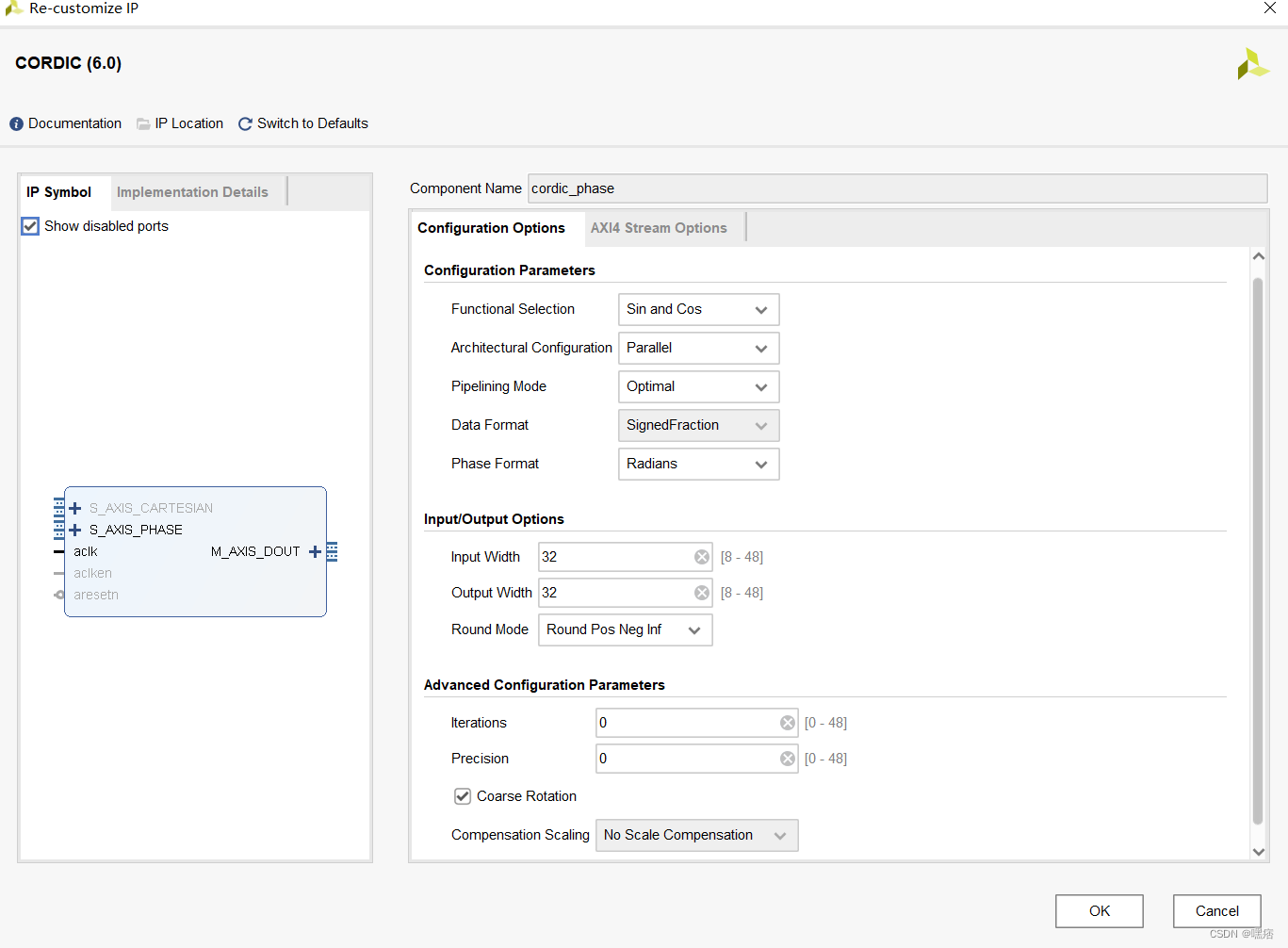

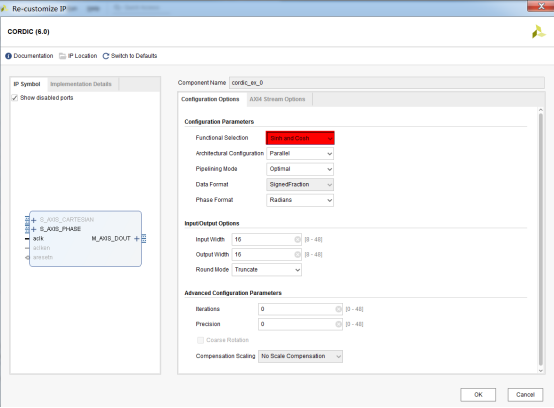

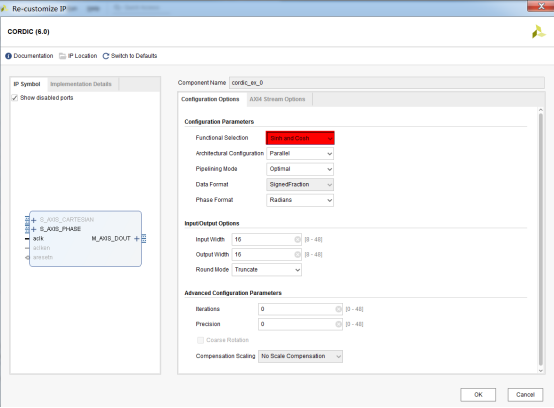

IP核的配置

其输入为角度值。

1. 功能选择为sin and cos(输出时sin在高32位,cos在低32位)

2.Architectural Configuration选择为并行模式,具有单周期数据吞吐量和较大的硅面积。具有并行结构配置的CORDIC核使用移位相加子级数组并行实现这些移位相加操作。该并形电路的实现规模与(内部精度 * 迭代次数)成正比。

3.Pipelining Mode选择Optimal:在不使用任何额外LUT的情况下,以尽可能多的使用流水线级数。

4.Signed Fraction:有符号分数(默认格式)。X和Y的输入和输出表示为整数宽度为2位的二进制补码定点数。这里输入的角度值是第一位表示正负,第二位和第三位表示整数部分,后29位表示小数部分,范围[-π,π]。输出的值是第一位表示正负,第二位表示整数部分,后30位表示小数部分,范围[-1,1]。

5.Radians:弧度制,范围[-Pi,Pi]。相位将表示位整数宽度位3位的二进制补码定点数。

6.Round Mode:Pos Neg Infinity:类似 round(x)。 四舍五入。

7.Iterations

当设置为0时(默认情况),执行的迭代次数由输出的所需精度决定,自动确定迭代次数,通常为输出位宽。

手动设置时,开方设置比较复杂,参照手册描述。其他情况下,对于位宽大于13的,应加1。

8.Precision

控制要执行的内部 add-sub 计算精度。

当设置为0时(默认情况),根据输出所需精度和内部迭代次数自动确定内部精度。

设置为( Input _ Width + Output _ Width + log2 ( Output _ Width) )时,无论输入幅度如何,输出相位都精确到全输出宽度。

9.Coarse Rotation

控制粗旋转模块的实例化。作用于:Vector rotation, Vector translation, Sin and Cos, and ArcTan 功能。

关闭粗旋转模块,输入输出范围限制在第一象限( - Pi / 4至+ Pi / 4)。

开启粗旋转模块,粗旋转通过将输入样本旋转到第一象限,反向旋转输出样本回到合适的象限,将CORDIC运算范围扩展到全圆。

10.Compensation Scaling

控制用于补偿CORDIC幅度缩放的补偿缩放模块。作用于:Vector Rotation and Vector Translation 功能。当选择不补偿时输出是乘了倍数Z的。对于 Sin, Cos, Sinh, Cosh, ArcTan, ArcTanh and Square Root 无影响,应设置为 No Scale Compensation。

modulesincos_test( input clk, input start, input[31:0] pha_in, outputwire over, outputwire[31:0] sin_out, outputwire[31:0] cos_out ); cordic_sincos my_sincos ( .aclk(clk), // input wire aclk.s_axis_phase_tvalid(start), // input wire s_axis_phase_tvalid.s_axis_phase_tdata(pha_in), // input wire [31 : 0] s_axis_phase_tdata.m_axis_dout_tvalid(over), // output wire m_axis_dout_tvalid.m_axis_dout_tdata({sin_out,cos_out}) // output wire [63 : 0] m_axis_dout_tdata); endmodule

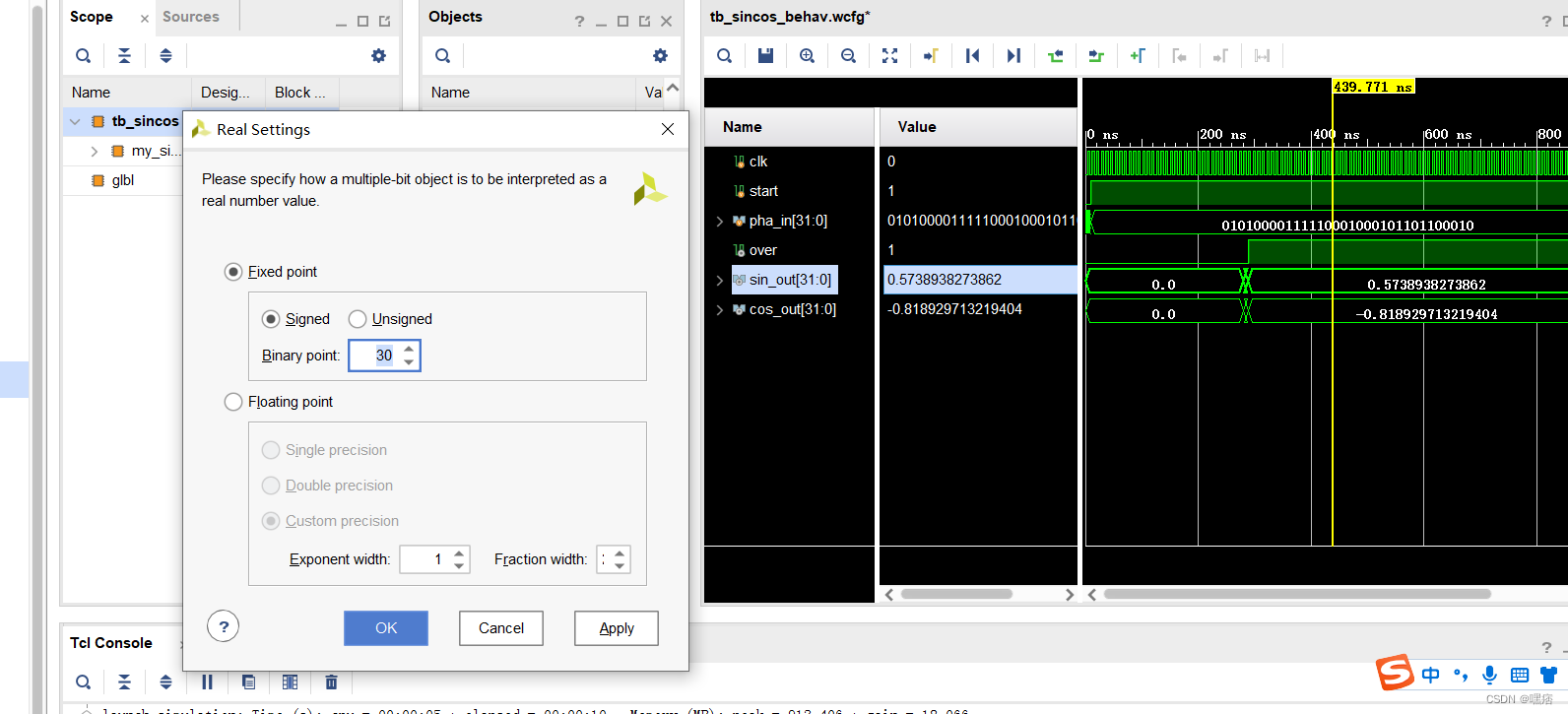

`timescale1ns / 1psmoduletb_sincos();regclk =0;regstart =0;reg[31:0] pha_in=0;wireover;wire[31:0] sin_out;wire[31:0] cos_out;always#4.069clk=~clk;initialbegin #10 start<=1;?// ? ? ? pha_in<=32'b00111001000000000000000000000000;? ? ? ? ?pha_in<=32'b01010000111110001000101101100010; ? ?endsincos_test my_sincos_test ( ? ?.clk? ? ? ? ? (clk), ? ?.start? ? ? ? (start), ? ?.pha_in? ? ? ?(pha_in), ? ?.over? ? ? ? ?(over), ? ?.sin_out? ? ? (sin_out), ? ?.cos_out? ? ? (cos_out) );endmodule

仿真结果:

-

模块

+关注

关注

7文章

2789浏览量

50588 -

IP核

+关注

关注

4文章

338浏览量

50876 -

Vivado

+关注

关注

19文章

835浏览量

68915

原文标题:vivado IP核 cordic 中sin和cos的计算

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Xilinx FPGA入门连载73:波形发生器之IP核CORDIC(正弦波)配置

请问8335电机套件程序中sin cos怎么计算

LabVIEW FPGA CORDIC IP核的arctan使用方法

xilinx vivado调用cordic IP核进行实现时报错多重驱动?

使用Xilinx CORDIC IP核生成正、余弦波

了解Vivado中IP核的原理与应用

Vivado中xilinx_courdic IP核的使用方法

Vivado中xilinx_courdic IP核(求exp指数函数)使用

Xilinx Vivado DDS IP使用方法

vivado IP核cordic中sin和cos的计算

vivado IP核cordic中sin和cos的计算

评论