概述

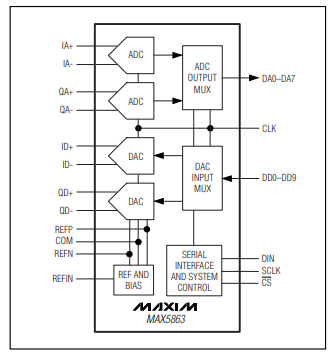

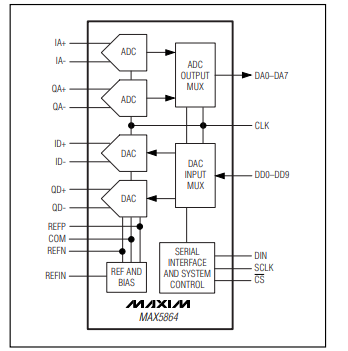

MAX5865超低功耗、高度集成的模拟前端适用于便携式通信设备,如手机、PDA、WLAN以及3G无线终端。MAX5865集成了双路8位接收ADC和双路10位发送DAC,以极低的功耗提供更高的动态性能。ADC的模拟I-Q输入放大器为全差分模式,可以接受1VP-P满量程信号。I-Q通道相位匹配典型值为±0.2°,幅度匹配典型值为±0.05dB。fIN = 5.5MHz和fCLK = 40MHz时,ADC的SINAD为48.4dB,无杂散动态范围(SFDR)为70dBc。DAC的模拟I-Q输出为全差分模式,满量程输出为±400mV,共模电压为1.4V。I-Q通道的相位匹配为±0.15°,增益匹配为±0.05dB。fOUT = 2.2MHz和fCLK = 40MHz时,DAC也具有双路10位分辨率,SFDR为72dBc、SNR为57dB。

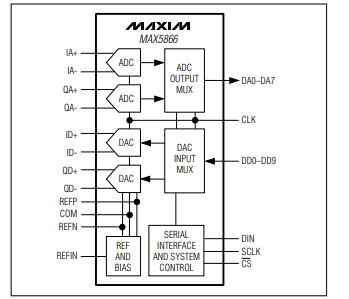

针对频分双工(FDD)与时分双工(TDD)模式,ADC与DAC可以同时工作或独立工作。3线串行接口控制关端和收发器的工作模式。收发模式下ADC与DAC同时工作、fCLK = 40Msps时,功耗典型值为75.6mW。MAX5865具有内部1.024V电压基准,在整个电源供电范围与工作温度范围内保持稳定。MAX5865工作在+2.7V至+3.3V模拟电源,为保证逻辑兼容性带有一个+1.8V至+3.3V数字I/O电源输入。空闲模式下静态电流为8.5mA,关断模式下为1?A。MAX5865工作温度范围为-40°C至+85°C,采用48引脚薄型QFN封装。

数据表:*附件:MAX5865超低功耗、高动态性能、40Msps模拟前端技术手册.pdf

应用

- 3G无线终端

- 固定/移动宽带无线调制解调器

- 窄带/宽带CDMA手机

- PDA

特性

- 集成的双路8位ADC与双路10位DAC

- 超低功耗

- f

CLK= 40MHz时75.6mW (收发器模式) - f

CLK= 22MHz时64mW (收发器模式) - 低电流空闲与关断模式

- f

- 优越的动态性能

- f

IN= 5.5MHz时SINAD为48.4dB (ADC) - f

OUT= 2.2MHz时SFDR为70dB (DAC)

- f

- 优越的增益/相位匹配

- f

IN= 5.5MHz时±0.2°相位匹配,±0.05dB增益(ADC)匹配

- f

- 内部/外部基准选择

- +1.8V至+3.3V数字输出电压(TTL/CMOS兼容)

- 为ADC/DAC提供多路复用并行数字输入/输出

- 微型48引脚薄型QFN封装(7mm x 7mm)

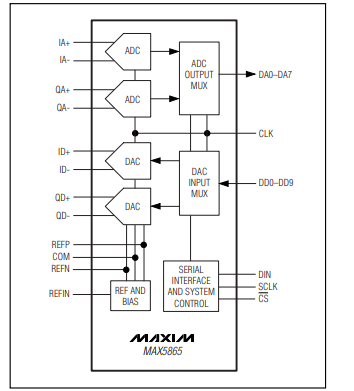

框图

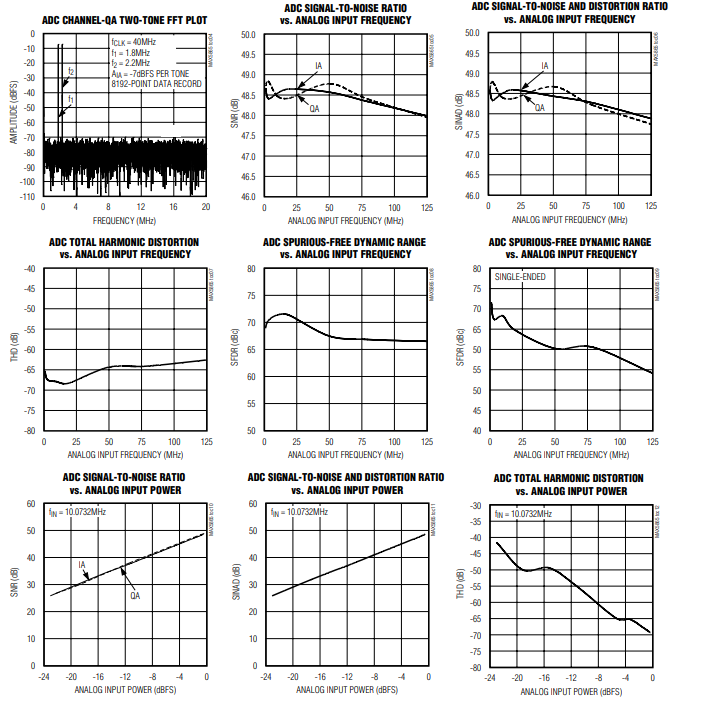

典型操作特性

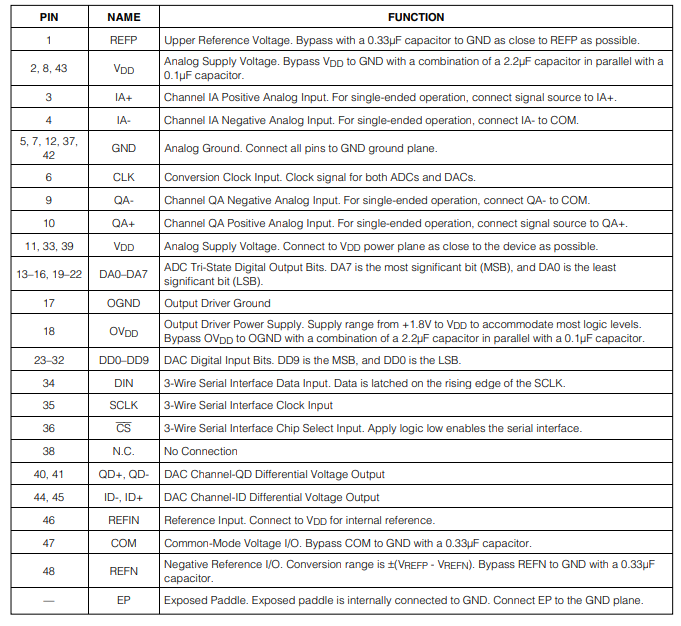

引脚描述

应用信息

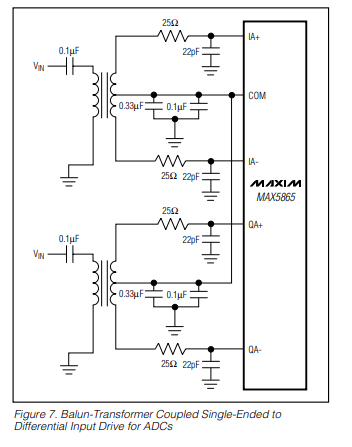

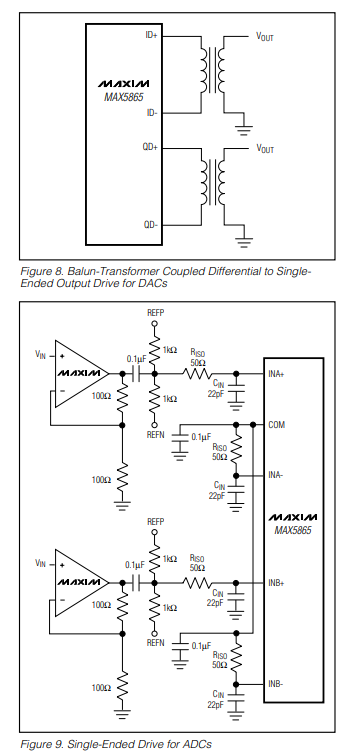

使用平衡 - 不平衡变压器交流耦合

射频变压器(图7)为将单端信号源转换为全差分信号提供了极佳方案,有助于实现ADC的最佳性能。将变压器的中心抽头连接到COM引脚,可使输入获得VDD/2的直流电平偏移。可以选择1:1变压器,也可选用升压变压器来降低驱动要求。一般来说,MAX5865在处理全差分输入信号方面优于SPDR和THD信号,尤其是在较高输入频率下。在差分模式中,由于两个输入端(IA+、IA - 、QA+、QA - )相互平衡,偶次谐波更低,并且每个ADC输入所需的信号摆幅仅为单端模式下的一半。图8展示了一个使用射频变压器将MAX5865 DAC的差分模拟输出转换为单端输出的示例。

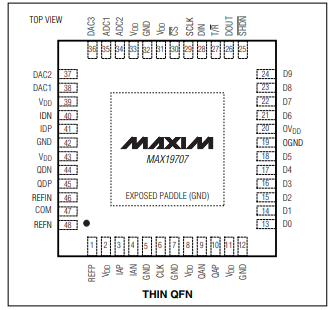

使用运算放大器耦合

当没有平衡 - 不平衡变压器可用时,可用运算放大器驱动MAX5865的模数转换器(ADC)。图9和图10展示了在交流耦合单端和直流耦合差分应用中,用运算放大器驱动ADC的情况。像MAX4354、MAX4454这类放大器具备高速、高带宽、低噪声和低失真特性,可维持输入信号完整性。图10中的电路也可用于数模转换器(DAC)差分模拟输出的接口,以提供增益或缓冲。DAC差分模拟输出不能用于单端模式,因为其内部产生的共模电平为1.4 VDC 。此外,DAC模拟输出设计要求采用差分输入级,且输入阻抗需≥70 kΩ。若需要单端输出,可使用一个放大器来实现差分转单端转换,并选择具有合适输入共模电压范围的放大器。

频分双工(FDD)和时分双工(TDD)模式

MAX5865可用于多种工作在FDD或TDD模式下的应用。在FDD模式下,MAX5865可用于Xcvr模式的应用,如WCDMA 3GPP(FDD)和4G技术。此外,MAX5865还能在Tx和Rx模式间切换,适用于TD - SCDMA、WCDMA - 3GPP(TDD)、IEEE 802.11a/b/g和IEEE 802.16等TDD应用。

在FDD模式下,ADC和DAC同时工作。ADC总线和DAC总线相互隔离,且必须分别连接到18位并行总线(8位ADC和10位DAC)的数字基带处理器。通过三线串行接口选择Xcvr模式,并使用转换时钟来锁存数据。在FDD模式下,当fCLK = 40MHz时,MAX5865的功耗为7.6mW 。这是ADC和DAC同时工作时的总功耗。

在TDD模式下,ADC和DAC独立工作。ADC和DAC总线可连接在一起,形成一个10位并行总线,连接到数字基带处理器。通过三线串行接口,在Rx模式下使能ADC,在Tx模式下使能DAC。在Rx模式下工作时,DAC不传输数据,其内核被禁用,ADC总线处于三态,这样可消除任何不需要的寄生发射,防止总线竞争。在TDD模式下,当fCLK = 40MHz时,MAX5865在Rx模式下的功耗为6.3mW ,Tx模式下DAC的功耗为3.4mW。

-

dac

+关注

关注

44文章

2419浏览量

194169 -

模拟前端

+关注

关注

3文章

224浏览量

30476 -

ADC

+关注

关注

0文章

216浏览量

16845

发布评论请先 登录

低功耗模拟前端芯片MAX586的工作原理是什么?

超低功耗高度集成的模拟前端MAX5865电子资料

超低功耗模拟前端集成电路MAX19705相关资料分享

MAX5865中文资料pdf

LTC2192/LTC2191/LTC2190:16位、65Msps/40Msps/25Msps低功耗双ADC产品手册

LTC2182/LTC2181/LTC2180:16位、65Msps/40Msps/25Msps低功耗双ADC产品手册

MAX5865超低功耗、高动态性能、40Msps模拟前端技术手册

MAX5865超低功耗、高动态性能、40Msps模拟前端技术手册

评论