概述

AD6643是一款11位、200 MSPS/250 MSPS、双通道中频(IF)接收机,专门针对要求高动态范围性能、低功耗和小尺寸的电信应用中支持多通道系统而设计。

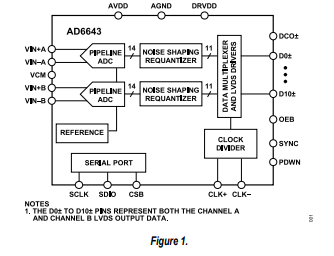

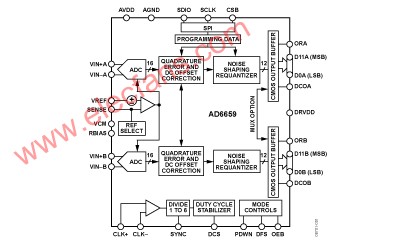

该器件包括两个高性能模数转换器(ADC)和噪声整形再量化器(NSR)数字模块。每个ADC由多级、差分流水线架构组成,并集成了输出纠错逻辑,每个ADC差分流水线的第一级包含一个宽带宽开关电容采样网络。集成基准电压源可简化设计考量。占空比稳定器(DCS)补偿ADC时钟占空比的波动,使转换器保持出色的性能。

数据表:*附件:AD6643双通道中频接收机技术手册.pdf

各ADC的输出内部连接到NSR模块。集成NSR电路能够提高奈奎斯特带宽内较小频段的信噪比(SNR)性能。该器件支持两种不同的输出模式,通过SPI可以选择输出模式。如果使能NSR特性,则在处理ADC的输出时,AD6643可以在有限的部分奈奎斯特带宽内实现更高的SNR性能,同时保持11位输出分辨率。

可以对NSR模块进行编程,以提供采样时钟22%或33%的带宽。例如,当采样时钟速率为185 MSPS时,在22%模式下,AD6643可以在40 MHz带宽内实现最高75.5 dBFS的SNR;在33%模式下,它可以在60 MHz带宽内实现最高73.7 dBFS的SNR。

禁用NSR模块时,ADC数据直接以11位的分辨率提供给输出端。这种工作模式下,AD6643能够在整个奈奎斯特带宽内实现最高66.5 dBFS的SNR。因此,AD6643可以用于电信应用,例如要求更宽带宽的数字预失真观测路径。

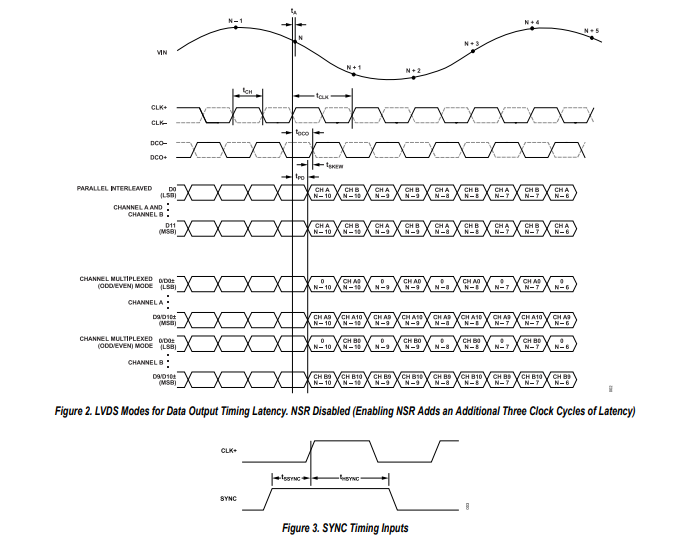

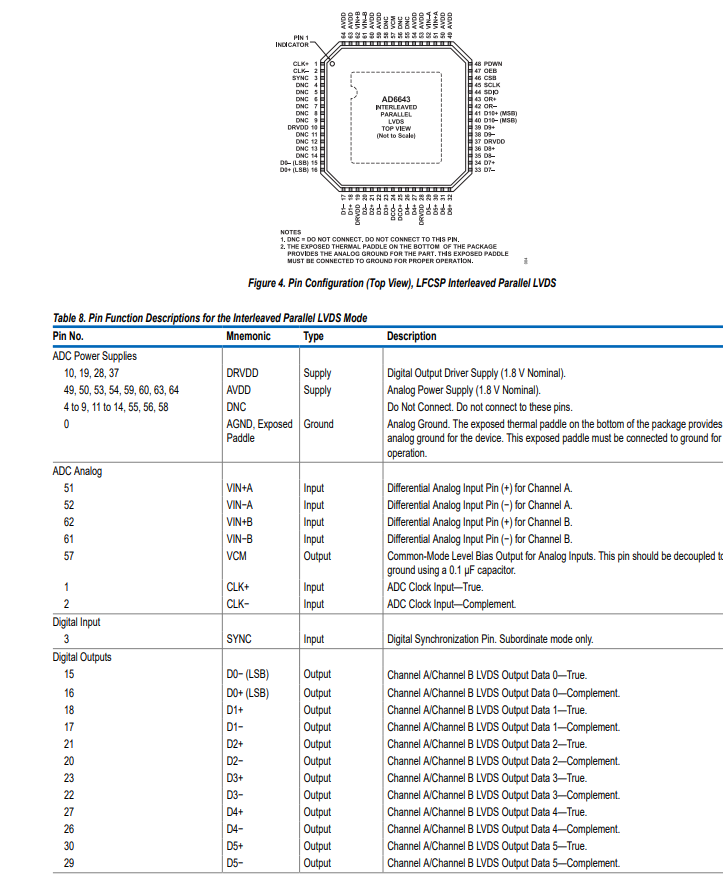

经过数字信号处理后,多路复用输出数据路由至一个11位输出端口,最大数据速率为400 Mbps (DDR)。这些输出设置为LVDS,支持ANSI-644电平。

AD6643接收器能够对很宽的中频频谱进行数字化处理。各接收机设计用于同步接收不同的天线。该IF采样架构与传统的模拟技术或较低集成度的数字方法相比,能大幅度降低元件的成本和复杂度。

灵活的掉电选项可以明显降低功耗。器件设置与控制的编程利用三线式SPI兼容型串行接口来完成;该接口提供多种工作模式,支持电路板级系统测试。

AD6643采用64引脚无铅9 mm × 9 mm引脚架构芯片级封装(LFCSP_VQ),符合RoHS标准,额定温度范围为?40°C至+85°C工业温度范围。该产品受美国专利保护。

产品聚焦

- 两款ADC均采用节省空间的9 mm × 9 mm × 0.85 mm、64引脚LFCSP小型封装。

- 引脚可选的噪声整形再量化器(NSR)功能,能够在185 MSPS下带宽降低至最大60 MHz时提高信噪比。

- LVDS数字输出接口针对低成本FPGA系列而配置。

- 采用1.8 V单电源供电。

- 标准串行端口接口(SPI)支持各种产品特性和功能,例如:数据格式化(偏移二进制或二进制补码)、NSR、掉电、测试模式以及基准电压模式。

- 片内1到8整数输入时钟分频器和多芯片同步功能支持广泛的时钟方案和多通道子系统。

应用

特性

- 每个通道11位、250 MSPS输出数据速率

- NSR使能时的性能

- NR:74.5 dBFS(55 MHz频段、最高90 MHz、250 MSPS)

- SNR:72.0 dBFS(82 MHz频段、最高90 MHz、250 MSPS)

- NSR禁用时的性能

- SNR:66.2 dBFS(最高90 MHz、250 MSPS)

- SFDR:85 dBc(最高185 MHz、250 MSPS)

- 总功耗:706 mW (200 MSPS)

- 1.8 V电源电压

- LVDS(ANSI-644电平)输出

- 1至8整数输入时钟分频器(最大输入频率625 MHz)

- ADC内部基准电压源

- 灵活的模拟输入范围

- 1.4 V p-p至2.0 V p-p(标称值1.75 V p-p)

- 差分模拟输入、400 MHz带宽

- 95 dB通道隔离/串扰

- 串行端口控制

- 节能的关断模式

框图

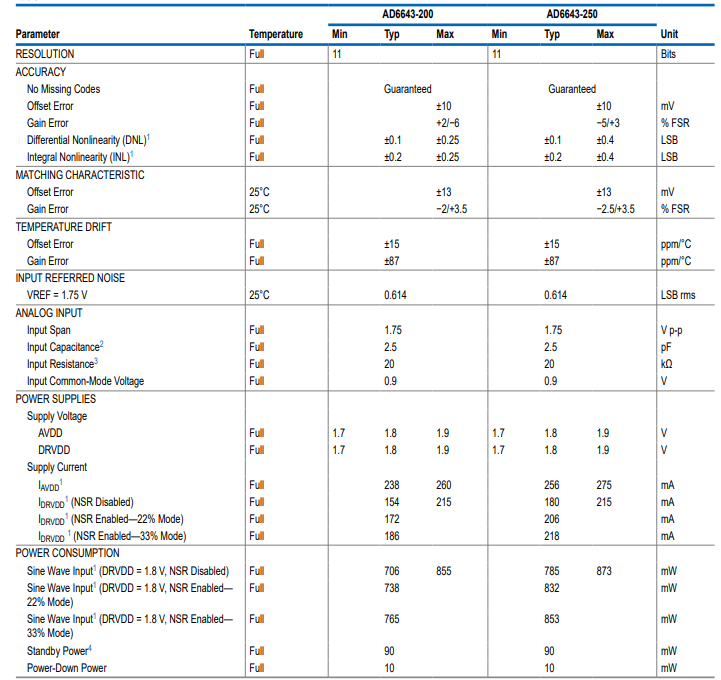

ADC DC规格

时序图

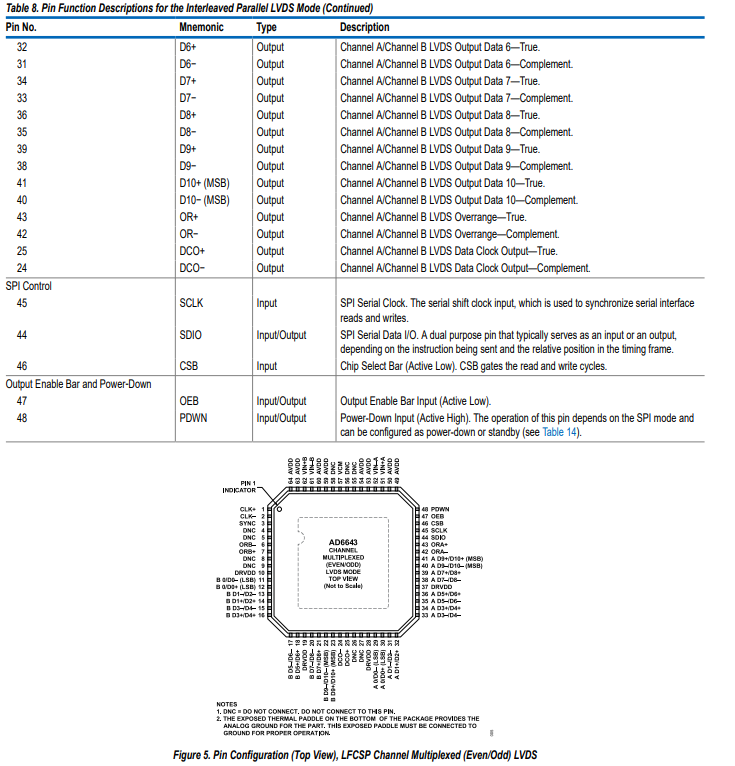

引脚配置描述

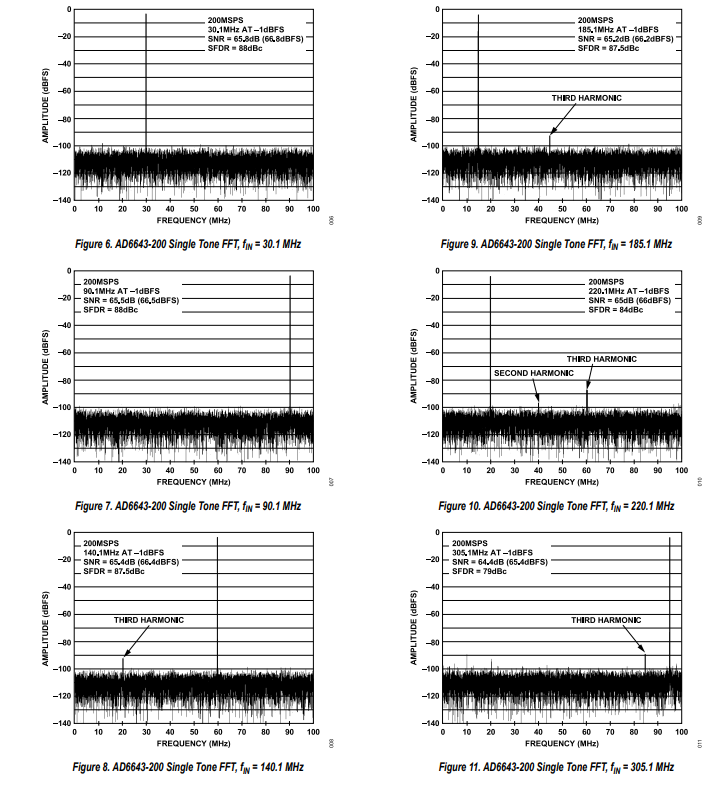

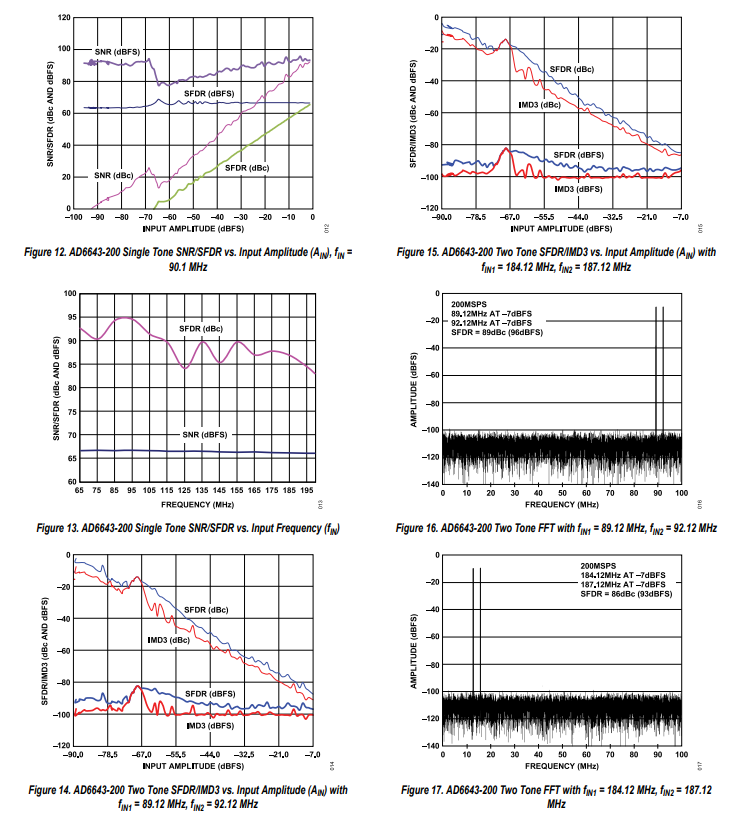

典型性能特征

典型性能特征

AD6643有两个模拟输入通道和两个数字输出通道。中间频率(IF)信号在呈现于输出端口之前,会经过多个处理阶段。

ADC架构

AD6643架构由双前端采样保持电路组成,其后连接流水线开关电容ADC。每个阶段的量化输出先进行合并,再得到最终的11位数字校正逻辑结果。或者,这11位结果在送入数字校正逻辑之前,可先通过NSR模块进行处理。

流水线架构使第一级能够基于新的输入样本运行,并让其余各级对前一个样本进行处理,在时钟上升沿进行采样。

流水线的每一级(最后一级除外)均由一个低分辨率闪存ADC、一个数模转换器(DAC)以及一个积分误差放大器(MDAC)组成。MDAC对DAC输出与下一级流水线中闪存输入的差值进行放大。每一级中都有一位冗余,用于校正闪存误差。最后一级仅由一个闪存ADC组成。

每个通道的输入级包含一个差分采样电路,可实现交流耦合或单端模式。输出数据锁存模块会阻塞数据、校正误差,并将数据输出到外部缓冲器。输出缓冲器由独立电源供电,在掉电期间,输出缓冲器进入高阻态。

AD6643双接收器可同时对两个通道进行数字化处理,用于支持通信系统中多样性接收和数字预失真(DPD)观测路径。

双中频接收器设计可用于处理同一载波上的不同接收信号,也可使用不同的天线处理不同的载波信号。ADC也可使用不同的天线,在直流至300 MHz的频率范围内对输入进行带通滤波,以最小的性能损失对400 MHz的模拟输入进行滤波。不过,这样做会增加ADC的噪声和失真。

它具备同步功能,可实现多个通道或多个器件之间的定时同步。通过一个三线制、SPI兼容的串行接口对AD6643进行编程和控制。

模拟输入注意事项

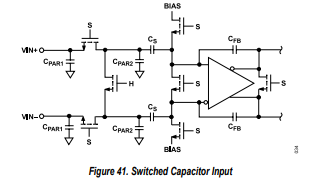

AD6643的模拟输入采用差分开关电容电路,针对差分输入信号处理进行了优化。

时钟信号交替切换输入电路,使其在采样模式和保持模式间转换(见图41)。处于采样模式时,信号源必须能够在半个时钟周期内完成对采样电容的充电以及设置。

每个输入端串联一个小电阻,有助于降低驱动源输出级所需的峰值瞬态电流。可在输入端之间并联一个旁路电容,为动态充电电流提供通路。这种无源网络会在ADC输入端形成一个低通滤波器,因此,具体数值取决于应用场景。

为实现最佳动态性能,需匹配驱动VIN+和VIN - 引脚的源阻抗,并使输入差分平衡。

输入共模

AD6643的模拟输入内部无直流偏置。在交流耦合应用中,用户必须从外部提供此偏置。将器件设置为VCM = 0.5 × AVDD(或0.9 V)可实现最佳性能。

芯片设计中集成了片上共模电压基准,可通过VCM引脚获取。建议使用VCM输出来设置输入共模。

模拟输入的最佳共模电压由VCM引脚电压(通常为0.5 × AVDD)设定。VCM引脚必须通过0.1 μF电容接地,具体内容见应用信息部分。将此去耦电容放置在靠近引脚处,可缩短电阻和电感回路,从而改善性能。

-

接收机

+关注

关注

9文章

1225浏览量

54876 -

IF

+关注

关注

1文章

64浏览量

27233 -

ADC

+关注

关注

0文章

217浏览量

16845 -

NSR

+关注

关注

0文章

5浏览量

1551

发布评论请先 登录

AD6659混合信号双通道中频接收机

高性能、双通道IF采样接收机

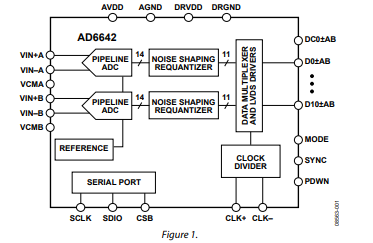

80MHz带宽双通道中频接收机

AD6643 双通道中频接收机

CN0140 高性能、双通道IF采样接收机

AD6642双通道中频接收机技术手册

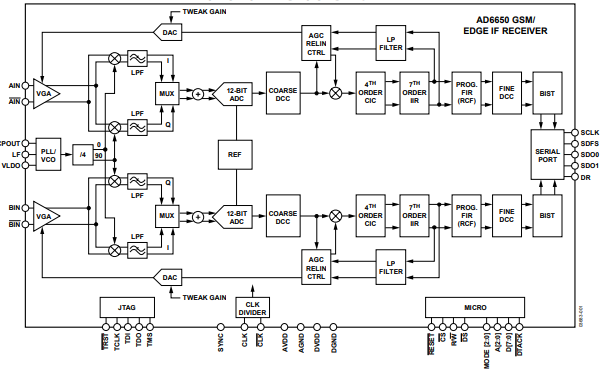

AD6650分集中频至基带GSM/EDGE窄带接收机技术手册

AD6643双通道中频接收机技术手册

AD6643双通道中频接收机技术手册

评论