概述

AD8331/AD8332/AD8334分别为单通道、双通道和四通道超低频噪声可变增益放大器(VGA)。它们针对线性度进行了优化,在高达120 MHz的频率下可用作低噪声可变增益元件。

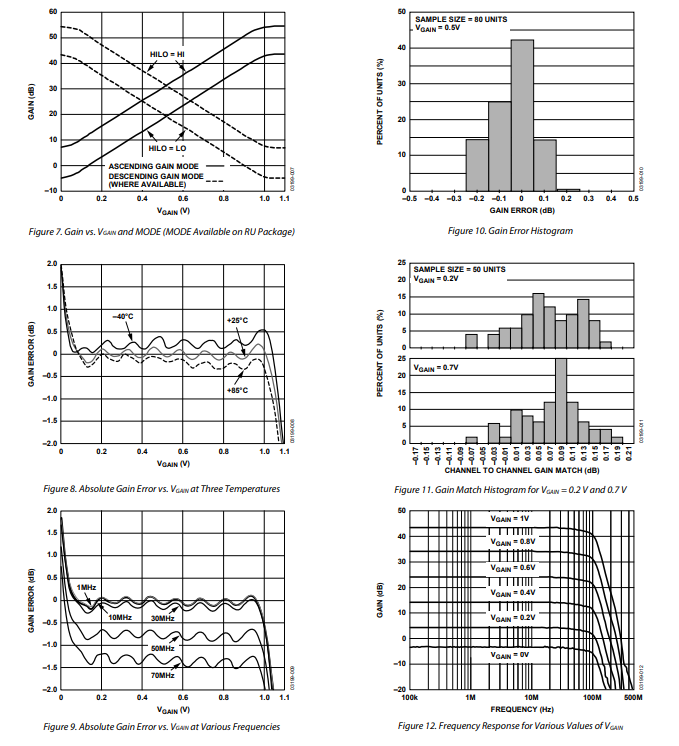

48 dB的增益范围使这些器件适用于各种应用。卓越的宽带平坦度在整个增益范围内都能保持。90 dB/V的增益控制斜率可实现线性的dB标度增益控制,电压范围为40 mV至1 V。工厂微调可确保出色的部分对部分以及通道对通道的增益匹配。

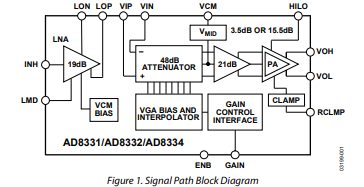

各通道内置一个超低噪声前置放大器(LNA)、一个48 dB增益范围的X-AMP? VGA以及一个具有可调输出限制功能的可选增益后置放大器。LNA增益为19 dB,具有单端输入和差分输出。LNA输入阻抗可以利用一个电阻来调节,以便与信号源相匹配,且不影响噪声性能。

VGA的48 dB增益范围使这些器件适合各种不同的应用。带宽在整个增益范围内可保持出色的一致性。对于40 mV至1 V范围内的控制电压,增益控制接口可提供精确的50 dB/V线性dB调整。通过工厂调整可确保器件间及通道间具有出色的增益匹配特性。差分信号路径提供出色的二次和三次失真性能及低串扰。

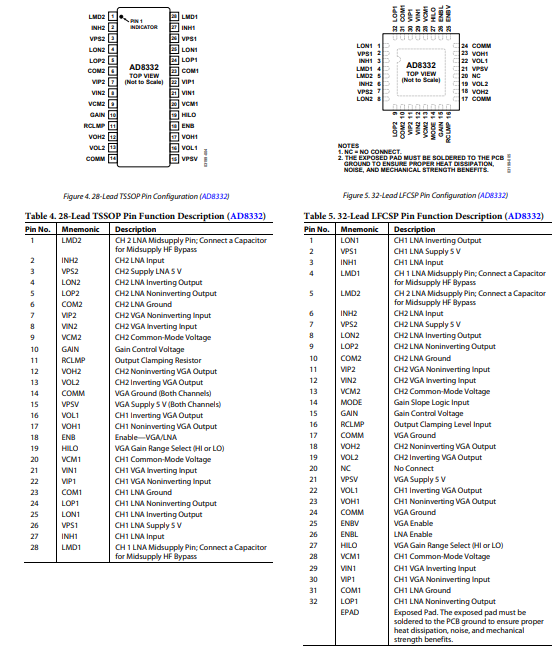

AD8332的工作温度范围为-40℃至+85℃,采用28引脚TSSOP和32引脚LFCSP两种封装。

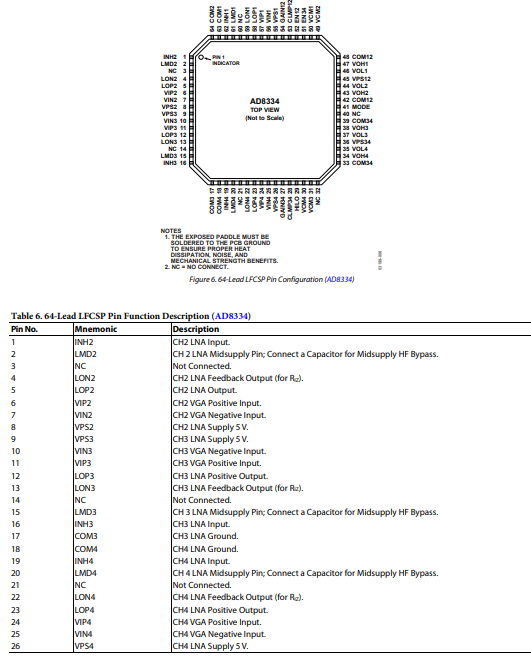

AD8332为双通道版本,AD8331为单通道版本,AD8334为四通道版本。

数据表:*附件:AD8331 AD8332 AD8334内置超低噪声前置放大器和可编程输入阻抗(RIN)的双通道VGA技术手册.pdf

应用

特性

- 超低噪声前置放大器

电压噪声 = 0.74 nV/√Hz

电流噪声 = 2.5 pA/√Hz - 3 dB带宽: 100 MHz

- 低功耗: 每通道145 mW

- 宽增益范围,内置可编程后置放大器

-4.5 dB至+43.5 dB

+7.5 dB至+55.5 dB - 低输出参考噪声

48 nV/√Hz典型值 - 有源输入阻抗匹配

- 针对10位/12位ADC优化

- 可选的输出箝位电平

- 采用5 V单电源供电

- 采用引脚架构芯片级封装

功能框图

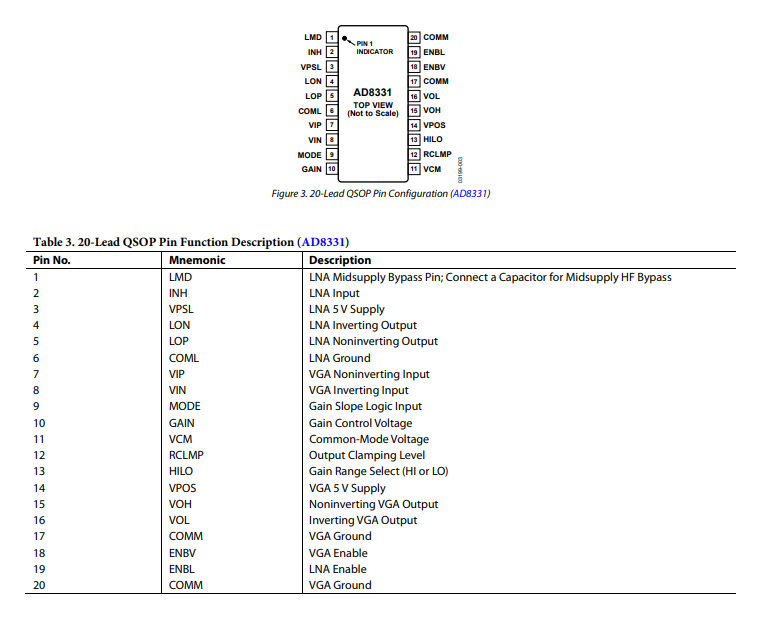

引脚配置描述

典型性能特征

应用信息

低噪声放大器(LNA)——外部组件

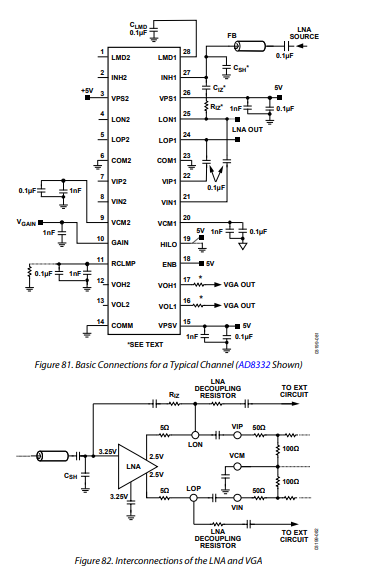

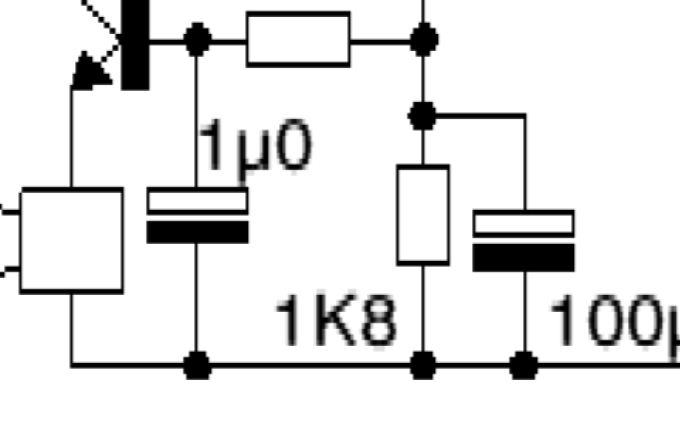

LMD引脚(连接到偏置电路)必须通过接地进行旁路,并且信号源应通过电容耦合到LNA引脚,该电容值在0.1μF至2.2μF之间(见图81)。

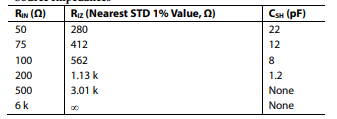

LNA的未端接输入阻抗为6 kΩ。用户可以根据公式6合成50Ω至6 kΩ之间的任何LNA输入电阻,或者从表7中选择。

表7. 常见源阻抗的LNA外部组件值

当使用有源输入端接时,需要一个去耦电容(C_{ST})来隔离LNA的输入和输出偏置电压。

并联输入电容**C_{ST}**会在较高频率下降低增益峰值,此时增益滚降是由于LNA在高频下的增益滚降造成的。**C_{ST}的值在R_{EQ}**增加到500Ω时减小,在该点不需要电容。对于50Ω≤R_{IN}≤200Ω,**C_{ST}**的建议值见表7。

当无法避免LNA引脚INH的长走线时,或者如果两个LNA输出都驱动外部电路,在引脚INH的信号线上串联一个小型铁氧体磁珠(FB)会很有用,它可以抑制噪声。该磁珠在100 MHz时为75Ω(村田BLM21或等效产品)。图82显示了LNA输出的互连细节。

LNA输出与VGA输入之间需要电容耦合。由于5Ω的输出电阻,需要考虑LNA输出和VGA输入之间的直流电平差异以及电容值的影响。建议电容值为0.1μF。LNA输出端与VGA输入端之间存在0.4 dB的损耗。在LNP和LNN输出端增加额外负载会影响LNA增益。

LNA的两个输出均可用于驱动外部电路。当需要单端LNA输出时,应使用引脚LOP。用户应注意LNA输出的杂散电容负载,特别是LON。LNA可以在10 pF的并联电容下驱动100Ω负载。如果LNA输出连接到远程印刷电路板,添加一个4.99Ω的串联电阻或在100 MHz时为75Ω的铁氧体磁珠可以防止振荡。

增益输入

AD8332的两个通道共用GAIN引脚。其输入阻抗标称值为1 MΩ,建议使用100 pF至1 nF的旁路电容。

并联设备可由一个公共电压源或DAC驱动。考虑到驱动波形的带宽要求,需利用总分布电容进行解耦。

在LO增益模式下,增益控制噪声成为一个因素,主要是≤15 nV/√Hz。在GAIN引脚内部,噪声增益约为15 nV/√Hz。在HI增益模式下,增益控制噪声可忽略不计。

共模电压输入(VCM)

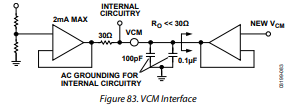

VCM引脚、VOL引脚和VOH引脚的共模电压默认值为2.5 V直流。在交流耦合应用中,VCM引脚未端接,但仍需在靠近差分电路的位置进行交流接地旁路。VGA输出可为ADC提供直流接地,这样ADC的共模输出电压可通过在VCM引脚施加1.5 V至3.5 V来设置。在直流耦合操作中,当VCM引脚由单独的电源供电时,不建议这样做。

VCM引脚上的电压由一个具有30 Ω输出阻抗和±2 mA默认输出电流的片内缓冲器提供(见图83)。如果VCM引脚由外部电源供电,其输出阻抗应远小于30 Ω,且其电流驱动能力应大于2 mA。如果多个设备并联连接,外部缓冲器应能够共同吸收总输出电流。当使用2.5 V以外的共模电压时,需要一个限压电阻**R_{LIMIT}**来防止过压。

逻辑输入——使能(ENB)、模式(MODE)和高低增益选择(HILO)

所有使能引脚的输入阻抗标称值为25 kΩ,可上拉至5 V(推荐使用上拉电阻),也可由3 V或5 V逻辑电平驱动。使能引脚在电源断电时为低电平,VGA输出电压接近地电位。多个设备可由一个公共源驱动。有关功能控制的更多信息,请参考表3、表4、表5和表6。

HILO引脚可与3 V或5 V CMOS逻辑电平兼容。它可以接地或上拉至5 V,具体取决于所需的增益范围和输出噪声。

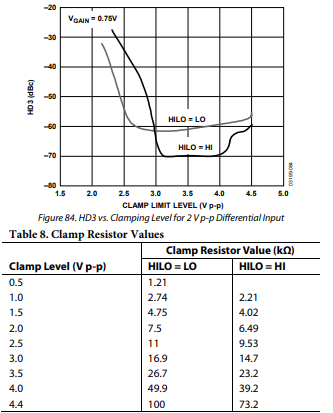

可选输出电压限制

RCLMP引脚为用户提供了一种在过载情况下限制输出电压摆幅的方法。峰值到峰值限制电压通过与地连接的电阻进行调整(见表8中的多个调整电压和对应电阻值)。未连接时,默认限制电平为4.5 V峰峰值。请注意,三次谐波失真会随着波形削波而增加。为实现最低失真,对于1 V峰峰值输入摆幅的转换器,箝位电平应设置为1.5 V峰峰值;对于2 V峰峰值输入摆幅,设置为2.7 V峰峰值;对于0.5 V峰峰值输入摆幅,设置为1 V峰峰值。最佳设置需通过实验确定。图84显示了在2 V峰峰值差分输入信号下,二次谐波失真与2增益模式下限制电平的函数关系。在HI增益模式下,更宽的限制电平是可取的。

输出解耦

当驱动电容大于约10 pF的负载,或在其他电路板上有长电路连接时,添加电阻和/或铁氧体磁珠组成的输出网络有助于确保稳定性。可以加入如81图所示的奈奎斯特滤波器等组件。在评估板中,该电阻值为84.5 Ω。例如,在应用中使用120 nH磁珠时,可将该电阻与低阻值电阻并联,以尽量减少负载变化。

-

增益放大器

+关注

关注

2文章

153浏览量

29714 -

VGA

+关注

关注

5文章

572浏览量

64877 -

AD8331

+关注

关注

0文章

3浏览量

7837

发布评论请先 登录

放大器,低噪声前置放大器参数,前置放大器厂家

AD8331前置放大器反馈电阻Riz的阻值匹配所有的Riz吗?

AD8331/AD8332/AD8334,pdf datas

低噪声前置放大器电路的设计步骤

AD8332 内置超低噪声前置放大器和可编程输入阻抗(RIN)的双通道VGA

AD8334 内置超低噪声前置放大器和可编程输入电阻(RIN)的四通道VGA

AD8331 内置超低噪声前置放大器和可编程输入阻抗(RIN)的单通道VGA

AD8331/AD8332/AD8334:带前置放大器和可编程输入电阻(R<sub>IN</sub>)的超低噪声VGA

AD8332-EVALZ:双VGA、超低噪声前置放大器和可编程RIN评估板数据表

AD8331/AD8332/AD8334内置超低噪声前置放大器和可编程输入阻抗(RIN)的双通道VGA技术手册

AD8331/AD8332/AD8334内置超低噪声前置放大器和可编程输入阻抗(RIN)的双通道VGA技术手册

评论