概述

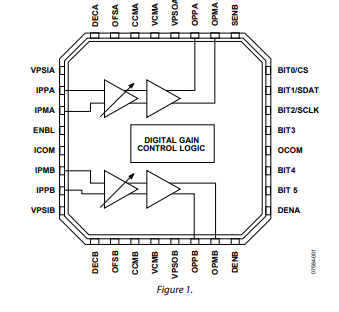

AD8372是一款双通道、数字控制、可变增益放大器,能提供精密的增益控制、高IP3与低噪声系数。出众的低失真性能与宽信号带宽使得AD8372非常适合多通道接收机应用。

数据表:*附件:AD8372 41dB增益范围、1 dB步长、可编程双通道VGA技术手册.pdf

对于宽动态范围应用而言,AD8372能提供41dB的宽增益范围。其增益可以通过4引脚、双向串行端口进行编程。每通道串行接口包括时钟、闩锁、数据输入线和数据输出线。

AD8372利用一个外部电阻提供设置输出级跨导能力。RXT1与RXT2引脚通常通过一个2.0 kΩ的电阻接地,将最大增益额定值设置为31 dB。调整电流设置电阻,可以控制每个通道的增益和失真性能。这个灵活特性可用于功耗与失真性能折中的应用。

AD8372利用ENB1、ENB2引脚的适当逻辑电平供电。在省电模式下,AD8372待机电流不足2.6 mA,提供出色的输入-输出隔离。省电模式下保持增益设置。

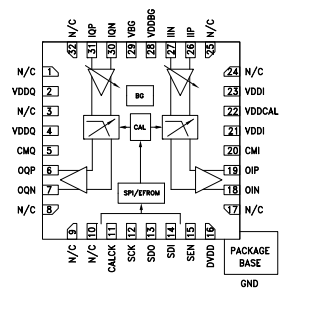

AD8372采用ADI公司的高频BiCMOS工艺制作,具有精密增益控制调节能力和低失真性能。AD8372每通道的静态电流通常为106 mA。AD8372放大器采用紧凑的、散热增强型5 mm × 5 mm 32引脚LFCSP封装,工作温度范围是:–40°C ~ +85°C 。

应用

特性

- 独立的双通道数字控制VGA

- 差分输入和输出

- 150 Ω差分输入

- 开集差分输出

- 7.8 dB噪声指数至100 MHz(最大增益时)

- HD2/HD3优于77 dBc(1 V峰峰值差分输出)

- ?3 dB带宽:130 MHz

- 41 dB增益范围

- 1 dB步长±0.2 dB

- 串行8位双向SPI控制接口

- 宽输入动态范围

- 引脚可编程输出级

- 关断特性

- 5 V单电源:每通道106 mA

- 32引脚LFCSP、5 mm × 5 mm封装

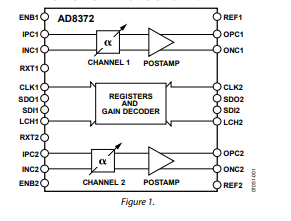

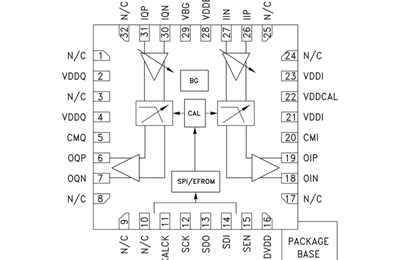

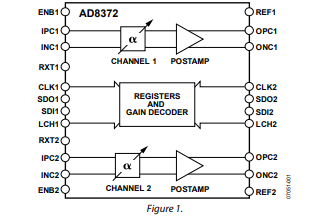

框图

串行控制接口时序

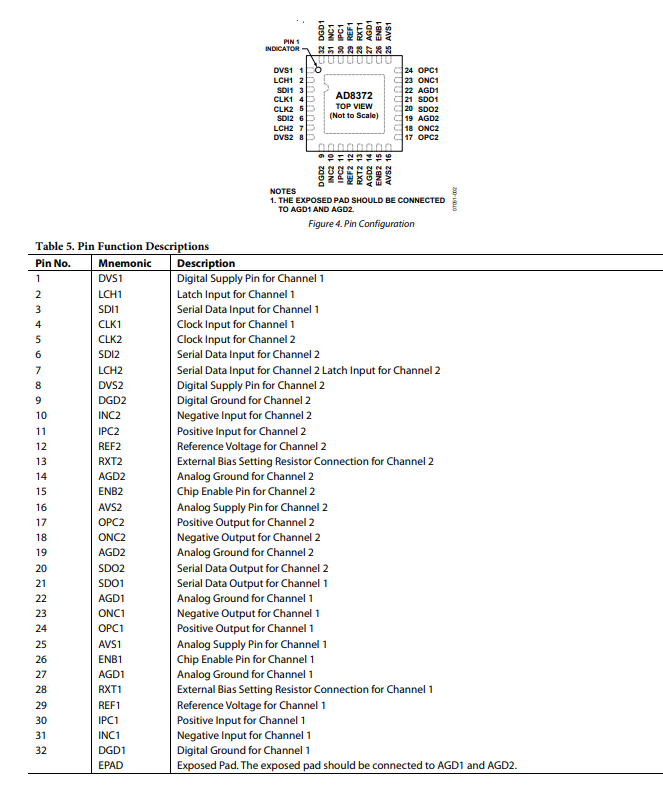

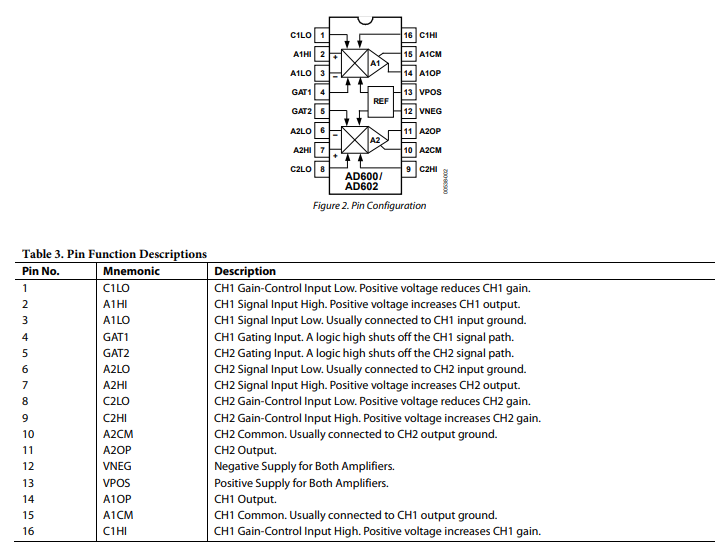

引脚配置描述

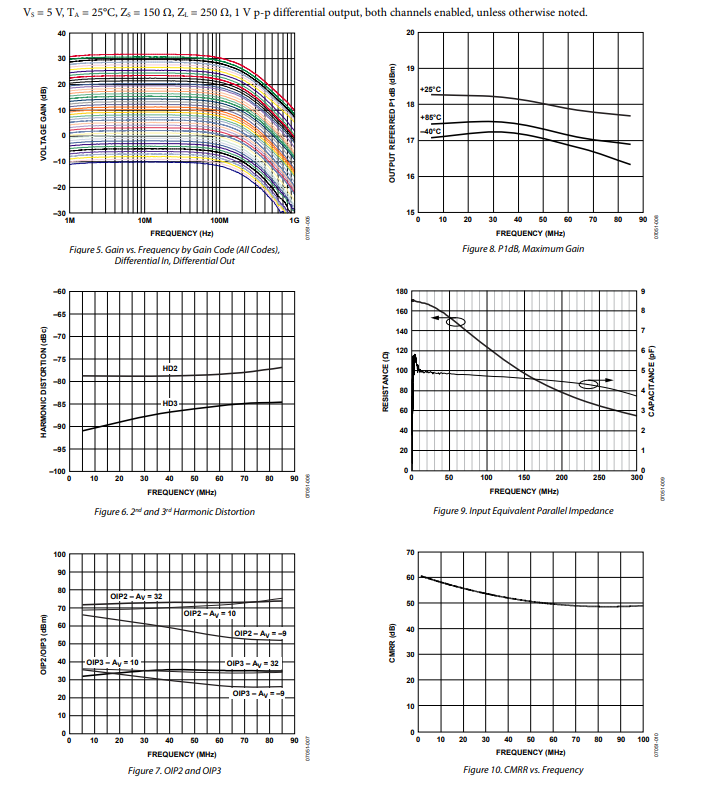

典型性能特征

AD8372是一款双路差分可变增益放大器。每个放大器由一个150Ω的数字控制6dB衰减器、一个1dB微调器以及一个固定增益跨导放大器组成。

每个放大器的差分输出由一对集电极开路输出晶体管组成。其偏置电压为+5V,采用高价值电感。33μH电感器(如Coilcraft 1812LS - 333XL )是该组件的理想选择。应在差分输出两端连接一个250Ω的电阻,以提供电流 - 电压转换,并作为无源滤波的源阻抗,用于AD8372之后的电路。

AD8372的增益基于250Ω的差分负载,根据以下公式随负载电阻变化:

- 电压增益:Gain = RL(负载电阻)/250

- 功率增益:Gain = 10log(RL/250)

增益对负载的依赖性源于集电极开路输出级,该级由外部电感偏置。电感的串联扼流圈和电阻决定了放大器的低频极点。高频极点由寄生电容以及与输出电阻并联的电容决定。每侧总输出电流为106mA,其中组合输出电流为70mA,电源引脚电流约为36mA。该电路有一个接地外部电阻(Rext),用于设置跨导级的输出阻抗。为实现最佳失真效果,建议每侧的Rext值为106mA。使Rext值约为2.0kΩ。每个输出端的参考引脚使用2.4V参考电压,并且在输入端使用0.1μF电容对该共模电压进行去耦。通过设置ENB引脚的电平可使器件功耗小于2.6mA。

AD8372的最大增益时噪声系数为7.8dB,随着增益降低而增加。噪声系数的增加量等于增益的减小量。

在输出端测量的增益线性度为一阶,与测量的相位无关。

布局设计应考虑通过在扼流圈下方铺设接地层来尽量减少输出电容,并通过走线均衡来实现相位平衡。

单端和差分信号

AD8372设计用于施加差分信号作为输入,并利用器件的差分输出驱动来实现出色的信号失真性能。信号失真性能的改善主要归因于使用差分信号技术来消除器件中的各种失真分量。此外,所有特性均采用差分信号路径进行表征。若将该器件的输入或输出用作单端信号,会显著降低AD8372的整体性能。

无源滤波技术

AD8372具有100Ω的差分输入阻抗。为实现最佳性能,差分输出负载应为250Ω。在设计AD8372的无源滤波器时,必须考虑这些阻抗。

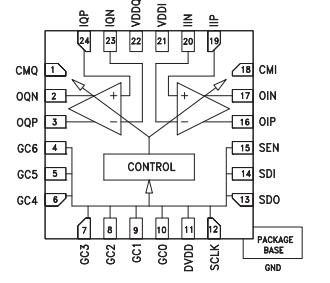

数字增益控制

数字增益控制接口由以下引脚组成:SDI、SDO、CLK和LATCH。当LATCH引脚为低电平时,该接口处于活动状态。增益字从AD8372的SDI引脚写入,并读回到SDO引脚。写入或读取模式下的第一个时钟输入数据引脚决定接口是写入模式还是读取模式。该位是一个无关位,而其余六位对编程增益起作用。在读取模式下,SDO引脚输出6位增益字,从最低有效位(LSB)到最高有效位(MSB)。增益可在 - 9dB至32dB之间以1dB为步长进行编程。图2和图3给出了增益定时的详细信息,表2给出了增益码。

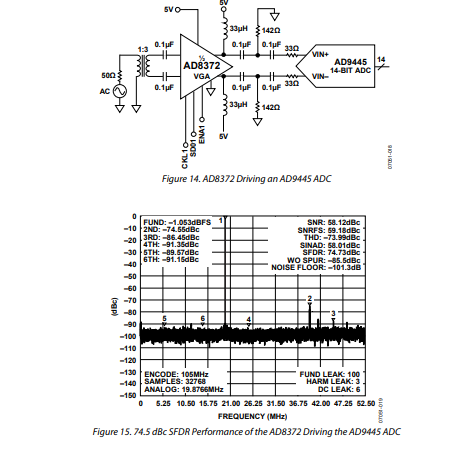

驱动模数转换器

AD8372旨在驱动高速、高动态范围的模数转换器(ADC)。图14所示的电路代表了AD8372双路可变增益放大器(VGA)驱动AD9445 14位、125MSPS ADC的简化端到端示意图。AD8372的输入进行交流耦合,使用1:3阻抗变压器,该变压器还将150Ω输入电阻与50Ω源匹配。集电极开路输出通过33μH电感器偏置,并与ADC的142Ω负载电阻交流耦合,在2kΩ输入电阻处并联,从而为增益精度提供250Ω负载。

ADC通过142Ω电阻进行交流耦合,以消除AD9445共模电压的直流影响。在33Ω电阻上串联连接可改善AD8372与ADC输入采样的隔离,并满足AD9445对2kΩ差分负载和2V p-p信号(VREF = 1V时为满量程输出)的要求。该电路提供可变增益、隔离以及与AD9445的源匹配。使用此电路,在85MHz时,AD8372增益为32dB(最大增益)时,可实现74.5dBc的无杂散动态范围(SFDR)性能(见图15)。

-

放大器

+关注

关注

145文章

14159浏览量

218259 -

增益放大器

+关注

关注

2文章

153浏览量

29714

发布评论请先 登录

通用双通道数字控制可变增益放大器AD8372电子资料

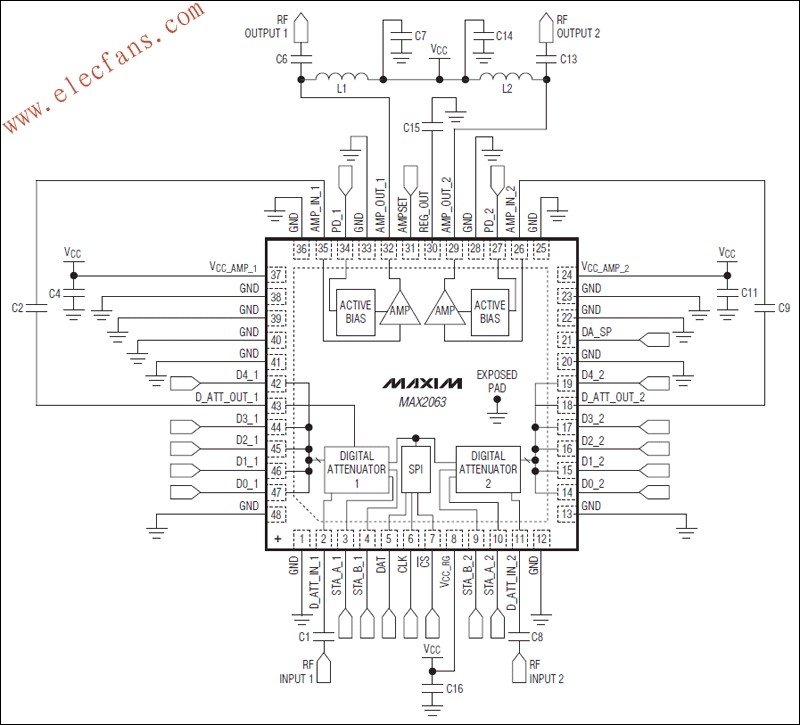

MAX2063双通道数字调节可变增益放大器(VGA)

AD8372 41dB增益范围、1 dB步长、可编程双通道VGA

AD8372:41 db range,1 dB蒸发器,程序双VGA数据Sheet

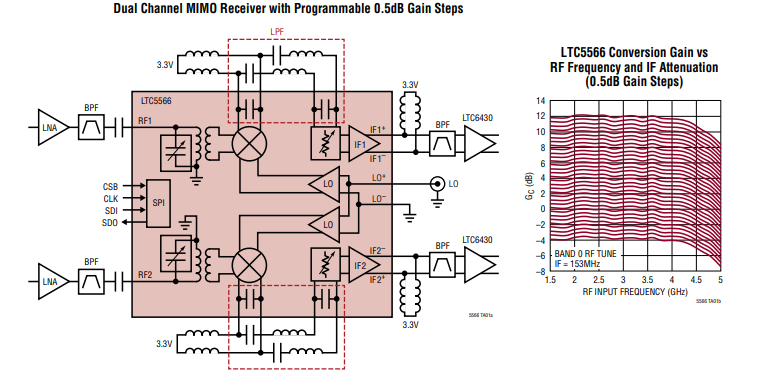

LTC5556 1.5GHz至7GHz双路可编程增益下变频混频器技术手册

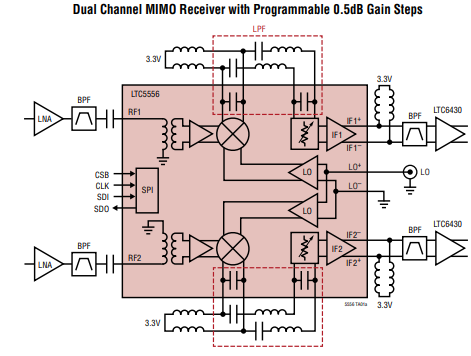

LTC5566 300MHz至6GHz双通道可编程增益下变频混频器技术手册

AD600/AD602双通道、低噪声、宽带可变增益放大器(增益范围0dB至+40dB)技术手册

AD8372 41dB增益范围、1 dB步长、可编程双通道VGA技术手册

AD8372 41dB增益范围、1 dB步长、可编程双通道VGA技术手册

评论