概述

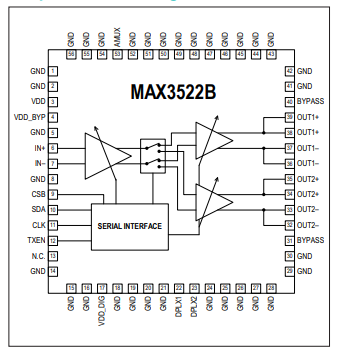

MAX3523是一款超越DOCSIS 3.1上游发射要求的可编程增益放大器(PGA)。PGA满足DOCSIS 3.1杂散限制,同时在5MHz至204MHz的射频带宽范围内发射68dBmV的组合输出功率。增益使用SPI 3线接口在60dB的范围内进行控制,以1dB为步长。该器件采用Maxim的高压CMOS工艺,能够提供高动态范围,同时充分降低+5V电源轨下的功耗。

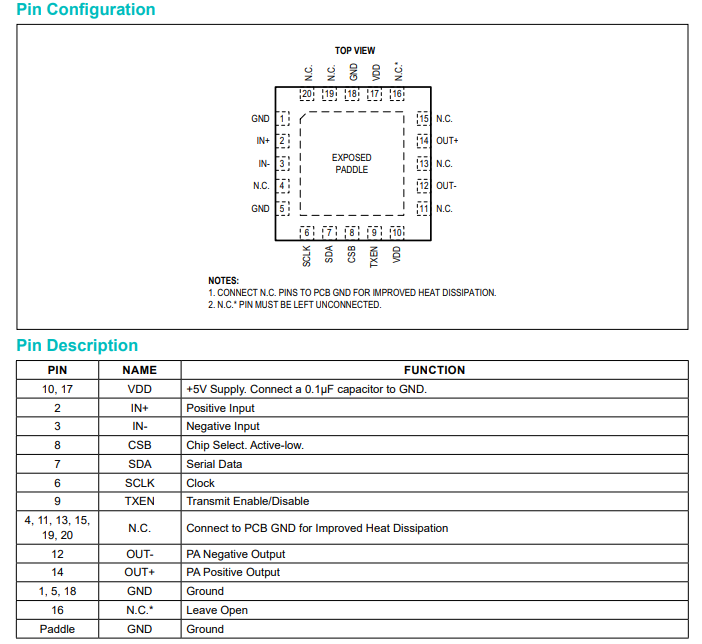

MAX3523采用20引脚5mm x 5mm x 0.75mm TQFN封装,工作温度范围为0°C至+70°C。

数据表:*附件:MAX3523低功耗DOCSIS 3.1可编程增益放大器技术手册.pdf

应用

- 电缆调制解调器(CM)

- 用户端设备(CPE)

- DOCSIS 3.1上游(D3.1 US)

特性

- 在符合DOCSIS 3.1要求的同时提供 +68dBmV输出功率

- 输出带宽范围:5MHz–204MHz

- 使用5V电源电压时的功耗为3.5W

- 可编程电源代码实现低功耗操作

- 在调制解调器输出为+65dBmV时超越了OFDM满载分配的杂散要求

- 采用带裸露焊盘的20L 5mm x 5mm x 0.75mm TQFN封装

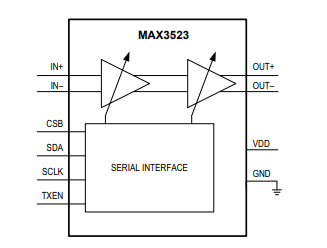

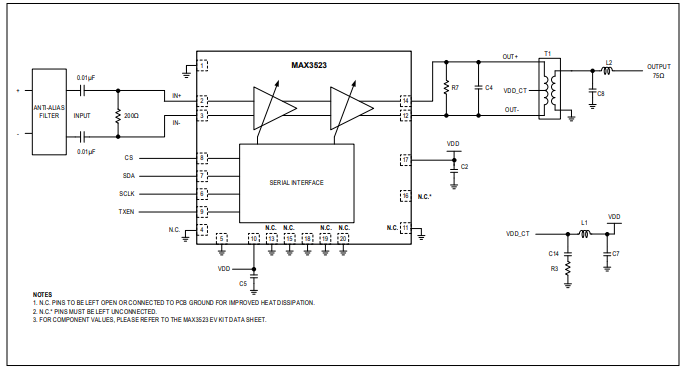

简化框图

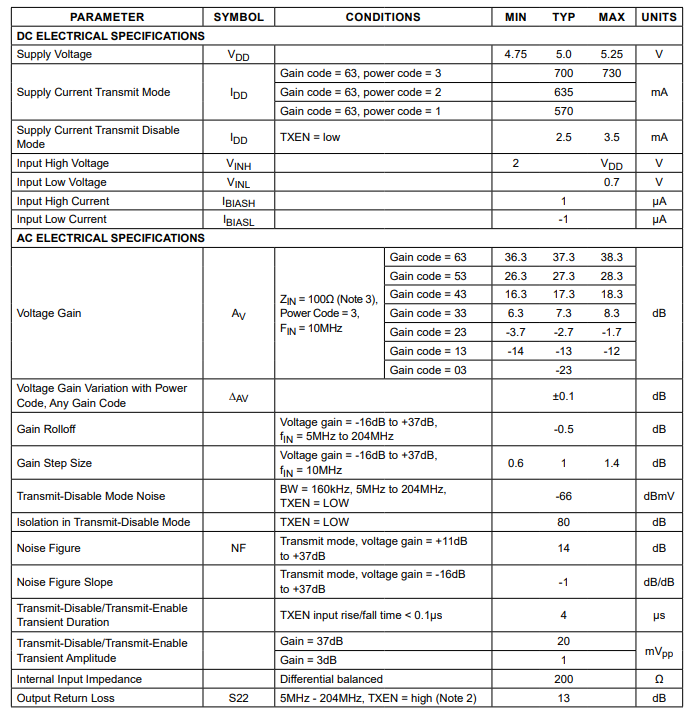

电特性

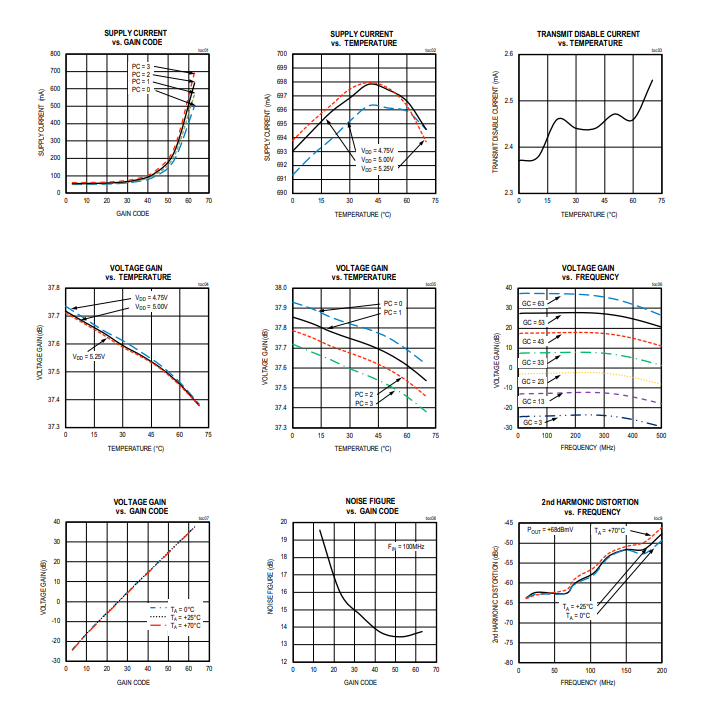

典型操作特性

引脚配置描述

应用电路

应用信息

电源编码

该器件的设计旨在满足DOCSIS 3.1的严格线性度要求(功率码3 )。使用较低的电源编码(PC = 2、1或0 )可降低器件的工作电流。全量程增益编码之间的增益差异通常小于0.1dB。

发射禁用模式

在DOCSIS系统中,通过将TXEN置低,可使MAX3523进入发射禁用模式。在满足DOCSIS 3.1要求的情况下,应在发送之前将TXEN保持低电平。

如果需要更改增益码或电源编码,新的PC或GC码值应在发射禁用(TXEN低 )时进行时钟控制。MAX3523应在SCLK的第12个上升沿设置新的工作点。此操作应在传输突发之间完成。

输出电路

输出电路是一个漏极开路差分放大器。输出应进行电阻端接,如典型应用电路所示。应使用50Ω - 75Ω的射频变压器作为器件差分输出与非平衡75Ω负载之间的接口。

放大器的性能取决于端接电阻的值。使用典型应用电路中所示的R7端接电阻可获得额定性能。增加该电阻的值会提高增益并改善信噪比,但会增加输出回波损耗。

变压器的初级电感可能会随温度变化。应提供足够的初级电感,以确保在温度变化时仍能保持宽带输出能力。

输入电路

MAX3523的差分输入阻抗为200Ω。但在典型应用中,由于需要100Ω差分源匹配,因此需使用一个200Ω匹配电阻,如典型应用电路所示。

该器件具有足够的增益和线性度,当输入信号为+31dBmV时,可产生+68dBmV的输出电平。如果使用高于+31dBmV的输入电平,可能会导致三阶互调失真产物增大。

布局问题

精心设计的印刷电路板(PCB)是射频电路的关键部分。为实现最佳性能,需关注电源供应布局问题以及输出电路布局。MAX3523评估版(EV)电路板可用作PCB设计的参考指南。其电气性能经过了全面测试,是优秀的参考资料。有关更多信息,请参考MAX3523评估套件。

输出电路布局

尽可能缩短输出走线长度。器件与变压器之间的串联电感会在较高的工作频率范围内降低性能。为保持输出网络的平衡,请使差分走线的长度尽可能匹配。

电源供应布局

为使器件不同部分之间的耦合最小化,理想的电源供应布局是星形配置。这种配置在电源分支节点处有一个大容值的去耦电容。电源供应走线从该节点出发,分别连接到电路的各个部分。在每条走线的末端放置一个去耦电容,以提供非常低的阻抗。这种布局可在每个电源引脚处实现本地电源去耦。电源走线必须能够承载最大电流,且不会产生明显的电压降。

外露焊盘热特性考量

MAX3523的20引脚TQFN封装的外露焊盘(EP)为芯片提供了低热阻路径。重要的是,印刷电路板的设计应使器件安装在与该低热阻路径有热接触的位置。如有必要,应提供一个低电感的接地路径。MAX3523评估板就是一个在热性能和电气性能方面都能提供最佳效果的示例。

-

pga

+关注

关注

1文章

107浏览量

42022 -

DOCSIS

+关注

关注

0文章

15浏览量

8677 -

可编程增益放大器

+关注

关注

0文章

19浏览量

7753

发布评论请先 登录

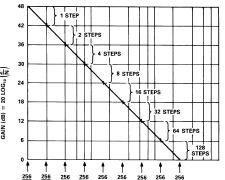

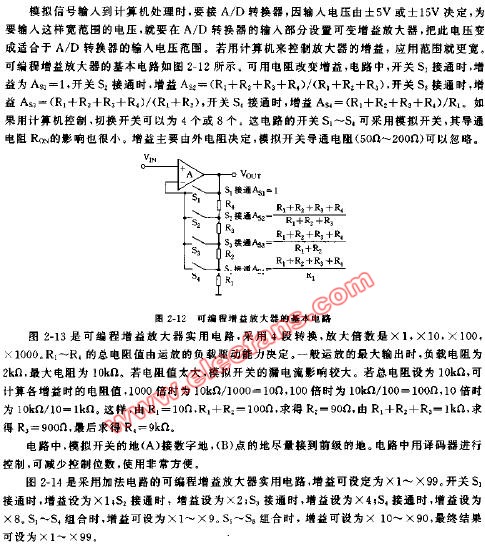

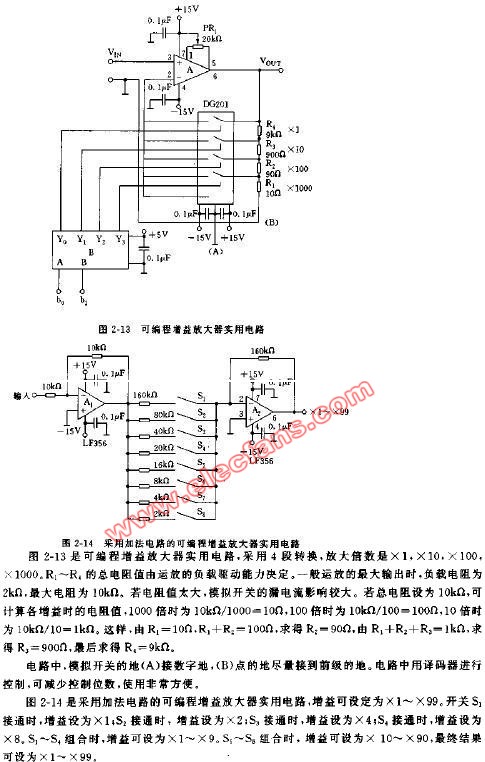

低功耗数字可编程增益放大器参考设计

UG-1443:评估ADA4254零漂移、高电压、低功耗、可编程增益仪表放大器

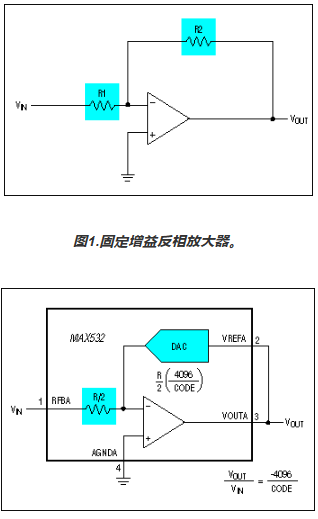

可编程增益放大器,使用MAX532 DAC

MAX3523低功耗DOCSIS 3.1可编程增益放大器技术手册

MAX3523低功耗DOCSIS 3.1可编程增益放大器技术手册

评论